Page History

Template Revision 2.6 - on construction

...

| HTML |

|---|

<!-- tables have all same width (web max 1200px and pdf full page(640px), flexible width or fix width on menu for single column can be used as before) -->

<style>

.wrapped{

width: 100% !important;

max-width: 1200px !important;

}

</style> |

...

| hidden | true |

|---|---|

| id | Comments |

Important General Note:

...

Export PDF to download, if vivado revision is changed!

Designate all graphics and pictures with a number and a description, Use "Scroll Title" macro

...

Figure template (note: inner scroll ignore/only only with drawIO object):

...

| anchor | Figure_xyz |

|---|---|

| title | Text |

| Scroll Ignore |

|---|

Create DrawIO object here: Attention if you copy from other page, use |

| Scroll Only |

|---|

image link to the generate DrawIO PNG file of this page. This is a workaround until scroll pdf export bug is fixed |

...

Table template:

- Layout macro can be use for landscape of large tables

- Set column width manually(can be used for small tables to fit over whole page) or leave empty (automatically)

...

| anchor | Table_xyz |

|---|---|

| title | Text |

...

| Scroll pdf ignore | ||||

|---|---|---|---|---|

Table of contents

|

Overview

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

Zynq PS Design with DDR Less FSBL Example.

Refer to http://trenz.org/te0722-info for the current online version of this manual and other available documentation.

Key Features

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

| Excerpt |

|---|

|

Revision History

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

...

| anchor | Table_DRH |

|---|---|

| title | Design Revision History |

...

- split FSBL into 2 templates, one with and one without Sensor+LED access example app

...

- TE Script update

- rework of the FSBLs

- DDR LESS, Device ID, Sensor+LED access

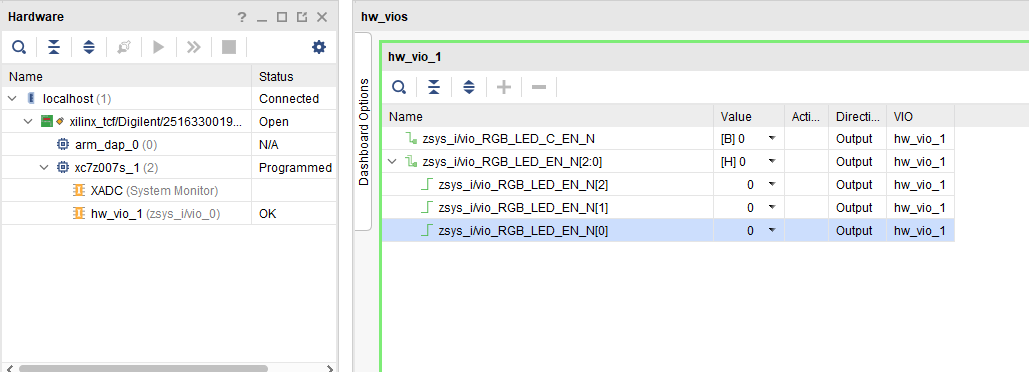

- VIO for RGB access

...

- initial release

Release Notes and Know Issues

...

...

...

...

Hardware

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

Basic description of TE Board Part Files is available on TE Board Part Files.

Complete List is available on <design name>/board_files/*_board_files.csv

Design supports following modules:

...

| anchor | Table_HWM |

|---|---|

| title | Hardware Modules |

...

...

Requirements

Software

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

...

| anchor | Table_SW |

|---|---|

| title | Software |

...

...

Design supports following carriers:

...

| anchor | Table_HWC |

|---|---|

| title | Hardware Carrier |

...

...

...

...

...

Additional HW Requirements:

...

| anchor | Table_AHW |

|---|---|

| title | Additional Hardware |

...

for JTAG, UART

...

Content

- content of the zip file

For general structure and of the reference design, see Project Delivery - Xilinx devices

...

...

...

...

Additional Sources

...

| anchor | Table_ADS |

|---|---|

| title | Additional design sources |

...

Prebuilt

...

| hidden | true |

|---|---|

| id | Comments |

Notes :

...

...

...

File

...

File-Extension

...

Description

...

Debian SD-Image

...

*.img

...

Debian Image for SD-Card

...

MCS-File

...

*.mcs

...

Flash Configuration File with Boot-Image (MicroBlaze or FPGA part only)

...

MMI-File

...

*.mmi

...

File with BRAM-Location to generate MCS or BIT-File with *.elf content (MicroBlaze only)

...

SREC-File

...

*.srec

...

Converted Software Application for MicroBlaze Processor Systems

...

...

...

...

...

...

...

...

...

...

...

...

...

Download

Reference Design is only usable with the specified Vivado/SDK/PetaLinux/SDx version. Do never use different Versions of Xilinx Software for the same Project.

| HTML |

|---|

<!--

Add correct path:https://shop.trenz-electronic.de/en/Download/?path=Trenz_Electronic/TE0803/Reference_Design/2017.1/Starterkit

--> |

Reference Design is available on:

Design Flow

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

| Note |

|---|

Reference Design is available with and without prebuilt files. It's recommended to use TE prebuilt files for first lunch. |

Trenz Electronic provides a tcl based built environment based on Xilinx Design Flow.

See also:

The Trenz Electronic FPGA Reference Designs are TCL-script based project. Command files for execution will be generated with "_create_win_setup.cmd" on Windows OS and "_create_linux_setup.sh" on Linux OS.

TE Scripts are only needed to generate the vivado project, all other additional steps are optional and can also executed by Xilinx Vivado/SDK GUI. For currently Scripts limitations on Win and Linux OS see: Project Delivery Currently limitations of functionality

...

- (optional for manual changes) Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

Note: Select correct one, see TE Board Part Files

...

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

...

(alternative) Start SDK with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_sdk

Note: Projects contains 3 FSBL template: zynq_fsbl (FSBL modified for DDR Less application → use for Boot.bin), zynq_fsbl_app (FSBL modified for DDR Less application and with demo app included → create Boot with this FSBL and Bitstream only), zynq_fsbl_flash(FSBL modified for Flash programming →FSBL which must be selected separately to program Flash)

See SDK Projects

| Info |

|---|

TE0722 is without DDR, so special FSBL (sources on reference designs) is needed, see also: DDR less ZYNQ Design |

Launch

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

Basic Information, see TE0722 Getting Started

Programming

| Note |

|---|

Check Module and Carrier TRMs for proper HW configuration before you try any design. |

Xilinx documentation for programming and debugging: Vivado/SDK/SDSoC-Xilinx Software Programming and Debugging

QSPI

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

| anchor | Figure_VHM |

|---|---|

| title | Vivado Hardware Manager |

...

...

...

| anchor | Figure_BD |

|---|---|

| title | Block Design |

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

Source location: \sw_lib\sw_apps

zynq_fsbl

...

...

...

Add Files: te_fsbl_hooks.h/.c(for hooks and board)\n\

...

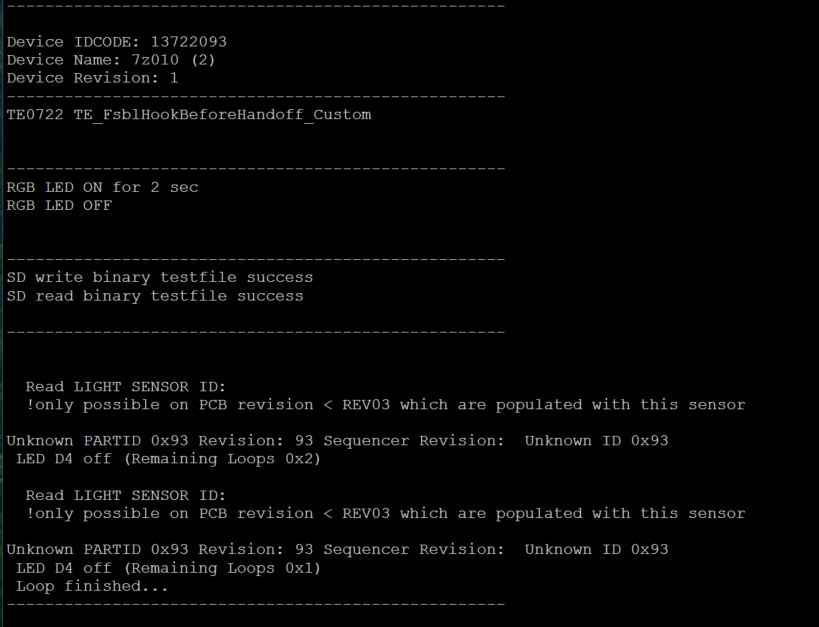

- Display FSBL Banner and Device ID

- Disable Memory initialisation on main.c

zynq_fsbl_app

TE modified 2018.3 FSBL

General:

- Modified Files:main.c, fsbl_hooks.h/.c (search for 'TE Mod' on source code)

Add Files: te_fsbl_hooks.h/.c(for hooks and board)\n\

- General Changes:

- Display FSBL Banner and Device ID

- Disable Memory initialisation on main.c

Module Specific:

- Add Files: all TE Files start with te_*

- Example app for LED access over MIO and sensor access over I2C

zynq_fsbl_flash

TE modified 2018.3 FSBL

General:

- Modified Files: main.c

- General Changes:

- Display FSBL Banner

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

...

...

...

...

...

...

...