Page History

...

| Scroll Title | ||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||

|

...

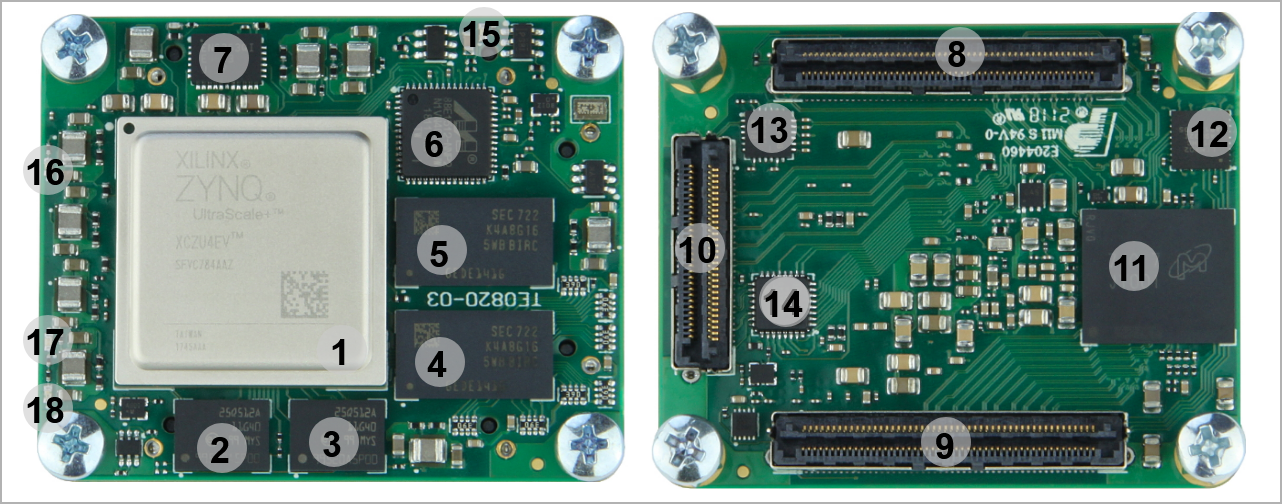

- Xilinx Zynq UltraScale+ MPSoC, U1

- 1.8V, 512 Mbit QSPI flash memory, U7

- 1.8V, 512 Mbit QSPI flash memory, U17

- 8 Gbit (512 x 16) DDR4 SDRAM, U2

- 8 Gbit (512 x 16) DDR4 SDRAM, U3

- Marvell Alaska 88E1512 integrated 10/100/1000 Mbps energy efficient ethernet transceiver, U8

- 6A PowerSoC DC-DC converter (PL_VCCINT, 0.85V), U5

- B2B connector Samtec Razor Beam™ LSHM-150, JM1

- B2B connector Samtec Razor Beam™ LSHM-150, JM2

- B2B connector Samtec Razor Beam™ LSHM-130, JM3

- 4 GByte eMMC memory, U6

- Lattice Semiconductor MachXO2 System Controller CPLD, U21

- I2C programmable, any frequency , any output quad clock generator, U10

- Highly integrated full featured hi-speed USB 2.0 ULPItransceiver, U18

- LED D1(Red) Done Pin

- LED D2 (Green) CPLD Status, User LED

- LED D3 (Red) PS Error

- LED D4 (Green) PS Error Status

Initial Delivery State

| Storage Device Name | Content | Notes |

|---|---|---|

SPI Flash OTP Area | Empty, not programmed | Except serial number programmed by flash vendor. |

SPI Flash Quad Enable bit | Programmed | - |

SPI Flash main array | Not programmed | - |

eFUSE USER | Not programmed | - |

eFUSE Security | Not programmed | - |

| Si5338 OTP NVM | Not programmed | - |

| CPLD (LCMXO2-256HC) | SC0820-02 QSPI Firmware | See Boot Process section. |

...

Date | Revision | Contributors | Description | ||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

|

|

| ||||||||||||||||||||||||

| v.69 | Ali Naseri |

| |||||||||||||||||||||||||

| v.61 | John Hartfiel |

| |||||||||||||||||||||||||

| 2018-03-12 | v.54 |

| |||||||||||||||||||||||||

| 2017-11-20 | v.51 | John Hartfiel |

| ||||||||||||||||||||||||

| 2017-11-10 | v.50 | John Hartfiel |

| ||||||||||||||||||||||||

| 2017-10-18 | v.49 | John Hartfiel |

| ||||||||||||||||||||||||

| 2017-09-25 | v.48 | John Hartfiel |

| ||||||||||||||||||||||||

| 2017-09-18 | v.47 | John Hartfiel |

| ||||||||||||||||||||||||

| 2017-08-30 | v.46 | Jan Kumann |

| ||||||||||||||||||||||||

2017-08-24 | v.36 | John Hartfiel |

| ||||||||||||||||||||||||

| 2017-08-21 | v.34 | John Hartfiel |

| ||||||||||||||||||||||||

| 2017-08-21 | v.33 | Jan Kumann |

| ||||||||||||||||||||||||

| v.7 | John Hartfiel |

| ||||||||||||||||||||||||

2017-08-07 | v.5 | Jan Kumann | Initial version |

...

Overview

Content Tools