Page History

...

| Scroll Title | ||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||

|

...

| Scroll Title | ||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||

|

...

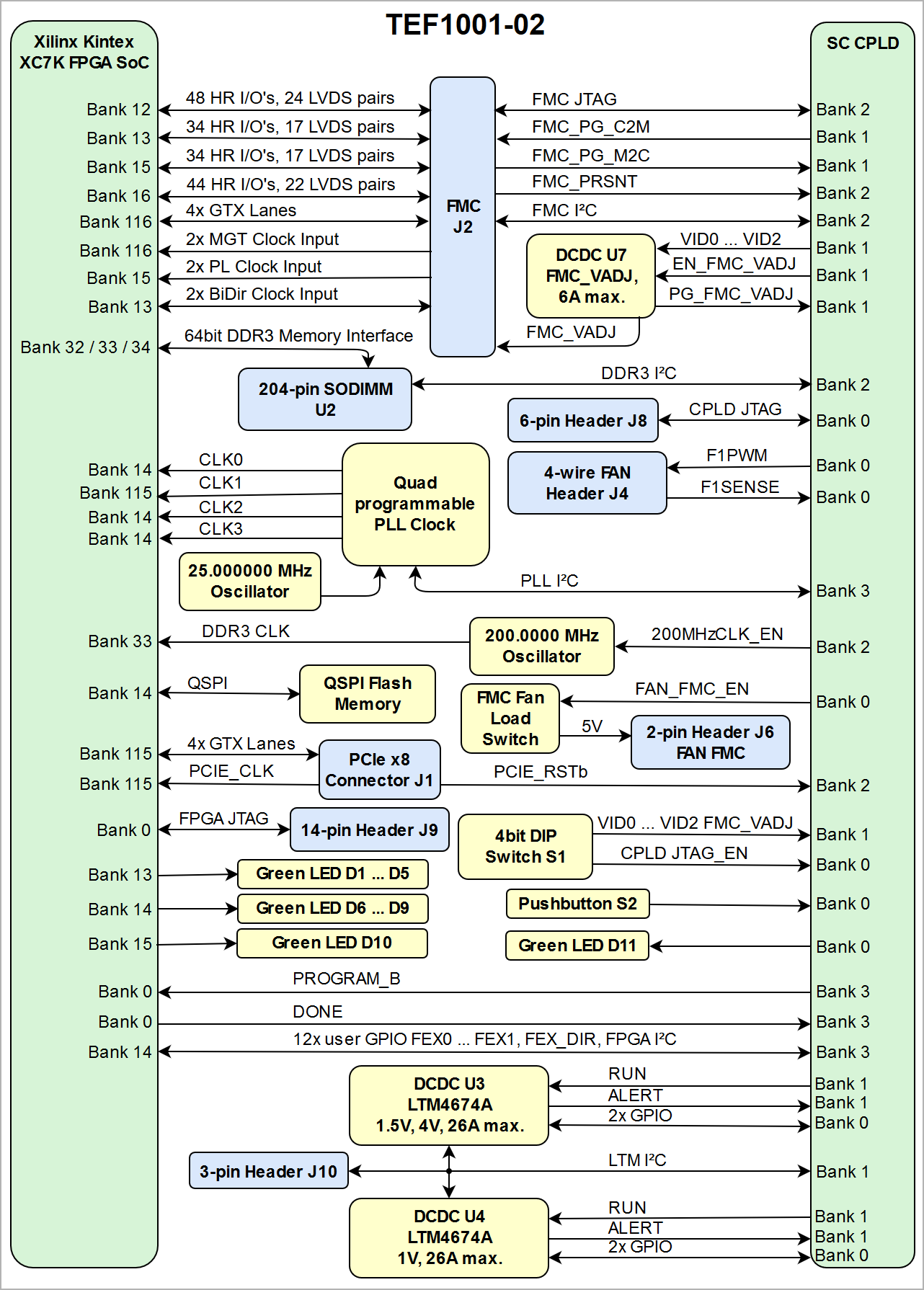

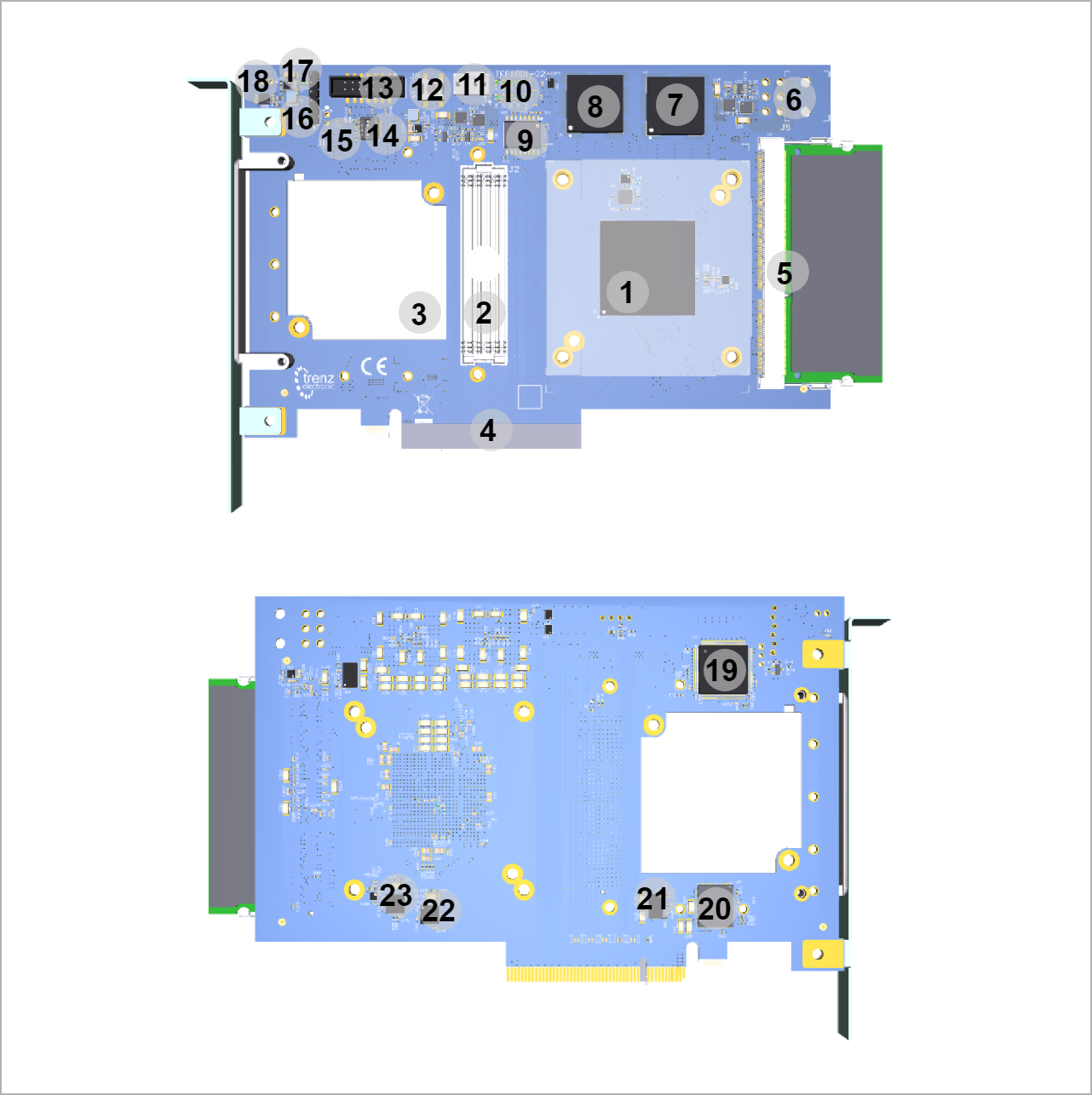

- Xilinx Kintex XC7K-2FBG676I FPGA SoC, U6

- ANSI/VITA 57.1 compliant FMC HPC connector, J2

- Cooling fan 5VDC M1 (45X5MM, 0.7W, 1.06CFM), M1

- PCIe x8 connector, J1

- DDR3 SODIMM 204-pin socket, U2

- 6-pin 12V power connector, J5

- Step-down DC-DC converter @1.5V and @4V (LT LTM4676A), U3

- Step-down DC-DC converter @1.0V (LT LTM4676A), U4

- 256 Mbit Quad SPI Flash Memory (Micron N25Q256A), U12

- 10x Green user LEDs connected to FPGA, D1 ... D10

- 4-wire PWM fan connector, J4

- User button, S2

- FPGA JTAG connector, J9

- 4bit DIP switch, S1

- I²C header for LTM4676A DC-DC converter, J10

- System Controller CPLD JTAG header, J8

- 1x Green LED connected to SC CPLD, D11

- 2-pin 5V FAN header, J6

- System Controller CPLD (Lattice Semiconductor LCMXO2-1200HC), U5

- 6A PowerSoC DC-DC converter @FMC_VADJ (Altera EN5365QI), U7

- 4A PowerSoC DC-DC converter @3.3V (3V3FMC) (Altera EN6347QI), U15

- LDO converter @1.2V (MGTAVTT_FPGA) (TI TPS74401RGW), U17

- LDO converter @1.0V (MGTAVCC_FPGA) (TI TPS74401RGW), U18

- 4A PowerSoC DC-DC converter @1.8V (Altera EN6347QI), U7

Initial Delivery State

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||

|

...

Table 1: Initial delivery state of programmable devices on the module

...

Control Signals

To get started with TEF1001 board, some basic control signals are essential and are described in the following table:

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

By default the configuration mode pins M[2:0] of the FPGA are set to QSPI mode (Master SPI), hence the FPGA is configured from QSPI Flash memory at system start-up. The JTAG interface of the module is provided for storing the initial FPGA configuration data to the QSPI Flash memory.

...

I/O signals and interfaces connected to the FPGA SoCs I/O bank and FMC connector J2:

...

| Interfaces | I/O Signal Count | LVDS-pairs count | Connected to | VCCO bank Voltage | Notes | J2|

|---|---|---|---|---|---|---|

| I/O | 48 | 24 | FPGA Bank 12 HR | FMC_VADJ | Bank voltage FMC_VADJ is supplied by DC-DC converter U7 | |

| 34 | 17 | FPGA Bank 13 HR | FMC_VADJ | |||

| 34 | 17 | FPGA Bank 15 HR | FMC_VADJ | |||

| 44 | 44 | FPGA Bank 16 HR | VIO_B_FMC | Bank voltage VIO_B_FMC is supplied by FMC connector J2 | ||

| I²C | 2 | - | SC CPLD U5, Bank 2, pin 48, 49 | - | FMC connector J2 is hardware programmed to I²C address 0x50 | |

| JTAG | 5 | - | SC CPLD U5, Bank 2, pin 27, 28, 331, 32 ,36 | 3.3V- | 4 JTAG pins with additional signal 'TRST' | |

| MGT | - | 8 (4 x RX/TX) | Bank 116 GTX | - | 4x MGT lanes | |

| Clock Input | - | 2 | Bank 116 GTX | - | 2x Reference clock input to MGT bank | |

| Control Signals | 3 | - | SC CPLD U5, Bank 1, pin 68, 69 ,70 | 3.3V | 'FMC_PG_C2M', 'FMC_PG_M2C', 'FMC_PRSNT_M2C_L' |

...

FMC connector J2 MGT Lanes:

...

| MGT Lane | Bank | Type | Signal Schematic Name | FMC Connector Pin | FPGA Pin | J2|

|---|---|---|---|---|---|---|

| 0 | 116 | GTX |

|

|

| |

| 1 | 116 | GTX |

|

|

| |

| 2 | 116 | GTX |

|

|

| |

| 3 | 116 | GTX |

|

|

|

...

FMC connector J2 reference clock sources:

...

| Signal Schematic Name | Connected to | FMC Connector Pin | FPGA Pin | Notes | J2|

|---|---|---|---|---|---|

| MGT bank 116 | J2-D4 | MGTREFCLK0P_116, D6 | Supplied by attached FMC module | |

| MGT bank 116 | J2-B20 J2-B21 | MGTREFCLK1P_116, F6 MGTREFCLK1N_116, F5 | Supplied by attached FMC module |

...

FMC connector J2 VCC/VCCIO:

...

| Available VCC/VCCIO | FMC Connector Pin | Source | Notes | J2|

|---|---|---|---|---|

| 3V3FMC | J2-D36 | DCDC U15, | Enable by SC CPLD U5, bank 1, pin 60 | |

| 3V3 | J2-D32 | LDO U9, max. current: 0.5A | not dedicated for FMC connector | |

| 12V | J2-C35 | external source through | - | |

| FMC_VADJ | J2-H40 | DCDC U7, | Enable by SC CPLD U5, bank 1, pin 51 |

...

FMC connector J2 Cooling Fan:

...

| Fan Designator | Enable Signal | Notes | J2|

|---|---|---|---|

| M1 | Enable by SC CPLD U5, bank 0, pin 78 | - |

...

Following table lists lane number, MGT bank number, transceiver type, signal schematic name, connector and FPGA pins connection:

...

| Lane | Bank | Type | Signal Name | PCIe Connector Pin | FPGA Pin | |

|---|---|---|---|---|---|---|

| J1 | 0 | 115 | GTX |

|

|

|

| 1 | 115 | GTX |

|

|

| |

| 2 | 115 | GTX |

|

|

| |

| 3 | 115 | GTX |

|

|

|

...

FAN Connectors

The TEF1001 board offers two one FAN connectors connector for cooling the FPGA device and on one built-in FAN for the FMC modules.

| Connector | Signal Schematic net namesNames | Connected to | Notes |

|---|---|---|---|

| 4-Wire PWM FAN connector J4, 12V power supply | 'F1SENSE', pin J4-3 | SC CPLD U5, pin 99 | FPGA cooling FAN can be controlled via I²C interface from FPGA, see current SC CPLD firmware |

| 2-pin FAN connector J6, 5V power supply with TPS2051 Load Switch U25 | 'FAN_FMC_EN', (Load Switch U25, pin 4) | SC CPLD U5, pin 78 | FMC cooling FAN |

...

| Pin Name | SC CPLD Direction | Function | Default Configuration |

|---|---|---|---|

| 200MHZCLK_EN | out | control line | enables 200.0000MHz oscillator U1 |

| BUTTON | in | user | Reset Button |

| CPLD_TDO | out | CPLD JTAG interface | - |

| CPLD_TDI | in | ||

| CPLD_TCK | in | ||

| CPLD_TMS | in | ||

| JTAG_EN | in | ||

| DDR3_SCL | in / out | I²C bus of DDR3 SODIMM socket | I²C connected to FPGA |

| DDR3_SDA | in / out | ||

| PLL_SCL | in / out | I²C bus of SI5338 quad clock PLL | I²C connected to FPGA |

| PLL_SDA | in / out | ||

| PCIE_RSTB | in | PCIe reset input | see refer to current SC CPLD firmware |

| FEX_DIR / FEX0 ... FEX11 | in / out | user GPIO | see refer to current SC CPLD firmware |

| F1PWM | out | FPGA FAN control | see refer to current SC CPLD firmware |

| F1SENSE | in | ||

| FAN_FMC_EN | out | FMC FAN enable | |

| FMC_PG_C2M | out | FMC signals and pins | see refer to current SC CPLD firmware |

| FMC_PG_M2C | in | ||

| FMC_PRSNT_M2C_L | in | ||

| FMC_SCL | in / out | FMC I²C | I²C connected to FPGA |

| FMC_SDA | in / out | ||

| FMC_TCK | FMC JTAG | see refer to current SC CPLD firmware | |

| FMC_TDI | |||

| FMC_TDO | |||

| FMC_TMS | |||

| FMC_TRST | |||

| DONE | in | FPGA configuration signal | PL configuration completed |

| PROGRAM_B | out | PL configuration reset signal | |

| LED1 | out | LED status signal | see refer to current SC CPLD firmware |

| FPGA_IIC_OE | in | SC CPLD works as I²C switch with the FPGA as I²C-Master and on-board peripherals as I²C-slaves | I²C output enable, connected to PL bank 14 pin F25 |

| FPGA_IIC_SCL | in / out | I²C clock line, connected to PL bank 14 pin G26 | |

| FPGA_IIC_SDA | in / out | I²C data line, connected to PL bank 14 pin G25 | |

| EN_1V8 | out | Power control | enable signal DCDC U20 '1V8' |

| PG_1V8 | in | power good signal DCDC U20 '1V8' | |

| EN_3V3FMC | out | enable signal DCDC U15 'EN_3V3FMC' | |

| PG_3V3 | in | power good signal U15 'EN_3V3FMC' | |

| EN_FMC_VADJ | out | enable signal DCDC U7 'FMC_VADJ' | |

| PG_FMC_VADJ | in | power good DCDC U7 'FMC_VADJ' | |

VID0_FMC_VADJ, | out | DCDC U7 power selection pin | |

VID0_FMC_VADJ_CTRL, | in | Power selection of FMC_VADJ, forwarded to DCDC U7 | |

| LTM_1V5_RUN | out | enable signals of DCDC U3, U4 (LTM4676) see refer to current SC CPLD firmware | |

| LTM_4V_RUN | out | ||

| LTM_SCL | in / out | DCDC U3, U4 (LTM4676) I²C | I²C Address U3: 0x40 I²C Address U4: 0x4F I²C interface of LTM4676 ICs |

| LTM_SDA | in / out | ||

| LTM1_ALERT | in | DCDC U3, U4 (LTM4676) control, active low | see refer to current SC CPLD firmware |

| LTM2_ALERT | in | ||

| LTM_1V_IO0 | in / out | ||

| LTM_1V_IO1 | in / out | ||

| LTM_1V5_4V_IO0 | in / out | ||

| LTM_1V5_4V_IO1 | in / out |

...