| Page properties |

|---|

|

Template Revision 2.3

TRM Name always "TE Series Name" +TRM, for example "TE0720 TRM" |

| HTML |

|---|

<!-- tables have all same width (web max 1200px and pdf full page(640px), flexible width or fix width on menu for single column can be used as before) -->

<style>

.wrapped{

width: 100% !important;

max-width: 1200px !important;

}

</style> |

| Page properties |

|---|

|

Important General Note:

|

| Page properties |

|---|

|

----------------------------------------------------------------------- |

| Page properties |

|---|

|

Note for Download Link of the Scroll ignore macro: |

| Scroll pdf ignore |

|---|

Table of Contents |

Overview

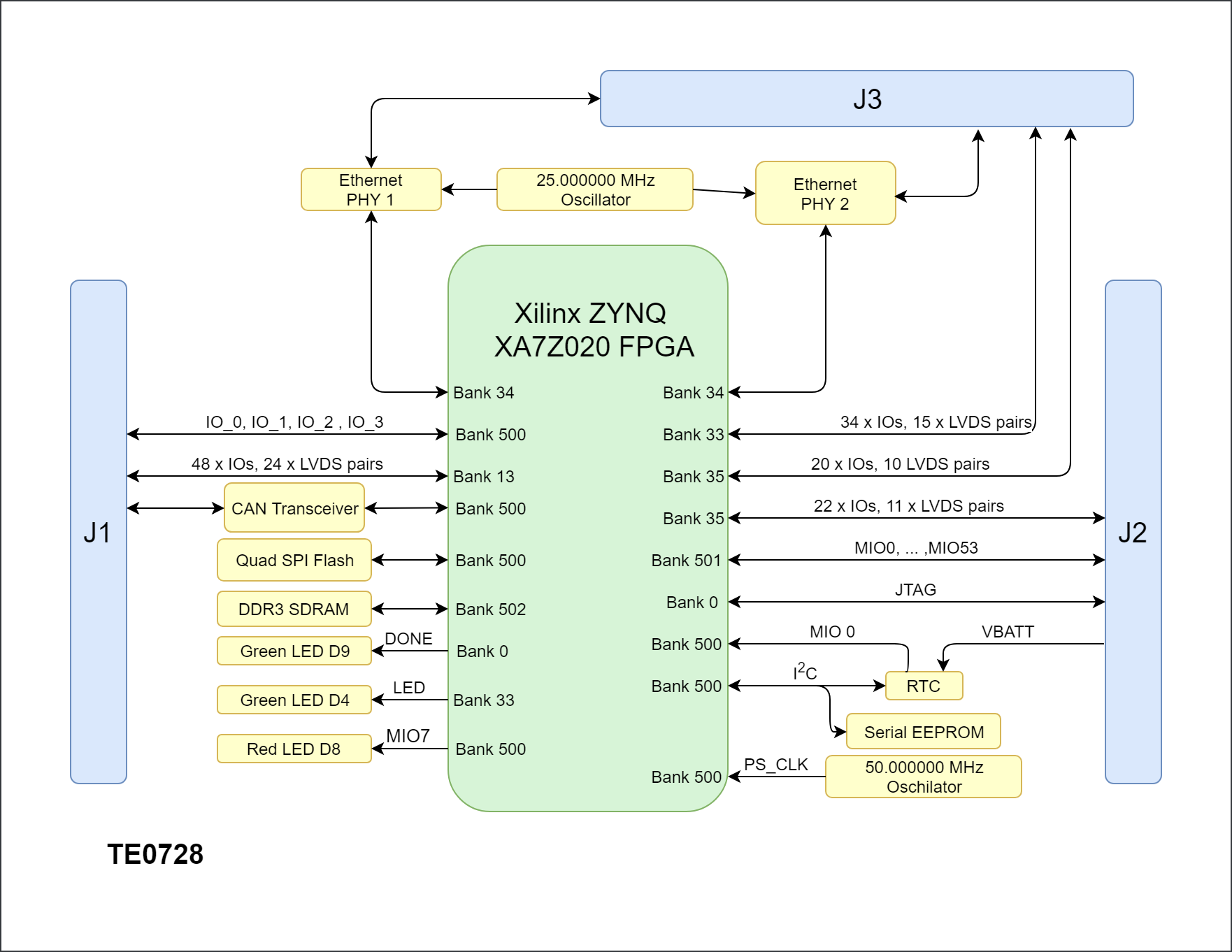

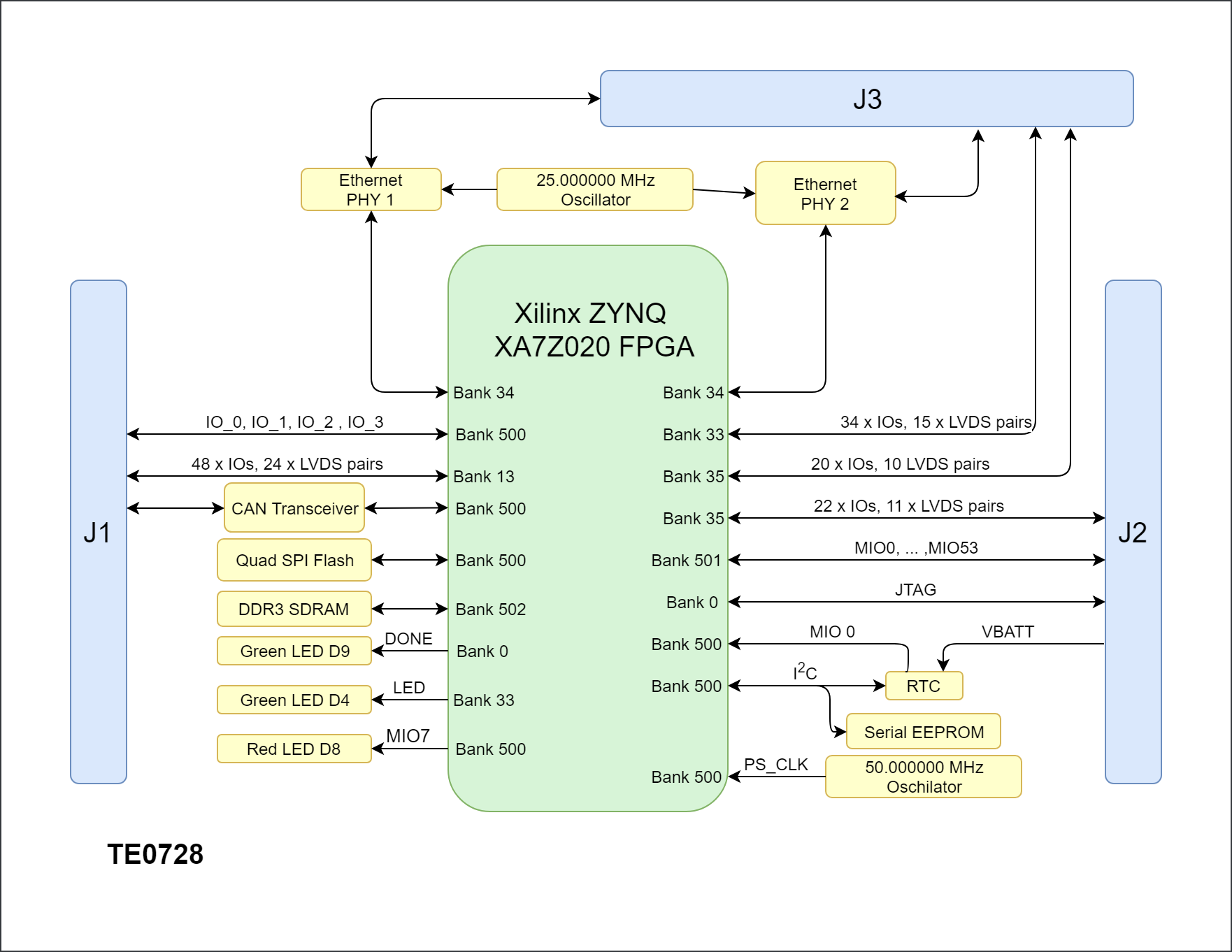

Trenz Electronic TE0728 is an automotive-grade FPGA module integrating a Xilinx Automotive Zynq-7020 FPGA, two 100 Mbit Ethernet transceivers (PHY) , 512 MByte DDR3L SDRAM, 16 MByte Flash memory for configuration and operation, and powerful switching-mode power supplies for all on-board voltages. Numerous configurable I/Os are provided via rugged high-speed strips.

Within the complete module only Automotive components are installed.

All this in a compact 6 x 6 cm form factor, at the most competitive price.

Refer to http://trenz.org/te0728-info for the current online version of this manual and other available documentation.

Key Features

Block Diagram

| Scroll Title |

|---|

| anchor | Figure_OV_BD |

|---|

| title | TE0728 block diagram |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | TE0728 |

|---|

| lbox | true |

|---|

| revision | 16 |

|---|

| diagramName | TE0728 |

|---|

| simpleViewer | false |

|---|

| width | 600 |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 881 |

|---|

|

|

| Scroll Only |

|---|

|

|

Main Components

| Page properties |

|---|

|

Notes : - Picture of the PCB (top and bottom side) with labels of important components

- Add List below

|

| Scroll Title |

|---|

| anchor | Figure_OV_MC |

|---|

| title | TE0728 main components |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | false |

|---|

| revision | 38 |

|---|

| diagramName | TE0728_MC2 |

|---|

| simpleViewer | true |

|---|

| width | 600 |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 1173 |

|---|

|

|

| Scroll Only |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

| | draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | false |

|---|

| revision | 38 |

|---|

| diagramName | TE0728_MC2 |

|---|

| simpleViewer | true |

|---|

| width | 600 |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 1173 |

|---|

|

|

|

- 512 MByte DDR3 SDRAM, Cypress DDR3 Memory, U1

- Xilinx Automotive XA7Z020-1CLG484Q ,U2

- 100 MBit Ethernet transceiver DP83848, U3

- 3.5V to 60V step-down converter, Texas Instruments TPS54260-Q1, U4

- Standard Clock Oscillators @ 25MHz 3.3V, SiTime SiT1618AA, U5

- 1.5 A Low Dropout Linear Regulator, Texas Instruments, TPS74801-Q1, U6

- Real Time Clock, Micro Crystal @32.768 MHz, 3.3V, RV-3029-C3, U7

- 3.5V to 60V step-down converter, Texas Instruments TPS54260-Q1, U8

- 3.5V to 60V step-down converter, Texas Instruments TPS54260-Q1, U9

- 100 MBit Ethernet transceiver DP83848MPHPEP, U10

- 64 Kbit I2C EEPROM, 24LC64, U11

- Low-Quiescent-Current Proggrammable Delay Supervisory Circuit, Texas Instruments TPS3808G01-Q1, U12

- 16 MByte QSPI Nor Flash memory, Cypress S25FL127, U13

- Standard Clock Oscillators @ 50MHz 3.3V, SiTime SiT8918AA, U14

- Low-Quiescent-Current Priggrammable Delay Supervisory Circuit, Texas Instruments TPS3808G01-Q1, U15

- CAN Tranceiver, Texas Instruments SN65HVD230Q1, U16

- B2B connector Samtec Micro Tiger Eye Connector SEM-140-02-03, JM2

- B2B connector Samtec Micro Tiger Eye Connector SEM-140-02-03, JM3

- B2B connector Samtec Micro Tiger Eye Connector SEM-140-02-03, JM1

- User LED Green

Initial Delivery State

| Scroll Title |

|---|

| anchor | Table_OV_IDS |

|---|

| title | Initial delivery state of programmable devices on the module |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

Storage device name | Content | Notes |

|---|

Quad SPI Flash | U13 | Empty | | DDR3 SDRAM | U1 | Empty | | 24LC64 | U11 |

|

|

Control Signals

| Page properties |

|---|

|

- Overview of Boot Mode, Reset, Enables,

|

| Scroll Title |

|---|

| anchor | Table_OV_BP |

|---|

| title | Boot process. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

MODE Signal State | Boot Mode |

|---|

High or open | QSPI |

|

Signals, Interfaces and Pins

| Page properties |

|---|

|

Notes : - For carrier or stand-alone boards use subsection for every connector type (add designator on description, not on the subsection title), for example:

- For modules which needs carrier use only classes and refer to B2B connector if more than one is used, for example

|

Board to Board (B2B) I/Os

FPGA bank number and number of I/O signals connected to the B2B connector:

| Scroll Title |

|---|

| anchor | Table_SIP_B2B |

|---|

| title | General PL I/O to B2B connectors information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| FPGA Bank | B2B Connector | I/O Signal Count | Voltage Level | Notes |

|---|

| 13 | JM1 | 48 | VCCO_13 |

| | 500 | JM1 | 4 | 3.3V |

| | 33 | JM3 | 34 | 3.3V |

| | 35 | JM3 | 20 | 3.3V |

| | 35 | JM2 | 22 | 3.3V |

| | 501 | JM2 | 38 | VMIO1 | MIO1 VREF is connected to resistor divider to support HSTL18 |

|

JTAG Interface

JTAG access to the Xilinx XA7Z020 FPGA through B2B connector JM2.

| Scroll Title |

|---|

| anchor | Table_SIP_JTG |

|---|

| title | JTAG pins connection |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

JTAG Signal | B2B Pin |

|---|

| TMS | JM2-12 | | TDI | JM2-10 | | TDO | JM2-8 | | TCK | JM2-6 |

|

PS7 UART

There is no fixed mapping for PS7 UART, if needed it can be mapped to free pins from MIO1 Bank or via EMIO to PL pins.

Recommended mapping for primary (console, debug) UART are MIO52, MIO53 for all cases when MIO1 is not used for off-board Gigabit ETH PHY.

On-board Peripherals

| Page properties |

|---|

|

Notes : - add subsection for every component which is important for design, for example:

- Two 100 Mbit Ethernet Transciever PHY

- USB PHY

- Programmable Clock Generator

- Oscillators

- eMMCs

- RTC

- FTDI

- ...

- DIP-Switches

- Buttons

- LEDs

|

| Scroll Title |

|---|

| anchor | Table_OBP |

|---|

| title | On board peripherals |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Chip/Interface | IC | PS7 Peripheral | Notes |

|---|

| SPI Flash | S25FL127SABMFV10 | QSPI0 | 16 MByte Flash | | I2C EEPROM | 24LC64 | I2C0 | 64 KByte EEPROM | | RTC I2C | RV-3029 | I2C0 |

| | RTC Interrupt | RV-3029 | GPIO - MIO0 |

| | User LED | LED Green | GPIO - MIO7 |

|

|

16 MByte Quad SPI Flash Memory

On-board QSPI flash memory S25FL127SABMFV10 is used to store initial FPGA configuration. Datasheet is provided in Texas Instruments. Besides FPGA configuration, remaining free flash memory can be used for user application and data storage. All four SPI data lines are connected to the FPGA allowing x1, x2 or x4 data bus widths. Maximum data rate depends on the selected bus width and clock frequency used.

Quad SPI Flash (U7) is connected to the Zynq PS QSPI0 interface via PS MIO bank 500.

| Scroll Title |

|---|

| anchor | Table_OBP_SPI |

|---|

| title | Quad SPI interface MIOs and pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| MIO Pin | Schematic | U13 Pin | Notes |

|---|

| MIO1 | SPI_CS | A1 |

| | MIO2 | SPI_DQ0/M0 | A2 |

| | MIO3 | SPI_DQ1/M1 | F6 |

| | MIO4 | SPI_DQ2/M2 | E4 |

| | MIO5 | SPI_DQ3/M3 | A3 |

| | MIO6 | SPI_SCK/M4 | A4 |

|

|

Supply Voltage: 2.7V to 3.6V

Temperature Range:

- Industrial (-40°C to +85°C)

- Industrial Plus (-40°C to +105°C)

- Automotive AEC-Q100 Grade 3 (-40°C to +85°C)

- Automotive AEC-Q100 Grade 2 (-40°C to +105°C)

RTC I2C

The RV-3029-C3 is an ultra miniature Real-Time-Clock Module with embedded Crystal. This RTC has an I2C Bus (2-wire SerialInterface) and offers temperature compensated time. The STC-Smart Temperature Compensation is calibrated in the factory and leads to a very high time-accuracy of ± 6ppm from -40°C to +85°C and ± 8ppm from -40°C to +125°C.

| Scroll Title |

|---|

| anchor | Table_OBP_RTC |

|---|

| title | I2C interface MIOs and pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| MIO Pin | Schematic | U7 Pin | Notes |

|---|

| MIO15 | SDA | 5 | On-board RTC, and EEPROM | | MIO14 | SCL | 4 | On-board RTC, and EEPROM |

|

I2C EEPROM

The Microchip Technology Inc. 24LC64 is a 64 Kbit Electrically Erasable PROM. The device is organized as a single block of 8K x 8-bit memory with a 2-wire serial interface. Lowvoltage design permits operation down to 1.7V, with standby and active currents of only 1 μA and 3 mA, respectively. It has been developed for advanced, lowpower applications such as personal communications or data acquisition. The 24LC64 also has a page write capability for up to 32 bytes of data. Functional address lines allow up to eight devices on the same bus, for up to 512 Kbits address space.

| Scroll Title |

|---|

| anchor | Table_OBP_EEP |

|---|

| title | I2C EEPROM interface MIOs and pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| MIO Pin | Schematic | U11 Pin | Notes |

|---|

| MIO15 | SDA | 3 | On-board RTC, and EEPROM | | MIO14 | SCL | 1 | On-board RTC, and EEPROM |

|

LEDs

| Scroll Title |

|---|

| anchor | Table_OBP_LED |

|---|

| title | On-board LEDs |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Schematic | Color | Connected to | Active Level | IO Standard |

|---|

| D9 | Green | DONE | Low | not applicable | | D8 | RED | MIO7 | High | not applicable | | D4 | Green | PL pin V18 | High | LVCMOS33 |

|

512 Mbyte DDR3L SDRAM

The TE0728 SoM has two 512 GByte volatile DDR3 SDRAM IC for storing user application code and data.

- Part number: NT5CC256M16DP Nanya

- Supply voltage: 1.35V

- Speed: 1600 Mbps

- NOR Flash

- Temperature: -40°C ~95°C

Configuration of the DDR3 memory controller in the FPGA should be done using the MIG tool in the Xilinx Vivado Design Suite IP catalog.

Ethernet

There are two 100 MBit Extreme Temperature Ethernet DP83848-EP are provided by Texas Instrument on the board. Datasheet is provided TI website, Literature number SNLS208H. Both PHY's are connected with all I/O Pins to FPGA Bank 34 (VCCIO = 3.3V). PHY Clock 25 MHz source is provided from MEMS Oscillator. There is no sharing of signals for the two PHY's.

PUDC pin is connected with pull-up to 3.3V those pre-configuration pull-ups are disabled by default. Strapping resistor exist to change the PUDC mode.

Both PHY's must be operated in MII Mode, other modes are not supported. It is possible to use PS ENET0 or ENET1 via EMIO routing or Ethernet IP Cores implemented in PL Fabric.

| Scroll Title |

|---|

| anchor | Table_OBP_ETH |

|---|

| title | Ethernet PHY to Zynq SoC connections |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Schematic | ETH1 | ETH2 | Pullup | Notes |

|---|

| CTREF | J3-57 | J3-25 |

| Magnetics center tap voltage | | TD+ | J3-58 | J3-28 | on-board |

| | TD- | J3-56 | J3-26 | on-board |

| | RD+ | J3-52 | J3-22 | on-board |

| | RD- | J3-50 | J3-20 | on-board |

| | LED1 | J3-55 | J3-23 | on-board |

| | LED2 | J3-53 | J3-21 | on-board |

| | LED3 | J3-51 | J3-19 | on-board |

| | POWERDOWN/INT | L21 | R20 | on-chip | It is recommended to configure FPGA I/O as input with Pullup or as output driving 1 if Interrupt not used. | | RESET_N | M15 | R16 | on-chip | It is recommended to configure FPGA I/O as input with Pullup or as output (active low PHY Reset). |

|

It is recommended to add IOB TRUE constraint for the MII Interface pins.

When connecting the PHY's to Zynq PS ETH0, ETH1 EMIO GMII Interfaces it is recommended to use GMII to MII Wrap IP Core. This IP core maps the EMIO GMII to external MII Interface.

CAN Transceiver

The SN65HVD230Q, controller area network (CAN) transceivers are designed for use with the Texas Instruments TMS320Lx240x 3.3-V DSPs with CAN controllers. The datasheet is avaiable in Texas Instrumens website. They are intended for use in applications employing the CAN serial communication physical layer in accordance with the ISO 11898 standard. Each CAN transceiver is designed to provide differential transmit capability to the bus and differential receive capability to a CAN controller at speeds up to 1 Mbps. Temperature must be in range of -40°C ~125°C .

| Scroll Title |

|---|

| anchor | Table_OBP_CAN |

|---|

| title | CAN Tranciever interface MIOs |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| MIO Pin | Schematic | U16 Pin | Notes |

|---|

| MIO8 | D | 1 |

| | MIO9 | R | 4 |

|

|

Low Quiescent Current Programmable Delay Supervisory Circuit

The TPS3808G01-Q1 microprocessor supervisory circuits monitor system voltages from 0.4 V to 5 V, asserting an open-drain RESET signal when the SENSE voltage drops below a preset threshold or when the manual reset (MR) pin drops to a logic low. The RESET output remains low for the useradjustable delay time after the SENSE voltage and MR return above their thresholds. Datasheet is available in Texas Instruments website.

The TPS3808G01-Q1 device uses a precision reference to achieve 0.5% threshold accuracy for VIT ≤ 3.3 V. The reset delay time can be set to 20 ms by disconnecting the CT pin, 300 ms by connecting the CT pin to VDD using a resistor, or can be useradjusted from 1.25 ms to 10 s by connecting the CT pin to an external capacitor. The TPS3808G01-Q1 has a very low typical quiescent current of 2.4 μA, so it is well suited for battery-powered applications.

Low Dropout Linear Regulator

The TPS74801-Q1 low-dropout (LDO) provides an easy-to-use robust power management solution for a wide variety of applications. User programmable soft-start minimizes stress on the input power source by reducing capacitive inrush current on start-up. The soft-start is monotonic and well- suited for powering many different types of Monitoring or Provides a Sequencing Signal processors and ASICs. The enable input and power for Other Supplies good output allow easy sequencing with external regulators. This complete flexibility permits the user to configure a solution that meets the sequencing Voltage Startup requirements of FPGAs, DSPs, and other applications with special start-up requirements.

A precision reference and error amplifier deliver 2% accuracy over load, line, temperature, and process. The device is stable with any type of capacitor greater than or equal to 2.2 μF, and is fully specified SON-10 and 5 x 5 QFN-20 Packages from –40°C to 105°C for the DRC package, and from –40°C to 125°C for the RGW package.

Clock Sources

| Scroll Title |

|---|

| anchor | Table_OBP_CLK |

|---|

| title | Osillators |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| IC | Description | Frequency | Used as |

|---|

| U14 | MEMS Oscillator | 50 MHz | PS PLL clock | | U5 | MEMS Oscillator | 25 MHz | Ethernet PHY Clock | | U7 | RTC (internal oscillator) | 32.768 KHz | Used by RTC, CLKOUT of RTC not connected |

|

Power and Power-On Sequence

Power Supply

Power supply with minimum current capability of 3.5 A for system startup is recommended.

Power Consumption

| Scroll Title |

|---|

| anchor | Table_PWR_PC |

|---|

| title | Power Consumption |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Power Input Pin | Typical Current |

|---|

| VIN | TBD* |

|

* TBD - To Be Determined

Power Distribution Dependencies

| Scroll Title |

|---|

| anchor | Figure_PWR_PD |

|---|

| title | Power Distribution |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | false |

|---|

| revision | 4 |

|---|

| diagramName | TE0728_PWR_PD |

|---|

| simpleViewer | true |

|---|

| width | 300 |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 421 |

|---|

|

|

| Scroll Only |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | false |

|---|

| revision | 4 |

|---|

| diagramName | TE0728_PWR_PD |

|---|

| simpleViewer | false |

|---|

| width | 300 |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 421 |

|---|

|

|

|

Power-On Sequence

| Scroll Title |

|---|

| anchor | Figure_PWR_PS |

|---|

| title | Power Sequence |

|---|

|

| Scroll Ignore |

|---|

Create DrawIO object here: Attention if you copy from other page, objects are only linked. |

| Scroll Only |

|---|

image link to the generate DrawIO PNG file of this page. This is a workaround until scroll pdf export bug is fixed |

|

The PS and PL power supplies are fully independent. PS power supplies (VCCPINT, VCCPAUX, VCCPLL, VCCO_DDR, VCCO_MIO0, and VCCO_MIO1) can be powered before or after any PL power supplies. The PS and PL power regions are isolated to prevent damage. The recommended power-on sequence is VCCPINT, then VCCPAUX and VCCPLL together, then the PS VCCO supplies (VCCO_MIO0, VCCO_MIO1, and VCCO_DDR) to achieve minimum current draw and ensure that the I/Os are 3-stated at power-on. The PS_POR_B input is required to be asserted to GND during the power-on sequence until VCCPINT, VCCPAUX and VCCO_MIO0 have reached minimum operating levels to ensure PS eFUSE integrity.

Voltage Monitor Circuit

Power Rails

| Scroll Title |

|---|

| anchor | Table_PWR_PR |

|---|

| title | Module power rails. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

B2B Name | B2B JM1 Pin | B2B JM2 Pin | B2B JM3 Pin | Direction | Notes |

|---|

| VIN | 1,3 | - | - | Input | Supply voltage from carrier board. | | VCCO_13 | 39 | - | - | I/O |

| | VBATT | - | 1 | - | Output |

| | 3.3V | 19 | 2, 4 | 25,57 | Output | Internal 3.3V voltage level. | 1.8V | - | 5 | - | Output | Internal 1.8V voltage level. |

|

Bank Voltages

| Scroll Title |

|---|

| anchor | Table_PWR_BV |

|---|

| title | Zynq SoC bank voltages. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Schematic Name | | Notes |

|---|

| 500 | VCCO_MIO0_500 | 3.3V |

| | 501 | VCCO_MIO1_500 | 3.3V |

| | 502 | VCCO_DDR_502 | 1.5V |

| | 13 HR | VCCO_13 | 3.3V | Supplied by the carrier board. JM1 | | 33 HR | VCCO_33 | 3.3V | Supplied by carrier board. JM3 | | 34 HR | VCCO_34 | 3.3V |

| | 35 HR | VCCO_35 | 3.3V | Supplied by the carrier board. JM2,JM3 |

|

Board to Board Connectors

6 x 6 modules use two or three Samtec Micro Tiger Eye Connector on the bottom side.

3 x REF-189018-01 (compatible to SEM-140-02-03.0-H-D-A), (80 pins, "40" per row)

Operating Temperature:-55°C ~ 125°C

Current Rating: 2.6A per ContactNumber of Positions: 80

Number of Rows: 2

Technical Specifications

Absolute Maximum Ratings

Processing System(PS)

| Scroll Title |

|---|

| anchor | Table_TS_AMR_PS |

|---|

| title | PS absolute maximum ratings |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Symbols | Description | Min | Max | Unit |

|---|

| VCCPINT | PS internal logic supply voltage | -0.5 | 1.1 | V | | VCCPAUX | PS auxiliary supply voltage | -0.5 | 2.0 | V | | VCCPLL | PS PLL supply | -0.5 | 2.0 | V | | VCCO_DDR | PS DDR I/O supply voltage | -0.5 | 2.0 | V | | VPREF | PS input reference voltage | -0.5 | 2.0 | V | | VCCO_MIO0 | PS MIO I/O supply voltage for HR I/O banks | -0.5 | 3.6 | V | | VCCO_MIO1 | PS MIO I/O supply voltage for HR I/O banks | 1.71 | 3.45 | V |

|

Programmable Logic(PL)

| Scroll Title |

|---|

| anchor | Table_TS_AMR_PL |

|---|

| title | PL absolute maximum ratings |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Symbols | Description | Min | Max | Unit |

|---|

| VCCINT | PL internal logic supply voltage | -0.5 | 1.1 | V | | VCCPAUX | PL auxiliary supply voltage | -0.5 | 2.0 | V | | VCCPLL | PL PLL supply | -0.5 | 1.1 | V | | VPREF | PL input reference voltage | -0.5 | 2.0 | V | | VCCO | PL supply voltage for HR I/O banks | -0.5 | 3.6 | V | | VIN | I/O input voltage for HR I/O banks | 1.71 | 3.45 | V |

|

| Scroll Title |

|---|

| anchor | Table_TS_AMR |

|---|

| title | Module absolute maximum ratings |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Parameter | Min | Max | Units | Reference Document |

|---|

| VIN supply voltage | 3.5 | 60 | V | TPS54260-Q1 datasheets. | | Supply voltage for PS MIO banks | 1.71 | 3.465 | V | See Xilinx DS187 datasheet. | | I/O input voltage for PS MIO banks | -0.2 | VCCO_MIO + 0.20 | V | See Xilinx DS187 datasheet. | | Supply voltage for PS DDR | 1.14 | 1.89 | V | See Xilinx DS187 datasheet. | | I/O input voltage for PS DDR | -0.20 | VCCO_DDR + 0.20 | V | See Xilinx DS187 datasheet. | | Supply voltage for HR I/Os banks | 1.14 | 3.465 | V | See Xilinx DS187 datasheet. | | I/O input voltage for HR I/O banks | -0.20 | VCCIO + 0.20 | V | See Xilinx DS187 datasheet. | | Storage Temperature | -65 | 150 | °C | See Xilinx DS187 datasheet. | | CAN Transceiver Temperature | -40 | 125 | °C | See Texas Instrument sn65hvd230q-q1 datasheet. | | SPI Flash Memory | -40 | 85 | °C | See Cypress S25FL127S datasheet. | | DDR3 SDRAM Temperature | -40 | 95 | °C | See Nanya NT5CC256M16CP-DIA datasheet. |

|

Recommended Operating Conditions

Commercial grade: 0°C to +70°C.

Industrial and automotive grade: -40°C to +85°C.

Operating temperature range depends also on customer design and cooling solution. Please contact us for options.

| Scroll Title |

|---|

| anchor | Table_TS_ROC |

|---|

| title | Recommended operating conditions |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Parameter | Min | Max | Units | Reference Document |

|---|

| VIN supply voltage | 3.5 | 60 | V | TPS54260-Q1 datasheets. | | Supply voltage for PS MIO banks | 1.71 | 3.465 | V | See Xilinx DS187 datasheet. | | I/O input voltage for PS MIO banks | -0.2 | VCCO_MIO + 0.20 | V | See Xilinx DS187 datasheet. | | Supply voltage for PS DDR | 1.14 | 1.89 | V | See Xilinx DS187 datasheet. | | I/O input voltage for PS DDR | -0.20 | VCCO_DDR + 0.20 | V | See Xilinx DS187 datasheet. | | Supply voltage for HR I/Os banks | 1.14 | 3.465 | V | See Xilinx DS187 datasheet. | | I/O input voltage for HR I/O banks | -0.20 | VCCIO + 0.20 | V | See Xilinx DS187 datasheet. | | Storage Temperature | -65 | 150 | °C | See Xilinx DS187 datasheet. | | CAN Transceiver Temperature | -40 | 125 | °C | See Texas Instrument sn65hvd230q-q1 datasheet. | | SPI Flash Memory | -40 | 85 | °C | See Cypress S25FL127S datasheet. | | DDR3 SDRAM Temperature | -40 | 95 | °C | See Nanya NT5CC256M16CP-DIA datasheet. |

|

Physical Dimensions

| Scroll Title |

|---|

| anchor | Figure_TS_PD |

|---|

| title | Physical Dimension |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | false |

|---|

| revision | 20 |

|---|

| diagramName | TE0728_MC1 |

|---|

| simpleViewer | true |

|---|

| width | 600 |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 1721 |

|---|

|

|

| Scroll Only |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

| | draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | false |

|---|

| revision | 20 |

|---|

| diagramName | TE0728_MC1 |

|---|

| simpleViewer | false |

|---|

| width | 600 |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 1721 |

|---|

|

|

|

Variants Currently In Production

| Scroll Title |

|---|

| anchor | Table_VCP_SO |

|---|

| title | Trenz Electronic Shop Overview |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

|

Revision History

Hardware Revision History

| Scroll Title |

|---|

| anchor | Table_RH_HRH |

|---|

| title | Hardware Revision History |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Revision | Note | PCN | Documentation Link |

|---|

| - | 01 | Prototypes | - | - |

|

|

|

|

|

|

Hardware revision number is printed on the PCB board next to the module model number separated by the dash.

Document Change History

| Page properties |

|---|

|

- Note this list must be only updated, if the document is online on public doc!

- It's semi automatically, so do following

Add new row below first Copy "Page Information Macro(date)" Macro-Preview, Metadata Version number, Author Name and description to the empty row. Important Revision number must be the same as the Wiki document revision number Update Metadata = "Page Information Macro (current-version)" Preview+1 and add Author and change description. --> this point is will be deleted on newer pdf export template - Metadata is only used of compatibility of older exports

|

| Scroll Title |

|---|

| anchor | Table_RH_DCH |

|---|

| title | Document change history. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Revision | Contributor | Description |

|---|

| Page info |

|---|

| infoType | Modified date |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| type | Flat |

|---|

|

| | Page info |

|---|

| infoType | Current version |

|---|

| prefix | v. |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| | Page info |

|---|

| infoType | Modified by |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| | -- | all | | Page info |

|---|

| infoType | Modified users |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| |

|

Disclaimer

| Include Page |

|---|

| IN:Legal Notices |

|---|

| IN:Legal Notices |

|---|

|