...

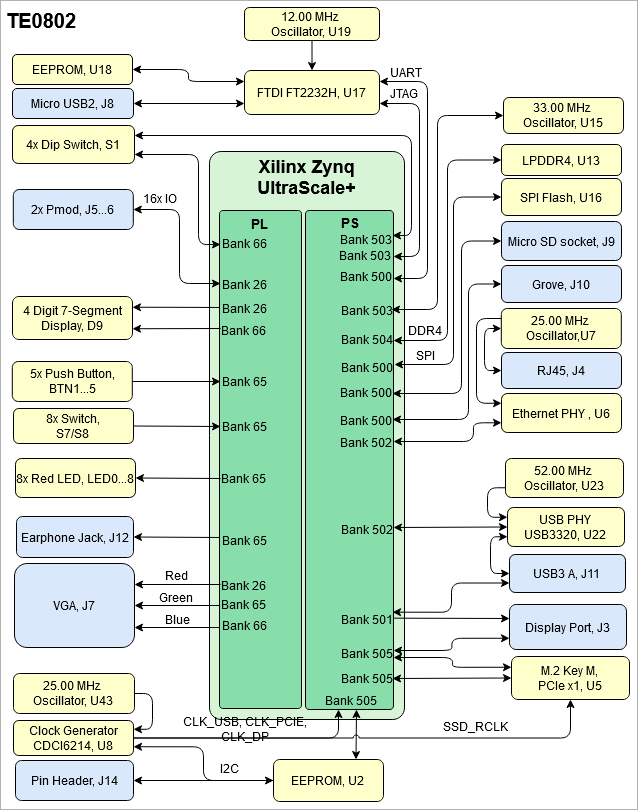

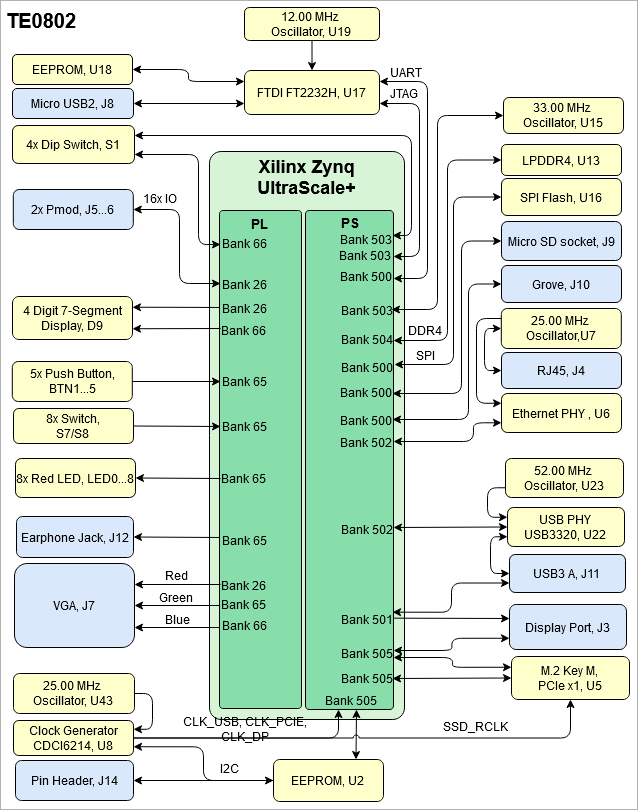

- MPSoC: XCZU2CG - Xilinx Zynq UltraScale+ MPSoC

- RAM/Storages:

- SDRAM: LPDDR4 -3733 8Gb 256Mx16x 2

- SPI Flash 256Mb (32M x 8) 133 MHz

- EEPROMs 2Kb (256 x 8)

- EEPROMs 4Kb (512 x 8)

...

| Scroll Title |

|---|

| anchor | Figure_OV_BD |

|---|

| title | TE0802 Block Diagram |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 24 |

|---|

| diagramName | TE0802_OV_BD |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 638 |

|---|

|

|

| Scroll Only |

|---|

|

|

...

Bootmode signals must be set through DIP Switch S9S1.

| Scroll Title |

|---|

| anchor | Table_OV_BP |

|---|

| title | Boot Process |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

MODE Signal State | MODE2 S9-C | MODE1 S9S1-2(B) | MODE0 S9S1-1(A) | Boot Mode |

|---|

MODE[2:0]=000 | OFF | OFF | OFF | JTAG | MODE[2:0]=001 | OFF | OFF | ON | QSPI (24 bit)not supported | MODE[2:0]=010 | OFF | ON | OFF | QSPI(32 bit) | MODE[2:0]=011 OFF | ON | ON | SD0(2.0) | | MODE[2:0]=111 | ON | ON | ON | USB(2.0) |

|

Reset setting is available through Push Button BTN6.

...

| Scroll Title |

|---|

| anchor | Table_SIP_B2B |

|---|

| title | General I/O to Pin Header and Connectors Information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| FPGA Bank | Connector | I/O Signal Count | Voltage Level | Notes |

|---|

| Bank 503 | Micro USB, J8 (over FTDI) | 4 Single Ended | 3.3 V | JTAG | | Bank 500 | Micro USB, J8 (over FTDI) | 2 Single Ended | 3.3 V | UART | | Bank 500 | Micro SD Card, J9 | 7 Single Ended | 3.3 V |

| | Bank 502 | Micro SD CardETH RJ45, J4 (over ETH PHY) | 14 Single Ended | 1.8 V |

| | Bank 505, 502 | USB 3.0, J11 (USB2 over USB PHY) | 2 Differential Pairs, 12 Single Ended | -- / 1.8V0.85 V |

| Bank 505, 501 | SSD M.2, U5 | 2 Differential Pairs | 0.85 V | Bank 501 | SSD M.2 , U5 5 Single Ended | -- / 3.3 V |

| | Bank 505, 501 | Display Port Connector, J3 | 2 Differential Pairs | 0.85 V | Bank 26 | D-Sub Host Socket, J7 | 2 , 5 Single Ended | --/ 3.3 V |

| | Bank 26, 65, 66, | D-Sub Host Socket (VGA), J7 | 12 14 Single Ended | 3.3 V / 1.8 V / 1.8 V |

| | Bank 65 | Earphone, J12 | 3 Single Ended | 1.8 V |

| | Bank 500 | Grove Connector, J10 | 2 Single Ended | 3.3 V |

| | Bank 26 | Pmod Host Socket, J5 | 8 Single Ended | 3.3 V |

| | Bank 26 | Pmod Host Socket, J6 | 8 Single Ended | 3.3 V |

|

|

...

| Scroll Title |

|---|

| anchor | Table_SIP_TestPoint |

|---|

| title | Test Points Information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

Test Point | Signals | B2B Connector | Notes |

|---|

| 1TP1 | +1.1V_LPDDR4 | - |

| | 2TP2 | +1.8V_MGTRAVTT |

| | -TP3 | 3 | +1.8V_PL | - |

| | 4TP4 | FT_B_TX | - |

| | 5TP5 | DP_TX_PWR | - |

| | 6TP6 | GND | - |

| | 7TP7 | GND | - |

| | 8TP8 | PMIC2_SDA |

| | -TP9 | 9 | PMIC2PMIC2_TP | - |

| | 10TP10 | ONKEY2 |

| | -TP11 | 11 | PMIC2_SCL |

| | -TP12 | 12 | DP_TX_HPD | - |

| | 13TP13 | DP_TX_PWR |

| | -TP14 | 14 | INT_SCL1 | - |

| | 15TP15 | INT_SDA1 |

| | -TP16 | 16 | FT_B_RX |

| | -TP17 | 17 | CLOCKDIST_OE | - |

| | 18TP18 | +0.85V_VCCINT | - |

| | 19TP19 | +3.3V |

| | -TP20 | 20 | +1.8V_PS |

| | -TP21 | 21 | ERR_STATUS | - |

| | 22TP22 | +1.2V_PSPLL |

| | -TP23 | 23 | GND |

| | -TP24 | 24 | GND | - |

| | 25TP25 | PMIC1_SCA |

| | -TP26 | 26 | PMIC1_SDA | - |

| | 27TP27 | ONKEY1 | - |

| | 28TP28 | PMIC1_TP |

| | -TP29 | 29 | POR_B |

| | -TP30 | 30 | PSBATT |

| | -TP31 | 31 | SRST_B |

| | -TP32 | 32 | DONE |

| | -TP33 | 33 | INIT_B | - |

| | 34TP34 | VBUS |

| | -TP35 | 35 | USB_VBUS | - |

| | 36TP36 | PROG_B |

| | -TP37 | 37 | ERR_OUT- |

|

|

On-board Peripherals

| Page properties |

|---|

|

Notes : - add subsection for every component which is important for design, for example:

- Two 100 Mbit Ethernet Transciever PHY

- USB PHY

- Programmable Clock Generator

- Oscillators

- eMMCs

- RTC

- FTDI

- ...

- DIP-Switches

- Buttons

- LEDs

|

...

| Scroll Title |

|---|

| anchor | Table_OBP |

|---|

| title | On-board Peripherals |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

|

Quad SPI Flash Memory

| Page properties |

|---|

|

Notes : Minimum and Maximum density of quad SPI flash must be mentioned for other assembly options. |

he TE0802 evaluation board has one single QSPI flash connected as x4. Flash size depends on the assembly option, default 32MB

| Scroll Title |

|---|

| anchor | Table_OBP_SPI |

|---|

| title | Quad SPI Interface MIOs and Pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| MIO Pin | Schematic | U16 Pin | Notes |

|---|

| MIO0 | MIO0 | B2 | SPI_CLK | | MIO1 | MIO1 | D2 | SPI_DQ1 | | MIO2 | MIO2 | C4 | SPI_DQ2 | | MIO3 | MIO3 | D4 | SPI_DQ3 | | MIO4 | MIO4 | D3 | SPI_DQ0 | | MIO5 | MIO5 | C2 | SPI_CS |

|

...

| Scroll Title |

|---|

| anchor | Table_OBP_I2C_FPGA_EEP |

|---|

| title | I2C Address for FPGA EEPROM |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| MIO PinType | I2C Address | Designator | Notes |

|---|

| MIO8...94AA025E48T-I/OT | 0x50 | U2 | EEPROM with MAC |

|

| Scroll Title |

|---|

| anchor | Table_OBP_FTDI_EEP |

|---|

| title | I2C FTDI EEPROM Interface Pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Pin | Schematic | U18 Pin | Notes |

|---|

| CS | EECS | 1 | FTDI | | CLK | EECLK | 2 | FTDI | | DIN/DO | EEDATA | 3/4 | FTDI |

|

...

| Scroll Title |

|---|

| anchor | Table_OBP_DIP_SWITCH |

|---|

| title | DIP Switches |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Designator | Schematic | Connected to | Functionality | Note |

|---|

| S1AS1-1(A) | MODE0 | Pin J16, FPGA Bank 503 | DIP | Pulled-down to GND. | | S1BS1-2(B) | MODE1 | Pin H15, FPGA Bank 503 | DIP | Pulled-down to GND. | | S1CS1-3(C) | USER_CFG0 | Pin A4, FPGA Bank 66 | DIP | Pulled-down to GND. | | S1DS1-4(D) | USER_CFG1 | Pin B4, FPGA Bank 66 | DIP | Pulled-down to GND. | | S7AS7-1(A) | USER_SW7 | Pin M5, FPGA Bank 65 | DIP | Pulled-up to +1.8V_PL. | | S7BS7-2(B) | USER_SW6 | Pin M4, FPGA Bank 65 | DIP | Pulled-up to +1.8V_PL.. | | S7-3(C) | S7C | USER_SW5 | Pin J2, FPGA Bank 65 | DIP | Pulled-up to +1.8V_PL. | | S7DS7-4(D) | USER_SW4 | Pin K1, FPGA Bank 65 | DIP | Pulled-up to +1.8V_PL. | | S8AS8-1(A) | USER_SW3 | Pin L1, FPGA Bank 65 | DIP | Pulled-up to +1.8V_PL. | | S8BS8-2(B) | USER_SW2 | Pin M1, FPGA Bank 65 | DIP | Pulled-up to +1.8V_PL. | | S8CS8-3(C) | USER_SW1 | Pin P2, FPGA Bank 65 | DIP | Pulled-up to +1.8V_PL. | | S8DS8-4(D) | USER_SW0 | Pin P3, FPGA Bank 65 | DIP | Pulled-up to +1.8V_PL. |

|

...

| Scroll Title |

|---|

| anchor | Table_TS_AMR |

|---|

| title | Absolute Maximum Ratings |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Symbols | Description | Min | Max | Unit |

|---|

| VIN | Input Supply Voltage (J13) | -3.5 | 7 | V | | T_STG | Storage Temperature | -40 |

50V

|

Recommended Operating Conditions

...

| Scroll Title |

|---|

| anchor | Table_TS_ROC |

|---|

| title | Recommended Operating Conditions |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Parameter | Min | Max | Units | Reference Document |

|---|

| VIN | 4 | 5.5 | V | Schematic "POWER" (Component: LTC4365ITS8) | | T_STG | 0 | 85 | °C | Zynq Ultrascale+ Data sheet |

|

Physical Dimensions

Module size: 100 mm × 100 mm. Please download the assembly diagram for exact numbers.

...

| Scroll Title |

|---|

| anchor | Table_VCP_SO |

|---|

| title | Trenz Electronic Shop Overview |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

|

...

| Scroll Title |

|---|

| anchor | Table_RH_DCH |

|---|

| title | Document Change History |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Revision | Contributor | Description |

|---|

| Page info |

|---|

| infoType | Modified date |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| type | Flat |

|---|

|

| | Page info |

|---|

| infoType | Current version |

|---|

| prefix | v. |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| | Page info |

|---|

| infoType | Modified by |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

Technical Specifications updated | | | 2020-11-19 | v.65 | Pedram Babakhani | | -- | all | | Page info |

|---|

| infoType | Modified users |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| |

|

...