...

| Scroll Title |

|---|

| anchor | Table_OBP_CLK_GEN |

|---|

| title | Clock Generator Connections and Pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Clock Generator Pin | Signal Schematic Names | Connected to | Note |

|---|

| REFP | - | Pin 3, U43 (Oscillator) |

| | REFSEL | REFSEL | - | Pulled-up to +3.3V. | | RESETN/SYNC | CLK_GEN_RESET | Pin B5, FPGA Bank 26 | Pulled-up to +3.3V. | | EEPROMSEL | EEPROMSEL | - | Pulled-up to +3.3V. | | SDA/GPIO2 | CLK_GEN_SDA | - (Default) MIO9, FPGA Bank 500 (R185/196 required) Pin 2, J14 (Pin Header required) | Pulled-up to +3.3V. (Default) Pulled-up to +3.3V. Pulled-up to +3.3V. | | SCL/GPIO3 | CLK_GEN_SCL | - (Default) MIO8, FPGA Bank 500 (R185/196 required) Pin 3, J14 (Pin Header required) | Pulled-up to +3.3V. (Default) Pulled-up to +3.3V. Pulled-up to +3.3V. | | OE/GPIO4 | - | - | Pulled-up to +3.3V. | Y1P | CLK_Y1_P / CLK_DP_P | Pin G19, FPGA Bank 505 | 27 MHz | | Y1N | CLK_Y1_N / CLK_DP_N | Pin G20, FPGA Bank 505 | 27 MHz | Y2P | CLK_Y2_P / CLK_USB_P | Pin J19, FPGA Bank 505 | 26 MHz | | Y2N | CLK_Y2_N / CLK_USB_N | Pin J20, FPGA Bank 505 | 26 MHz | Y3P | CLK_Y3_P / CLK_PCIe_P | Pin L19, FPGA Bank 505 | 100 MHz | | Y3N | CLK_Y3_N / CLK_PCIe_N | Pin L20, FPGA Bank 505 | 100 MHz | Y4P | CLK_Y4_P / SSD_RCLK_P | Pin 55, U5 (M.2) | 100 MHz | | Y4N | CLK_Y4_N / SSD_RCLK_N | Pin 53, U5 (M.2) | 100 MHz |

|

Clock Sources

| Scroll Title |

|---|

| anchor | Table_OBP_CLK |

|---|

| title | Oscillators |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Designator | Signal Schematic Names | Connected to | Description | Frequency | Note |

|---|

| U7 | ETH_XTAL_IN | Pin 34, U6 (Ethernet PHY) | Clock for Ethernet | 25 MHz |

| | U15 | PS_CLK | Pin H14, FPGA Bank 503 | Clock for FPGA | 33 MHz |

| | U23 | USB_CLK / USB0_RCLK | Pin 26, U22 (USB PHY) | Clock for USB | 52 MHz |

| | U43 | - | Pin 5, U8 (Clock Generator) | Clock for Clock Generator | 25 MHz |

|

|

...

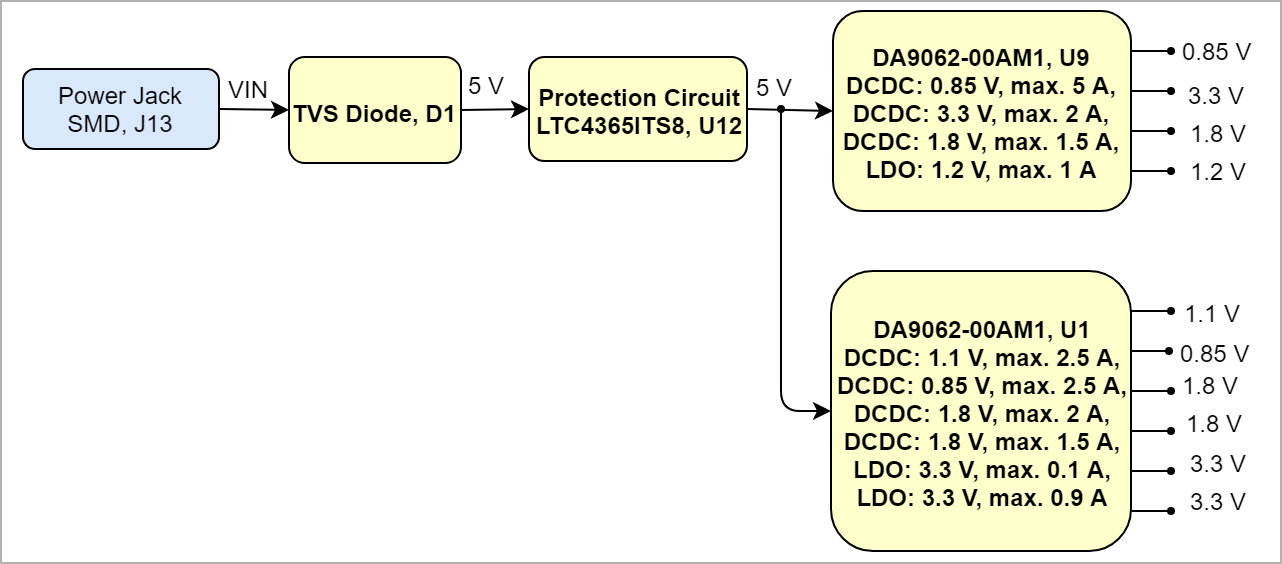

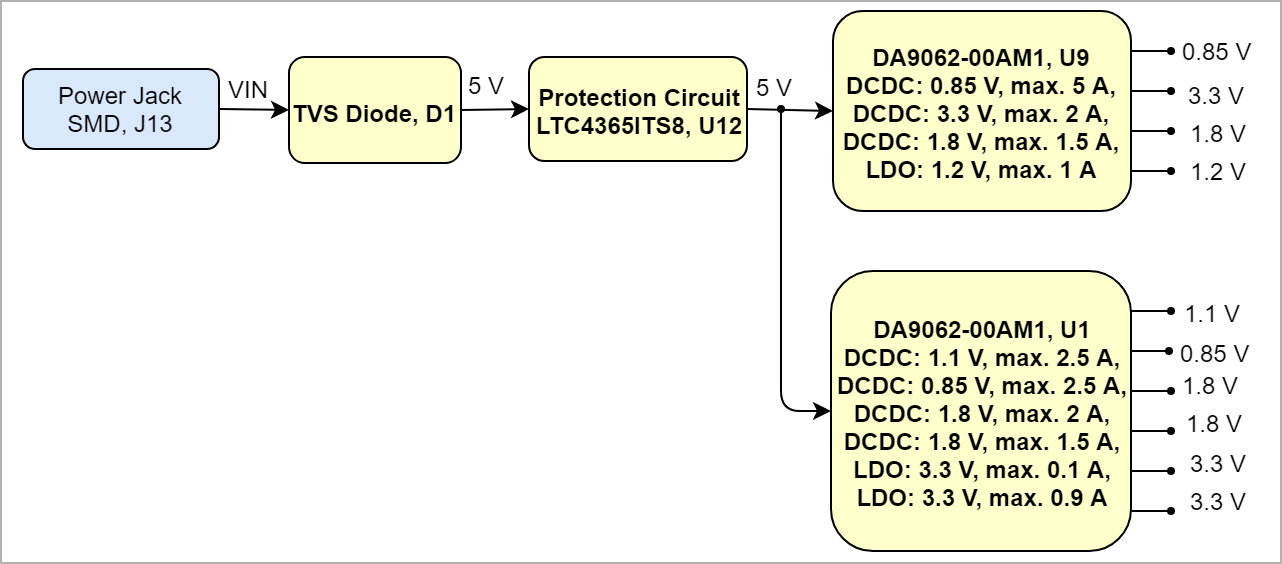

| Scroll Title |

|---|

| anchor | Figure_PWR_PD |

|---|

| title | Power Distribution |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 4 |

|---|

| diagramName | TE0802_PWR_PD |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 641 |

|---|

|

|

| Scroll Only |

|---|

Image Modified Image Modified

|

|

Power-On Sequence

...

| anchor | Figure_PWR_PS |

|---|

| title | Power Sequency |

|---|

...

There is no power sequence, regulators will be on after power on.

Power Rails

| Scroll Title |

|---|

| anchor | Table_PWR_PR |

|---|

| title | Module Power Rails |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Power Rail Name | Direction | Notes |

|---|

| VIN | IN | Supply Voltage | | +5V | Out | J1...2 | | +3.3V | Out | J14, J10 |

|

...