...

| Scroll Title |

|---|

| anchor | Table_OV_IDS |

|---|

| title | Initial delivery state of programmable devices on the module |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

Storage device name | Content | Notes |

|---|

HPS SPI Flash (U6) | Not programmed | HPS Configuration | | FPGA SPI Flash (U15) | Not programmed | FPGA Configuration | | MAC EEPROM (U38)Not | Programmed MAC programmed, otherwise not programmed | Ethernet MAC | | FTDI EEPROM (U31) | Programmed | FTDI Functionality |

|

...

| Scroll Title |

|---|

| anchor | Table_OV_BP |

|---|

| title | Boot process. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

BOOTSEL[1..0] Signal State | DIP-switch S7 position | Boot Mode | Notes |

|---|

00 | S7A - ON; S7B - ON | FPGA | Firmware dependent |

| | 01 | S7A - ON; S7B - OFF | SD | Firmware dependent |

| | 11 | S7A - OFF; S7B - OFF | SPI | Firmware dependent |

|

|

| Scroll Title |

|---|

| anchor | Table_OV_RST |

|---|

| title | Reset process. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

Reset | Button | Note |

|---|

HPS cold reset | S1 | Firmware dependent |

| | HPS warm reset | S3 | Firmware dependent |

| | FPGA reset | S4Firmware dependent |

|

|

Signals, Interfaces and Pins

...

| Scroll Title |

|---|

| anchor | Table_SIP_PMOD |

|---|

| title | Pmod connectors pin description |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Pmod Connector P1 Pin | Signal Schematic Name | Connected to Intel Cyclone V, U10 | Notes |

|---|

| 1 | P0_IO1 |

Intel Cyclone V U10, Intel Cyclone V U10, Intel Cyclone V U10, Intel Cyclone V U10, Intel Cyclone V U10, Intel Cyclone V U10, Intel Cyclone V U10, Intel Cyclone V U10, | Pin AB12 |

| | Pmod Connector P2 Pin | Signal Schematic Name | Connected to Intel Cyclone V, U10 | Notes | | 1 | P1_IO1 |

Intel Cyclone V U10, XIntel Cyclone V U10, Intel Cyclone V U10, Intel Cyclone V U10, Intel Cyclone V U10, Intel Cyclone V U10, Pin Intel Cyclone V U10, Intel Cyclone V U10, | Pin AE9 |

| | Pmod Connector P3 Pin | Signal Schematic Name | Connected to Intel Cyclone V, U10 | Notes | | 1 | P2_IO1 |

Intel Cyclone V U10, Intel Cyclone V U10, Intel Cyclone V U10, Intel Cyclone V U10, Intel Cyclone V U10, Intel Cyclone V U10, Intel Cyclone V U10, Intel Cyclone V U10, | Pin AJ1 |

| | Pmod Connector P4 Pin | Signal Schematic Name | Connected to Intel Cyclone V, U10 | Notes | | 1 | P3_IO1 |

Intel Cyclone V U10, Intel Cyclone V U10, Intel Cyclone V U10, Intel Cyclone V U10, Intel Cyclone V U10, Intel Cyclone V U10, Intel Cyclone V U10, Intel Cyclone V U10,

|

SMA Connector

The TEI0022 board offers up to seven SMA connectors for trigger and clock input and output.

...

| Scroll Title |

|---|

| anchor | Table_SIP_JTG |

|---|

| title | JTAG pins connection |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

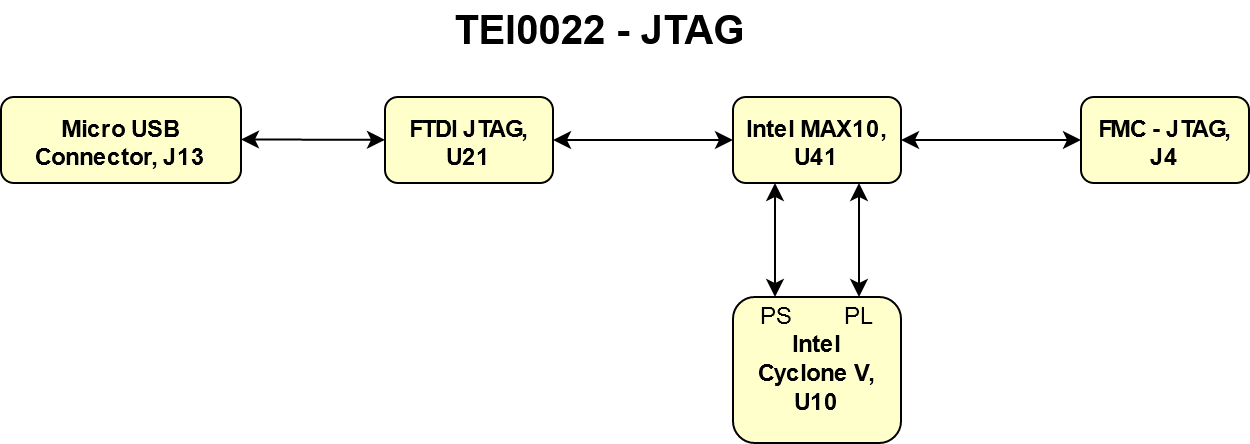

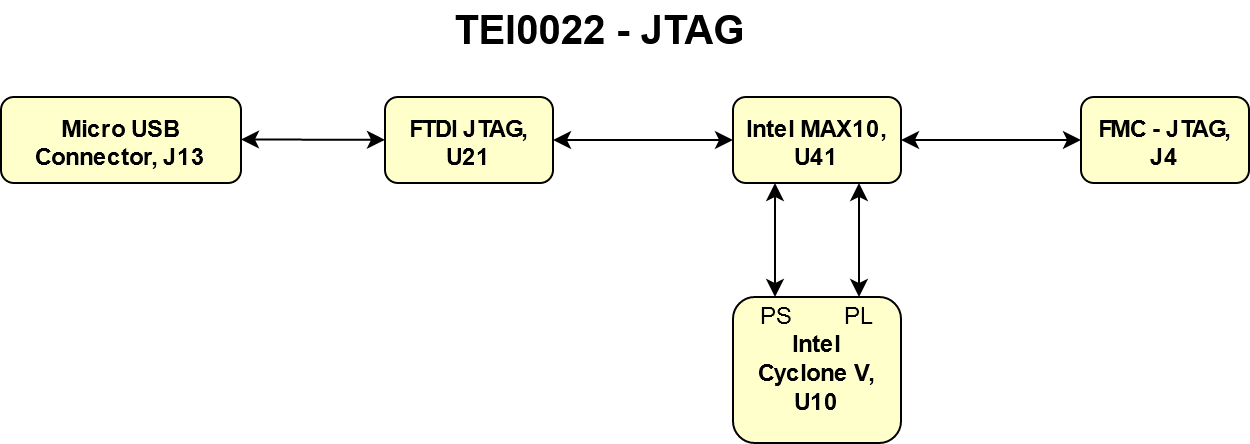

JTAGSEL1 | JTAGSEL0 | JTAGSEL1 | JTAGSEL0 | Note |

|---|

| X | X | ON | Intel MAX10 |

| | ON | ON | OFF | Intel Cyclone V HPSFirmware dependent |

| | ON | OFF | OFF | Intel Cyclone V FPGAFirmware dependent |

| | OFF | ON | OFF | FMCFirmware dependent |

|

|

| Scroll Title |

|---|

| anchor | Figure_OV_JTAG |

|---|

| title | TEI0022-01 JTAG |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | true |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 1 |

|---|

| diagramName | Figure_OC_JTAG |

|---|

| simpleViewer | true |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | top |

|---|

| diagramWidth | 641 |

|---|

|

|

| Scroll Only |

|---|

|

|

...