Page History

...

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

| Excerpt |

|---|

|

...

| Scroll Title | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

...

| Scroll Title | |||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||

|

Hardware

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

...

| Scroll Title | |||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||

|

...

| Page properties | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Notes :

|

...

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||

|

...

Reference Design is available on:

Design Flow

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

...

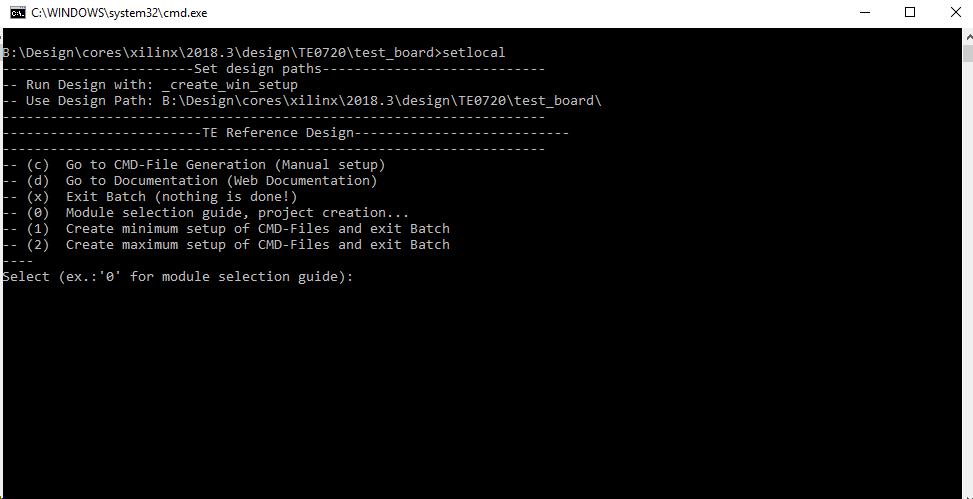

- _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

- Press 0 and enter to start "Module Selection Guide"

- (optional Win OS) Generate Virtual Drive or use short directory for the reference design (for example x:\<design name>)

- Create Project (follow instruction of the product selection guide), settings file will be configured automatically during this process

- (optional for manual changes) Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

Note: Select correct one, see TE Board Part Files

- (optional for manual changes) Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

- Create HDF and export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

- Create Linux (uboot.elf and image.ub) with exported HDFXSA

- HDF XSA is exported to "prebuilt\hardware\<short name>"

Note: HW Export from Vivado GUI create another path as default workspace. - Create Linux images on VM, see PetaLinux KICKstart

- Use TE Template from /os/petalinux

- HDF XSA is exported to "prebuilt\hardware\<short name>"

- Add Linux files (uboot.elf and image.ub) to prebuilt folder

- "prebuilt\os\petalinux\<ddr size>" or "prebuilt\os\petalinux\<short name>"

Notes: Scripts select "prebuilt\os\petalinux\<short name>", if exist, otherwise "prebuilt\os\petalinux\<DDR size>" of the selected device

- "prebuilt\os\petalinux\<ddr size>" or "prebuilt\os\petalinux\<short name>"

- Generate Programming Files with HSI/SDKVitis

- Run on Vivado TCL: TE::sw_run_

- vitis -all

Note: Depending of PC performance this can take several minutes. Scripts generate applications and bootable files, which are defined in "sw_lib\apps_list.csv" and open Vitis - (alternative) Start

- Vitis with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_

- vitis

Note:

- TCL scripts generate also platform project, this must be done manuelly in case GUI is used. See Vitis

Launch

Programming

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

...

| Code Block | ||||

|---|---|---|---|---|

| ||||

# # Constraints for System controller support logic # set_property PACKAGE_PIN K16 [get_ports PL_pin_K16] set_property PACKAGE_PIN K19 [get_ports PL_pin_K19] set_property PACKAGE_PIN K20 [get_ports PL_pin_K20] set_property PACKAGE_PIN L16 [get_ports PL_pin_L16] set_property PACKAGE_PIN M15 [get_ports PL_pin_M15] set_property PACKAGE_PIN N15 [get_ports PL_pin_N15] set_property PACKAGE_PIN N22 [get_ports PL_pin_N22] set_property PACKAGE_PIN P16 [get_ports PL_pin_P16] set_property PACKAGE_PIN P22 [get_ports PL_pin_P22] # # If Bank 34 is not 3.3V Powered need change the IOSTANDARD # set_property IOSTANDARD LVCMOS33 [get_ports PL_pin_P22] set_property IOSTANDARD LVCMOS33 [get_ports PL_pin_P16] set_property IOSTANDARD LVCMOS33 [get_ports PL_pin_N22] set_property IOSTANDARD LVCMOS33 [get_ports PL_pin_N15] set_property IOSTANDARD LVCMOS33 [get_ports PL_pin_M15] set_property IOSTANDARD LVCMOS33 [get_ports PL_pin_L16] set_property IOSTANDARD LVCMOS33 [get_ports PL_pin_K20] set_property IOSTANDARD LVCMOS33 [get_ports PL_pin_K19] set_property IOSTANDARD LVCMOS33 [get_ports PL_pin_K16] |

Software Design -

...

Vitis

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

...

For SDK project creation, follow instructions from:SDK Projects

Application

| Page properties | ||||

|---|---|---|---|---|

| ||||

---------------------------------------------------------- FPGA Example todo.. ---------------------------------------------------------- Zynq Example: zynq_fsblTE modified 2018.3 FSBL General:

Module Specific:

zynq_fsbl_flashTE modified 2018.3 FSBL General:

ZynqMP Example: ---------------------------------------------------------- zynqmp_fsblTE modified 2018.3 FSBL General:

Module Specific:

zynqmp_fsbl_flashTE modified 2018.3 FSBL General:

zynqmp_pmufwXilinx default PMU firmware. ---------------------------------------------------------- General Example: hello_te0820Hello TE0820 is a Xilinx Hello World example as endless loop instead of one console output. u-bootU-Boot.elf is generated with PetaLinux. SDK/HSI is used to generate Boot.bin. |

Template location: ./sw_lib/sw_apps/

zynq_fsbl

TE modified 20182019.3 2 FSBL

General:

- Modified Files:main.c, fsbl_hooks.h/.c (search for 'TE Mod' on source code)

Add Files: te_fsbl_hooks.h/.c(for hooks and board)\n\

- General Changes:

- Display FSBL Banner and Device ID

...

zynq_fsbl_flash

TE modified 20182019.3 2 FSBL

General:

- Modified Files: main.c

- General Changes:

- Display FSBL Banner

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

...

| Code Block | ||

|---|---|---|

| ||

#include <configs/platform-auto.h>

#define CONFIG_SYS_BOOTM_LEN 0xF000000

#define DFU_ALT_INFO_RAM \

"dfu_ram_info=" \

"setenv dfu_alt_info " \

"image.ub ram $netstart 0x1e00000\0" \

"dfu_ram=run dfu_ram_info && dfu 0 ram 0\0" \

"thor_ram=run dfu_ram_info && thordown 0 ram 0\0"

#define DFU_ALT_INFO_MMC \

"dfu_mmc_info=" \

"set dfu_alt_info " \

"${kernel_image} fat 0 1\\\\;" \

"dfu_mmc=run dfu_mmc_info && dfu 0 mmc 0\0" \

"thor_mmc=run dfu_mmc_info && thordown 0 mmc 0\0"

/*Required for uartless designs */

#ifndef CONFIG_BAUDRATE

#define CONFIG_BAUDRATE 115200

#ifdef CONFIG_DEBUG_UART

#undef CONFIG_DEBUG_UART

#endif

#endif

/*Define CONFIG_ZYNQ_EEPROM here and its necessaries in u-boot menuconfig if you had EEPROM memory. Dependencies for ENV to be stored in EEPROM. Ensure environment fits in eeprom size*/

#ifdef CONFIG_ENV_ZYNQIS_IN_EEPROM

#define CONFIG_SYS_I2C_EEPROM_ADDR_LEN 1

#define CONFIG_SYS_I2C_EEPROM_ADDR 0x54

#define CONFIG_SYS_EEPROM_PAGE_WRITE_BITS 4

#define CONFIG_SYS_EEPROM_PAGE_WRITE_DELAY_MS 5

#define CONFIG_SYS_EEPROM_SIZE 1024 /* Bytes */

#define CONFIG_SYS_I2C_MUX_ADDR 0x74

#define CONFIG_SYS_I2C_MUX_EEPROM_SEL 0x4

#endif

#define CONFIG_PREBOOT "echo U-BOOT for petalinux;echo importing env from FSBL shared area at 0xFFFFFC00; if itest *0xFFFFFC00 == 0xCAFEBABE; then echo Found valid magic; env import -t 0xFFFFFC04; fi;setenv preboot; echo; dhcp"

|

...

- CONFIG_i2c-tools=y

- CONFIG_busybox-httpd=y (for web server app)

- CONFIG_packagegroup-petalinux-utils(util-linux,cpufrequtils,bridge-utils,mtd-utils,usbutils,pciutils,canutils,i2c-tools,smartmontools,e2fsprogs)

Applications

startup

Script App to load init.sh from SD Card if available.

...

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

...