Page History

...

| Page properties | ||||

|---|---|---|---|---|

| ||||

Template Revision 1.8 9 - on construction Design Name always "TE Series Name" + optional CPLD Name + "CPLD" |

...

| HTML |

|---|

<!-- tables have all same width (web max 1200px and pdf full page(640px), flexible width or fix width on menu for single column can be used as before) -->

<style>

.wrapped{

width: 100% !important;

max-width: 1200px !important;

}

</style> |

| Scroll Only (inline) |

Online version of this manual and other related documents can be found at https://wiki.trenz-electronic.de/display/PD/SC-CPLD-Firmware |

| Scroll pdf ignore | ||||

|---|---|---|---|---|

Table of contents

|

Overview

Firmware for system controller TEI0022 Intel MAX 10 with designator U41: 10M08SAU169C8G

Feature Summary

...

- Fan Controlcontrol

- FMC Voltage Control

- JTAG Controlcontrol

- LED Controlcontrol

- UART

- User Button

- Power Management

- button

- Power management

- Power regulator mode control

- FMC Power control

- Reset management

- Configuration sheme controlReset Management

Firmware Revision and supported PCB Revision

See Document Change History

Product Specification

Port Description

| Name / opt. VHD Name | Direction | Pin | Bank Power | Description | |||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| BOOTSEL2 / BOOTSEL2 | out | L10 | +3.3V | Boot Select Bit 2 | JTAGSEL0 / JTAGSEL0HPS boot select pin 2 | ||||||

| CONF_DONE_I | in | F9L5 | +3.3V | _MAX10Select JTAG Connection | Cyclone V CONF_DONE pin | ||||||

| CPU_GPIO_0 | JTAGSEL1 / JTAGSEL1in | E9N10 | +3.3V | _MAX10Select JTAG Connection | FTDI_JTAG_TC/SK / FTDI_TCK | in | Voltage selection via software for FMC_VADJ (U43 → VS0 pin) | ||||

| CPU_GPIO_1 | in | N9 | G2+3.3V | _MAX10FTDI JTAG TCK | FTDI_JTAG_TDO/DI / FTDI_TDI | in | Voltage selection via software for FMC_VADJ (U43 → VS1 pin) | ||||

| CPU_GPIO_2 | in | N11 | F6+3.3V | _MAX10FTDI JTAG TDI | FTDI_JTAG_TMS/CS / FTDI_TMS | in | Voltage selection via software for FMC_VADJ (U43 → VS2 pin) | ||||

| CPU_GPIO_3 | in | L1 | G1+3.3V | _MAX10FTDI JTAG TCK | FMC power enable control via software | ||||||

| CPU_GPIO_4 | HPS_TDO / HPS_TDOin | J6H4 | +3.3V | HPS JTAG TDO | FPGA_TDI / FPGA_TDOFan control via software | ||||||

| BDBUS0 | in | J1D1 | +3.3V | FPGA JTAG TDO | FMC_TDO / FMC_TDO | in | _MAX10 | FTDI UART TXD pin | |||

| BDBUS1 | out | C1 | M10+3.3V | FMC JTAG TDO | FTDI_JTAG_TDI/DO / FTDI_TDO_MAX10 | FTDI UART RXD pin | |||||

| EN_0V9 | out | F5F1 | +3.3V_MAX10 | FTDI JTAG TDO | +0.9V power enable | ||||||

| EN_1V8 | HPS_TCK / HPS_TCKout | K1D12 | +3.3V | HPS JTAG TCK | HPS_TDI / HPS_TDI_MAX10 | +1.8V power enable | |||||

| EN_2V5 | out | M4A12 | +3.3V | HPS JTAG TDI | HPS_TMS / HPS_TMS_MAX10 | +2.5V power enable | |||||

| EN_3V3 | out | M7B13 | +3.3V | HPS JTAG TMS | FPGA_TCK / FPGA_TCK | out | K2_MAX10 | +3.3V | HPS JTAG TCK | FPGA_TDO / FPGA_TDIpower enable | |

| EN_5V0 | out | L2A7 | +3.3V | FPGA JTAG TDI | _MAX10 | +5.0V power enable | |||||

| EN_DDR_FPGA | FPGA_TMS / FPGA_TMSout | J2E13 | +3.3V_MAX10 | FPGA | JTAG TMSFMC_TCK/ FMC_TCKDDR power enable | ||||||

| EN_DDR_HPS | out | M8F13 | +3.3V | FMC JTAG TCK | _MAX10 | HPS DDR power enable | |||||

| EN_FMC | FMC_TDI / FMC_TDIout | M9E1 | +3.3V_MAX10 | FMC | JTAG TDIFMC_TMS /_VADJ power enable | ||||||

| EN_FMC_ | TMS3V3 | out | M11C13 | +3.3V_MAX10 | FMC JTAG TMS | HPS_RST#_SW / HPS_RSTn_SW | in | +3.3V FMC power enable | |||

| EN_FMC_12V | out | C12 | J5+3.3V | Reset Button | HPS_RST#_BO / HPS_RSTn_BO | in | _MAX10 | +12.0V FMC power enable | |||

| EN_VCC | out | A10 | K6+3.3V | Brown Out Detection | HPS_WARM_RST#_SW / HPS_WARM_RSTn_SW | in | _MAX10 | VCC power enable | |||

| FAN_EN | out | D13 | K5+3.3V | Warm Reset Button | FPGA_RST#_SW / FPGA_RSTn_SW | in | _MAX10 | Fan control | |||

| FMC_PG_C2M | out | K7 | B4+3.3V | _MAX10FPGA Reset Button | HPS_RST# / HPS_RSTn | out | FMC power good signal to FMC connector | ||||

| FMC_PRSNT_M2Cn | in | J7 | L11+3.3V | HPS Reset | |||||||

| HPS_WARM_RST# / HPS_WARM_RSTn | out | M3 | +3.3V | HPS Warm Reset | |||||||

| FMC card detection from FMC connector / currently_not_used | |||||||||||

| FPGA_GPIO_0 | out | K11 | FPGA_RST# / FPGA_RSTn | out | L13VDD_DDR_FPGA | FPGA | ResetVID0_SW / VID0_SWIO (FPGA pin AG10) / FPGA UART RXD | ||||

| FPGA_GPIO_1 | in | J10 | VDD_DDR_FPGA | FPGA IO (FPGA pin AH9) / FPGA UART TXD | |||||||

| FPGA_RSTn | out | L13 | VDD_DDR_FPGA | FPGA reset | |||||||

| FPGA_RSTn | F8 | +3.3V_MAX10 | Power Selection Pin 0 for FMC Voltage | VID1_SW / VID1_SW | in | E8B4 | +3.3V_MAX10 | Power Selection Pin 1 for FMC Voltage | VID2_SW / VID2_SW | in | FPGA reset button |

| FMC_TCK | out | M8 | D8+3.3V | _MAX10Power Selection Pin 2 for FMC Voltage | CPU_GPIO_0 / CPU_GPIO0 | in | FMC JTAG TCK | ||||

| FMC_TDI | out | M9 | N10+3.3V | CPU GPIO 0 (used for automatic power selection for FMC Voltage) | CPU_GPIO_1 / CPU_GPIO1FMC JTAG TDI | ||||||

| FMC_TDO | in | N9M10 | +3.3V | CPU GPIO 1 (used for automatic power selection for FMC Voltage) | CPU_GPIO_2 / CPU_GPIO2 | in | FMC JTAG TDO | ||||

| FMC_TMS | out | M11 | N11+3.3V | CPU GPIO 2 (used for automatic power selection for FMC Voltage) | FMC JTAG TMS | ||||||

| FPGA_TCK | VID0 / VID0out | B2K2 | +3.3V | _MAX10Power Selection Pin 0 for FMC Voltage at U43 | VID1 / VID1HPS JTAG TCK | ||||||

| FPGA_TDI | out | C2J1 | +3.3V | _MAX10Power Selection Pin 1 for FMC Voltage at U43 | VID2 / VID2 | out | F4 | FPGA JTAG TDI | |||

| FPGA_TDO | in | L2 | +3.3V | _MAX10Power Selection Pin 2 for FMC Voltage at U43 | PWR_SEL / PWR_SELFPGA JTAG TDO | ||||||

| FPGA_TMS | out | E4J2 | +3.3V | _MAX10Power Selection for Cyclone V FMC VCCPD at U37 | FPGA JTAG TMS | ||||||

| FTDI_JTAG_TCK | USER_BTN_SW / USER_BTN_SWin | B3G2 | +3.3V_MAX10 | User Button | |||||||

| USER_BTN_FPGA / USER_BTN_FPGA | out | G12 | VDD_DDR_FPGA | FPGA User Button | |||||||

| FTDI JTAG TCK | |||||||||||

| FTDI_JTAG_TDI | in | F5 | +3.3V_MAX10 | FTDI JTAG TDI | |||||||

| FTDI_JTAG_TDO | out | F6 | BDBUS0 / FTDI_RXD | in | D1+3.3V_MAX10 | FTDI | UART RXDJTAG TDO | FPGA||||

| FTDI_ | GPIO_1 / FPGA_IO1JTAG_TMS | in | J10 | VDD_DDR_FPGA | FPGA IO 1 | ||||||

| FPGA_GPIO_0 / FPGA_IO0 | out | K11 | VDD_DDR_FPGA | FPGA IO 0 | |||||||

| G1 | +3.3V_MAX10 | FTDI JTAG TMS | |||||||||

| HPS_TCK | out | K1 | +3.3V | HPS JTAG TCK | |||||||

| HPS_TDI | out | M4 | BDBUS1 / FTDI_TXD | out | C1+3.3V | _MAX10FTDI UART TXD | CPU_GPIO_4 / CPU_GPIO4HPS JTAG TDI | ||||

| HPS_TDO | in | H4J6 | +3.3V | CPU GPIO 4 (used for fan control) | HPS JTAG TDO | ||||||

| HPS_TMS | FAN_EN / FAN_ENout | D13M7 | +3.3V | _MAX10Fan Control | MODE_VCC / MODE_DCDC_VCCHPS JTAG TMS | ||||||

| HPS_RSTn | out | D9L11 | +3.3V | _MAX10VCC DCDC Mode Selection | MODE / MODE_DCDC_5V | out | HPS reset | ||||

| HPS_RSTn_BO | in | K6 | A11+3.3V | _MAX10+5.0 V DCDC Mode Selection | MODE_DDR_FPGA / MODE_DCDC_FPGA | out | Brown Out detection | ||||

| HPS_RSTn_SW | in | J5 | +3.3V | Reset button | |||||||

| HPS_WARM_RSTn | out | M3 | E10+3.3V | _MAX10FPGA DDR Power DCDC Mode Selection | MODE_DDR_HPS / MODE_DCDC_HPS | out | HPS warm reset | ||||

| HPS_WARM_RSTn_SW | in | K5 | F10+3.3V | _MAX10HPS warm reset button | |||||||

| JTAGSEL0 DDR Power DCDC Mode SelectionPG_+5.0V / PG_5V0 | in | A8F9 | +3.3V_MAX10 | +5.0 V Power Good | Select JTAG connection | ||||||

| JTAGSEL1PG_VCC / PG_VCC | in | B11E9 | +3.3V_MAX10 | VCC Power Good | PG_+2.5V / PG_2V5 | in | Select JTAG connection | ||||

| LED_1V8 | out | H2 | C11+3.3V_MAX10 | + | 2.5 V Power GoodPG_+1.8V | / PG_1V8in | power good led | ||||

| LED_FMC_VADJ | out | C9 | D11+3.3V_MAX10 | +1.8 V Power Good | PG_+3.3V / PG_3V3 | in | FMC_VADJ power good led | ||||

| LED_VCC | out | F12 | B12+3.3V_MAX10 | +3.3 V Power Good | EN_VCC / EN_VCCVCC power good led | ||||||

| LED_VDD_DDR_FPGA | out | A10E6 | +3.3V_MAX10 | VCC Power Enable | FPGA DDR VDD power good led | ||||||

| LED_VDD_DDR_HPS | EN_+2.5V / EN_2V5out | A12H3 | +3.3V_MAX10 | +2.5 V Power Enable | EN_+1.8V / EN_1V8HPS DDR VDD power good led | ||||||

| LED_VTT_DDR_FPGA | out | D12D6 | +3.3V_MAX10 | +1.8 V Power EnableFPGA DDR VTT power good led | |||||||

| LED_ | VCC / LED_VCCVTT_DDR_HPS | out | F12G4 | +3.3V_MAX10 | VCC Power Led | EN_HPS DDR VTT power good led | |||||

| MODE | out | A11 | +3.3V_MAX10 | +5.0V voltage regulator mode selection | |||||||

| MODE_DDR_FPGA | / EN_3V3out | B13E10 | +3.3V_MAX10 | +3.3 V Power Enable | EN_+0.9V / EN_0V9Voltage regulator mode selection for FPGA DDR power | ||||||

| MODE_DDR_HPS | out | F1F10 | +3.3V_MAX10 | +0.9 V Power Enable | Voltage regulator mode selection for HPS DDR power | ||||||

| MODE_VCC | LED_+1.8 V / LED_1V8out | H2D9 | +3.3V_MAX10 | VCC voltage regulator mode selection | |||||||

| MSEL0 | out | N5 | + | 1.8 V Power Led3.3V | Configuration mode selection pin 0 | ||||||

| MSEL1 | EN_DDR_HPS / EN_DDR_HPSout | F13N3 | +3.3V | _MAX10HPS DDR Power Enable | EN_DDR_FPGA / EN_DDR_FPGAConfiguration mode selection pin 1 | ||||||

| MSEL2 | out | E13N2 | +3.3V | _MAX10FPGA DDR Power Enable | CPU_GPIO_3 / CPU_GPIO3 | in | Configuration mode selection pin 2 | ||||

| MSEL3 | out | N4 | L1+3.3V | CPU GPIO 3 (used for FMC Power Enable) | Configuration mode selection pin 3 | ||||||

| MSEL4 | out | N6 | FMC_PRSNT_M2C# / FMC_PRSNT_M2Cn | in | J7 | +3.3V | FMC Card Detection from FMC Connector | EN_FMC_+12.0V / EN_FMC_12V | out | Configuration mode selection pin 4 | |

| nSTATUS_I | in | L4 | C12+3.3V | _MAX10+12.0 V FMC Power Enable | EN_FMC / EN_FMC | out | Cyclone V nSTATUS pin | ||||

| PG_1V8 | in | D11 | E1+3.3V_MAX10 | Power Enable for FMC Voltage at U43 | PWR_SWT_EN / PWR_VCCPD_EN | out | +1.8V power good signal | ||||

| PG_2V5 | in | C11 | C10+3.3V_MAX10 | Power Enable for Cyclone V VCCPD VoltageEN_FMC_ | + | 3.3V / EN_FMC2.5V power good signal | |||||

| PG_3V3 | outin | C13B12 | +3.3V_MAX10 | +3. | 3 V FMC Power EnableFMC_PG_C2M / FMC_PG_C2M | out | 3V power good signal | ||||

| PG_5V0 | in | A8 | K7+3.3V | FMC Power Good Signal to FMC Connector | POK_FMC / POK_FMC_MAX10 | +5.0V power good signal | |||||

| PG_VCC | in | E3B11 | +3.3V_MAX10 | Power Good for FMC Voltage at U43 | VCC power good signal | ||||||

| PG_VDD_FPGA | in | E12 | +3.3V_MAX10 | FPGA VDD DDR | Power Goodpower good signal | ||||||

| PG_VDD_HPS | / PG_VDD_HPSin | G10 | +3.3V_MAX10 | HPS VDD DDR | Power GoodLED_FMC_VADJ / LED_FMC_VADJ | out | power good signal | ||||

| PG_VTT_FPGA | in | B10 | C9+3.3V_MAX10 | Power Good Led for FMC Voltage at U43 | LED_VDD_DDR_FPGA / LED_VDD_DDR_FPGA | out | FPGA VTT DDR power good signal | ||||

| PG_VTT_HPS | in | B5 | E6+3.3V_MAX10 | FPGA DDR VDD Power Good Led | LED_VTT_DDR_FPGA / LED_VTT_DDR_FPGA | out | HPS VTT DDR power good signal | ||||

| POK_FMC | in | E3 | D6+3.3V_MAX10 | FPGA DDR VTT Power Good Led | LED_VDD_DDR_HPS / LED_VDD_DDR_HPSFMC_VADJ power good signal | ||||||

| PWR_SEL | out | H3E4 | +3.3V_MAX10 | HPS DDR VDD Power Good Led | LED_VTT_DDR_HPS / LED_VTT_DDR_HPS | out | Power selection pin for FMC_VCCPD voltage at U37 (Cyclone V - Bank 8A VCCPD voltage) | ||||

| PWR_SWT_EN | out | C10 | G4+3.3V_MAX10 | HPS DDR VTT Power Good Led | JTAGEN / | in | Power enable pin for FMC_VCCPD voltage at U37 | ||||

| STATUS | out | H1 | E5+3.3V_MAX10 | Select JTAG Connection | EN_+5.0V / EN_5V0status led | ||||||

| USER_BTN_FPGA | out | A7 | +3.3V_MAX10 | +5.0 V Power Enable | PG_VTT_FPGA / PG_VTT_FPGA | in | G12 | VDD_DDR_FPGA | FPGA user button pin | ||

| USER_BTN_HPS | out | M2 | +3.3V | HPS user button pin | |||||||

| USER_BTN_SW | in | B3 | B10+3.3V_MAX10 | FPGA VTT DDR Power Good | PG_VTT_HPS / PG_VTT_HPS | in/out | user button | ||||

| VID0_SW | in | F8 | B5+3.3V_MAX10 | HPS VTT DDR Power Good | STATUS / | - | Dip switch S8A for FMC_VADJ voltage selection | ||||

| VID1_SW | in | E8 | H1+3.3V_MAX10 | / currently_not_used | BDBUS2 / | - | B1 | Dip switch S8B for FMC_VADJ voltage selection | |||

| VID2_SW | in | D8 | +3.3V_MAX10 | / currently_not_used | BCBUS2 / | - | Dip switch S8C for FMC_VADJ voltage selection | ||||

| VID0 | out | B2 | A9+3.3V_MAX10 | / currently_not_used | DEVCLRn / | - | Voltage selection pin 0 (VS0) for FMC_VADJ voltage at U43 | ||||

| VID1 | out | C2 | B9+3.3V_MAX10 | / currently_not_used | BDBUS7 / | - | Voltage selection pin 1 (VS1) for FMC_VADJ voltage at U43 | ||||

| VID2 | out | F4 | A6+3.3V_MAX10 | / currently_not_used | BCBUS1 / | - | Voltage selection pin 2 (VS2) for FMC_VADJ voltage at U43 | ||||

| JTAGEN | in | E5 | B6+3.3V_MAX10 | / currently_not_used | enable/disable JTAG access to system controller MAX10 | ||||||

| BDBUS2 | BDBUS5 /- | A4B1 | +3.3V_MAX10 | / currently_not_used | |||||||

| BDBUS3 | - | A3A2 | +3.3V_MAX10 | / currently_not_used | |||||||

| BDBUS4 | - | C4A3 | +3.3V_MAX10 | / currently_not_used | |||||||

| BDBUS5 | - | C5A4 | +3.3V_MAX10 | / currently_not_used | |||||||

| BDBUS6 | - | A2A5 | +3.3V_MAX10 | / currently_not_used | BDBUS6 /|||||||

| BDBUS7 | - | A5A6 | +3.3V_MAX10 | / currently_not_used | |||||||

| CLK_MAX10 | /- | H6 | +3.3V | SI5338A → CLK2A pin / currently_not_used | ETH_RST /|||||||

| CLKSEL0 | - | G5N8 | +3.3V | Cyclone V clock select pin 0 / currently_not_used | |||||||

| USB_RSTCLKSEL1 | - | H5N7 | +3.3V | Cyclone V clock select pin 1 / currently_not_usedUSER | |||||||

| _BTN_HPS /DEVCLRn | - | M2B9 | +3.3V_MAX10 | Device-wide reset for MAX 10 / currently_not_used | |||||||

| nCONFIGETH_I /RST | - | M1G5 | +3.3V | Ethernet phy reset / currently_not_usedMSEL1 / | |||||||

| FMC_SCL | - | N3N12 | +3.3V | FMC I²C interface / currently_not_usedMSEL2 / | |||||||

| FMC_SDA | - | N2M13 | +3.3V | FMC I²C interface / currently_not_usedUSB_ | |||||||

| HUB_RST /FMC_TRST# | - | L3M12 | +3.3V | FMC JTAG test reset / currently_not_used | |||||||

| FPGA_GPIO_9 /2 | - | K10K12 | VDD_DDR_FPGA | FPGA IO (FPGA pin AF11) / currently_not_used | |||||||

| FPGA_GPIO_3 / | - | L12 | VDD_DDR_FPGA | FPGA IO (FPGA pin AG11) / currently_not_used | |||||||

| FPGA_GPIO_2 /4 | - | K12G13 | VDD_DDR_FPGA | FPGA IO (FPGA pin AA13) / currently_not_used | |||||||

| FPGA_GPIO_11 /5 | - | J12H13 | VDD_DDR_FPGA | FPGA IO (FPGA pin AB13) / currently_not_used | |||||||

| FPGA_GPIO_8 /6 | - | J9H8 | VDD_DDR_FPGA | FPGA IO (FPGA pin AK2) / currently_not_used | |||||||

| FPGA_GPIO_12 /7 | - | H10H9 | VDD_DDR_FPGA | FPGA IO (FPGA pin AK3) / currently_not_used | |||||||

| FPGA_GPIO_10 /8 | - | J13J9 | VDD_DDR_FPGA | FPGA IO (FPGA pin AJ4) / currently_not_used | |||||||

| FPGA_GPIO_5 /9 | - | H13K10 | VDD_DDR_FPGA | FPGA IO (FPGA pin AK4) / currently_not_used | |||||||

| FPGA_GPIO_7 /10 | - | H9J13 | VDD_DDR_FPGA | FPGA IO (FPGA pin AE13) / currently_not_used | |||||||

| FPGA_GPIO_6 /11 | - | H8J12 | VDD_DDR_FPGA | FPGA IO (FPGA pin AF13) / currently_not_used | |||||||

| FPGA_GPIO_4 /12 | - | G13H10 | VDD_DDR_FPGA | FPGA IO (FPGA pin AD14) / currently_not_used | |||||||

| nSTATUSHPS_SPI_I SS/BOOTSEL0 | - | L4K8 | +3.3V | HPS boot select pin 0 / currently_not_used | |||||||

| CONF_DONE_I /HPS_TRST# | - | L5M5 | +3.3V | HPS JTAG test reset / currently_not_used | |||||||

| HPSnCONFIG_TRST# /I | - | M5M1 | +3.3V | Cyclone V nCONFIG pin / currently_not_used | |||||||

| MSEL0 QSPI_CS/BOOTSEL1 | - | N5J8 | +3.3V | HPS boot select pin 1 / currently_not_usedMSEL3 / | |||||||

| USB_HUB_RST | - | N4L3 | +3.3V | USB hub (U33) reset / currently_not_usedMSEL4 / | |||||||

| USB_RST | - | N6H5 | +3.3V | / currently_not_used | CLKSEL0 / | - | N8 | +3.3V | USB phy (U8) reset / currently_not_used | ||

| CLKSEL1 / | - | N7 | +3.3V | / currently_not_used | |||||||

| FMC_TRST# / | - | M12 | +3.3V | / currently_not_used | |||||||

| FMC_SDA / | - | M13 | +3.3V | / currently_not_used | |||||||

| HPS_SPI_SS/BOOTSEL0 | - | K8 | +3.3V | / currently_not_used | |||||||

| QSPI_CS/BOOTSEL1 | - | J8 | +3.3V | / currently_not_used | |||||||

| FMC_SCL / | - | N12 | +3.3V | / currently_not_used |

Functional Description

DCDC Mode Control

The mode signals are connected to "1".

...

MODE_DCDC_VCC,

MODE_DCDC_5V

...

1

...

MODE_DCDC_FPGA,

MODE_DCDC_HPS

...

Functional Description

Fan control

Can be enabled/disabled through the Intel Cyclone V HPS "CPU_GPIO_4" pin.

JTAG control

The FTDI JTAG is connected to the Intel MAX 10, the Intel Cyclone V HPS and Fabric and to the FMC Connector according to the following table.

| JTAGSEL0 | JTAGSEL1 | JTAGEN | JTAG selection |

|---|---|---|---|

| X | X | 1 - (ON) | Intel MAX 10 |

| 0 - (ON) | 0 - (ON) | 0 - (OFF) | Cyclone V HPS |

| 0 - (ON) | 1 - (OFF) | 0 - (OFF) | Cyclone V FPGA |

| 1 - (OFF) | 0 - (ON) | 0 - (OFF) | FMC |

LED Control

| Led | Description |

|---|---|

| LED_1V8 | connected to PG_1V8 |

| LED_FMC_VADJ | connected to POK_FMC |

| LED_VCC | connected to PG_VCC |

| LED_VDD_DDR_FPGA | connected to PG_VDD_FPGA |

| LED_VDD_DDR_HPS | connected to PG_VDD_HPS |

| LED_VTT_DDR_FPGA | connected to PG_VTT_FPGA |

| LED_VTT_DDR_HPS | connected to PG_VTT_HPS |

| STATUS | Status LED (D25). Status depends on blink sequence and priority.

|

UART

UART signal are routed directly from FTDI chip through Intel MAX 10 to Cyclone V FPGA.

| FTDI FT2232H-56Q | Direction | Cyclone V FPGA |

|---|---|---|

| BDBUS0 (TXD) | → | FPGA_GPIO_0 (RXD, Pin AG10) |

| BDBUS1 (RXD) | ← | FPGA_GPIO_1 (TXD, Pin AH9) |

User button

The user button is connected to the USER_BTN_FPGA pin AB21 and USER_BTN_HPS pin A23 on the Cyclone V FPGA.

Power management

The power sequencing is handled inside the system controller according to the next figure, starting with DCDC U46 +5.0V.

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||

|

Fan Control

Can be enabled/disabled through the Intel Cyclone V HPS "CPU_GPIO4".

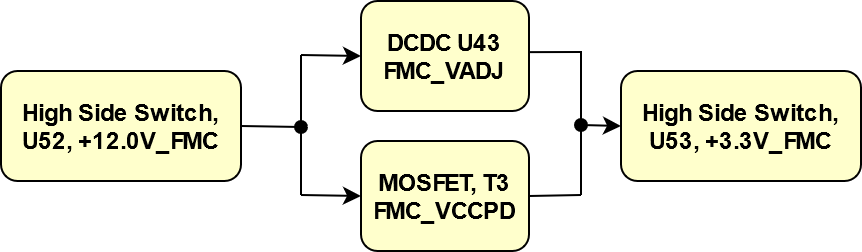

FMC Voltage Control

The power is enabled if signal "CPU_GPIO3" is set to "1" and there is an FMC card. Then, the +12.0 V level is enabled. After that, the adjustable voltage is enabled. Finally, the +3.3 V level is enabled. Then, the signal "FMC_PG_C2M" is asserted.

JTAG Control

The FTDI JTAG is connected to the Intel MAX10, the Intel Cyclone V HPS and Fabric and to the FMC Connector according to the following table.

...

LED Control

The leds signals their power good status.

UART

The second channel of the JTAG FTDI interface delievers an UART connection to the Intel Cyclone V fabric.

User Button

The User Button is connected to the FPGA.

Power Management

The power sequencing is handled inside the system controller according to the next figure.

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

The FMC power sequencing depends on the assertion through the signals "CPU_GPIO3" and "FMC_PRSNT_M2Cn". If both of them are asserted, the +12.0 V level starts, followed by the adjustabel voltage level with the according pre-driver voltage and finally, the +3.3 V level is started.

Voltage regulator mode control

| Designator | Signal | State | Description |

|---|---|---|---|

| U45 | MODE_VCC | 1 | Forced continous mode |

| U46 | MODE | 1 | Forced continous mode |

| U56 | MODE_DDR_FPGA | 1 | Pulse-skipping mode for VDD |

| U50 | MODE_DDR_HPS | 1 | Pulse-skipping mode for VDD |

For more information about possible modes see datasheet of voltage regulators.

FMC power control

The FMC adjustable voltage selection FMC_VADJ (U43) can be done by the dip switches VID0_SW (S8A), VID1_SW (S8B) and VID2_SW (S8C) or by the Intel Cyclone V HPS via CPU_GPIO_0 pin, CPU_GPIO_1 pin and CPU_GPIO_2 pin. The choice is done according to the next table.

VID2_SW (S8C)/ CPU_GPIO_2 | VID1_SW (S8B)/ CPU_GPIO_1 | VID0_SW (S8A)/ CPU_GPIO_0 | Voltage | Notes |

|---|---|---|---|---|

| ON / 0 | ON / 0 | ON / 0 | 3.3V | - |

| ON / 0 | ON / 0 | OFF / 1 | 2.5V | - |

| ON / 0 | OFF / 1 | ON / 0 | 1.8V | - |

| ON / 0 | OFF / 1 | OFF / 1 | 1.5V | - |

| OFF / 1 | ON / 0 | ON / 0 | 1.25V | - |

| OFF / 1 | ON / 0 | OFF / 1 | 1.2V | - |

| OFF / 1 | OFF / 1 | ON / 0 | 0.8V | not supported by Intel Cyclone V |

| OFF | OFF | OFF | CPU-dependent | select voltages with CPU_GPIO_0/CPU_GPIO_1/CPU_GPIO_2 pins |

The FMC power can be enabled or disabled via software with CPU_GPIO_3 pin, when the dip switches VID0_SW (S8A), VID1_SW (S8B) and VID2_SW (S8C) are set to OFF. If the FMC_VADJ voltage is selected by the dip switches, FMC power is always enabled.

The FMC power sequencing is handled as shown in the next figure.

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

The FMC adjustable voltage selection can be done manually by the switches or automatically by the Intel Cyclone V HPS. The choice is done via the switches according to the next table. The voltage for the Intel Cyclone V HPS pre-driver is selected according to the voltage setting.

...

|

Reset Management

The reset buttons are connected via the system controller to the according reset locations.

| Designator | Name | connected to | Notes |

|---|---|---|---|

| S1 | HPS_RSTn_SW | HPS_RSTn | Button |

| U54 | HPS_RSTn_BO | HPS_RSTn | Brown out detection |

| S3 | HPS_WARM_RSTn_SW | HPS_WARM_RSTn | Button |

| S4 | FPGA_RSTn_SW | FPGA_RSTn | Button |

Configuration sheme control

| MSEL4 | MSEL3 | MSEL2 | MSEL1 | MSEL0 | Configuration sheme |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 0 | FPP x16 Fast, compression feature enabled |

Appx. A: Change History and Legal Notices

Revision Changes

SC REV03 to REV04

- PCB REV03 support only

- bugfixes

- add status led control

- add USER_BTN_HPS, CONF_DONE_I, nSTATUS_I pins

SC REV02 to REV03

- bugfixes

- add configuration sheme

SC

Reset Management

The reset buttons are connected via the system controller to the according reset locations. That means that, if the reset button S1 or the brown-out detection is asserted, the Cyclone V should be reseted. If the warm reset button S3 is asserted, the Cyclone V should be warm reseted. If the FPGA reset button S4 is asserted, the FPGA could be reseted.

Appx. A: Change History and Legal Notices

Revision Changes

CPLD REV01 to REV02

- Changed pin connections

- Changed JTAG connection

- Changed reset connection

- Changed FMC Vadj Voltage selection

- Changed power sequencing

Document Change History

To get content of older revision got to "Change History" of this page and select older document revision number.

...

| Date | Document Revision | CPLD Firmware Revision | Supported PCB Revision | Authors | Description | ||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| REV04 | REV03 |

| Revision 04 release | ||||||||||||||||||||||||

| 2020-06-03 | v.9 | REV03 | REV02 | Thomas Dück | Revision 03 release | ||||||||||||||||||||||||

| 2020-02-19 | v.197 | REV02 | REV02 |

| Initial release | ||||||||||||||||||||||||

| All |

|

Legal Notices

| Include Page | ||||

|---|---|---|---|---|

|

...