Page History

...

The whole design process needs several tools, whereby output files and folders from one step are essential for the next processing step. Therefore, each step can be handled independently with its complexity if the needed files and folders are available. The usage of tools will be described in sequential order, according to the necessary path, booting the HPS. This process is described by showing the requirements in the next section. The following section displays the necessary steps withing the tool "Intel Quartus Project" (Step 1). After that, the generation of the preloader and the main bootloader from u-boot sources (Step 2) is shown, followed by the generation of the device tree blob (Step 3). Then, the SD card setup for the Intel Cycone V HPS (Step 4) is delivered and finally, references for further information are mentioned.

...

The requirements for bring-up the HPS in the Intel Cyclone V SoC consists of the following tools:

- Windows:

- Intel® Quartus® Prime Lite - Version 18.1 build 625

- Intel® Soc FPGA Embedded Development Suite (Soc EDS) - Version 18.1 build 625

- Linux

...

- :

- fdisk

- mkfs

Intel

////

This step by step guide covers the tools and console commands for Windows users. The programs and tools this guide uses

are Linux based. Intels approach for making these Linux tools accessible to Windows users is the wrapper Cygwin, because of

that, the steps and console commands in a Linux environment are nearly identical.

All required Editors and tools are part of the Intel FPGA Design software packages.

Only the SD card build requires low level access to the SD card and can therefore only be performed in native Linux environment.

////

Intel Quartus Project generation

The first step within the HPS booting procedure is using the tool "Intel Quartus Prime". Within this tool it is necessary to create a new project. After that, it is mandatory to configure the resources (system memory and SD card access) withing the Plattform Designer. After that, connect the basis interfaces (UART, I2C) of the HPS to the board resources and compile the project to create the ".sopinfo", the ".qip" files, and the "handoff" folder. Refer to "Intel Quartus project" for more detailed information.

////

- Setup a project in Quartus Prime Lite (folder: project and project name: HPSexample)

- Use the Plattform Designer to configure the resources needed to boot the HPS

(System Memory and SD card access)

- Connect the basic interfaces (Uart and i²c) of the HPS to the board resources

- Compile the project to get the required files and folders for the next steps

HPSexample.sopinfo / PlattformEditorHPS.qip file and (hps_isw_)handoff folder

////

Preloader/Bootloader generation

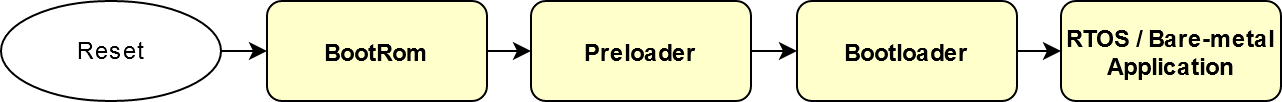

After Intel Quartus Prime project generation, it is necessary to handle System on Chip (SoC) booting. The boot process, according to the next figure, consists of several stepsstages:

- BootROM:

The BootROM is hard coded into the chip. After reset the BootROM code can detect the selected boot source and perform a minimal HPS setup. After that the preloader can be loaded into the On Chip RAM (OCRM) and can be executed.

...

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

////

[preloader-mkpimage.bin u-boot.img]

...

Device Tree Blob generation

...