Page History

...

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

Refer to http://trenz.org/te0xyztei0006-info for the current online version of this manual and other available documentation.

...

| Excerpt |

|---|

|

Revision History

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

...

| Scroll Title | ||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||

|

...

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

...

Complete List is available on <design name>/board_files/*_board_filesdevices.csv

Design supports following modules:

| Scroll Title | ||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||

|

...

| Scroll Title | ||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||

|

Content

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

For general structure and of the reference design, see Project Delivery - Xilinx Intel devices

Design Sources

| Scroll Title | |||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||

|

...

TE Scripts are only needed to generate the quartus project, all other additional steps are optional and can also executed by Intel Quartus/SDK GUI. For currently Scripts limitations on Win and Linux OS see: Project Delivery Currently limitations of functionality

- Open create_project_win.cmd/create_project_linux.sh and follow instructions in "Messages" section:

- Select board in "Board selection" section

- click Click on "Create project" button to create project

- (optional for manual changes) Select correct Quartus install path on "design_basic_settings.cmd"

Launch

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note: |

...

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

...

- XSA is exported to "prebuilt\hardware\<short name>"

Note: HW Export from Vivado GUI create another path as default workspace. - Create Linux images on VM, see PetaLinux KICKstart

- Use TE Template from /os/petalinux

...

- "prebuilt\os\petalinux\<ddr size>" or "prebuilt\os\petalinux\<short name>"

...

- Run on Vivado TCL: TE::sw_run_vitis -all

Note: Scripts generate applications and bootable files, which are defined in "sw_lib\apps_list.csv" - (alternative) Start SDK with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_vitis

Note: TCL scripts generate also platform project, this must be done manuelly in case GUI is used. See Vitis

|

Programming

| Note |

|---|

Check Module and Carrier TRMs for proper HW configuration before you try any design. |

QSPI

- Connect JTAG and power on carrier with module

- Open "create_project_win.cmd/create_project_linux.sh"

- select correct Board in "Board selection" section

- Click on "Program device" button

- (if prebuilt files are available) select "Program prebuilt file" and click on "Start program device"

- select "Program other file" and click on "Browse ..." to open own generated programming file

- (optional) click on "Open programmer GUI" to program device with Quartus programmer GUI

- Click on "Start program device"

JTAG

Not used on this Example.

Usage

- Prepare HW like described on section TEI0006 Reference Design#Programming

- Connect UART USB (most cases same as JTAG)

- Power On PCB

UART

- Open Serial Console (e.g. putty)

- Speed: 115200

- COM Port: Win OS, see device manager, Linux OS see dmesg |grep tty

- Select "Implicit CR in every LF" in category "Terminal"

- Simple Socket Server is starting up. Follow instructions on shell.

- If dhcp server is not available: open sdk project in sdk gui and change predefined IP address in simple_socket_server.h, build software project and download *.elf file to device.

- Connect your board to the network

- Open command shell and enter "telnet <ip_address> 30"

System Design - Quartus

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

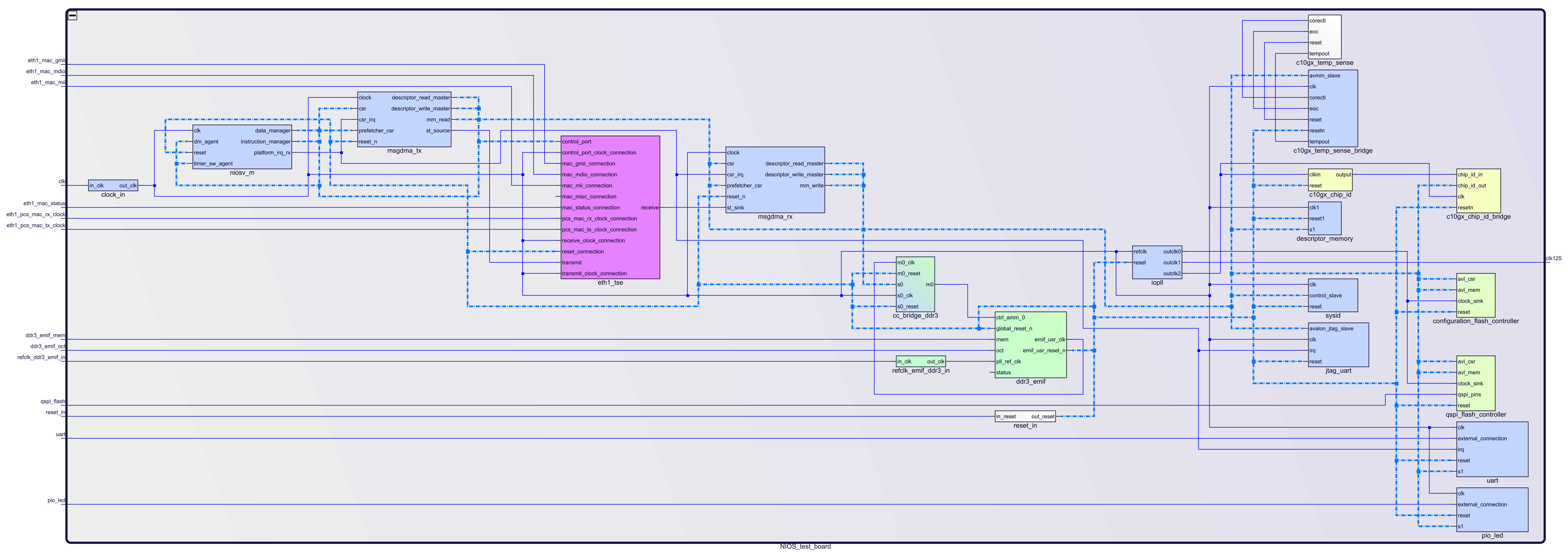

Block Design

| Scroll Title | ||||

|---|---|---|---|---|

| ||||

| Scroll Title | ||||

|---|---|---|---|---|

| ||||

Software Design - SDK

Launch

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

Programming

| Note |

|---|

Check Module and Carrier TRMs for proper HW configuration before you try any design. |

Xilinx documentation for programming and debugging: Vivado/SDK/SDSoC-Xilinx Software Programming and Debugging

Get prebuilt boot binaries

- _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell

- Press 0 and enter to start "Module Selection Guide"

- Select assembly version

- Validate selection

- Select Create and open delivery binary folder

Note: Folder (<project foler>/_binaries_<Artikel Name>) with subfolder (boot_<app name>) for different applications will be generated

QSPI

Optional for Boot.bin on QSPI Flash and image.ub on SD.

- Connect JTAG and power on carrier with module

- Open Vivado Project with "vivado_open_existing_project_guimode.cmd" or if not created, create with "vivado_create_project_guimode.cmd"

- Type on Vivado TCL Console: TE::pr_program_flash_binfile -swapp u-boot

Note: To program with SDK/Vivado GUI, use special FSBL (zynqmp_fsbl_flash) on setup

optional "TE::pr_program_flash_binfile -swapp hello_te0820" possible - Copy image.ub on SD-Card

- use files from (<project foler>/_binaries_<Articel Name>)/boot_linux from generated binary folder,see: Get prebuilt boot binaries

- or use prebuilt file location, see <design_name>/prebuilt/readme_file_location.txt

- Insert SD-Card

SD

- Copy image.ub and Boot.bin on SD-Card

- use files from (<project foler>/_binaries_<Articel Name>)/boot_linux from generated binary folder,see: Get prebuilt boot binaries

- or use prebuilt file location, see <design_name>/prebuilt/readme_file_location.txt

- Set Boot Mode to SD-Boot.

- Depends on Carrier, see carrier TRM.

- Insert SD-Card in SD-Slot.

JTAG

Not used on this Example.

Usage

- Prepare HW like described on section 43680037

- Connect UART USB (most cases same as JTAG)

- Select SD Card as Boot Mode (or QSPI - depending on step 1)

Note: See TRM of the Carrier, which is used. - Power On PCB

Note: 1. Zynq Boot ROM loads FSBL from SD into OCM, 2. FSBL loads U-boot from SD into DDR, 3. U-boot load Linux from SD into DDR

Linux

- Open Serial Console (e.g. putty)

- Speed: 115200

- COM Port: Win OS, see device manager, Linux OS see dmesg |grep tty (UART is *USB1)

- Linux Console:

Note: Wait until Linux boot finished For Linux Login use:- User Name: root

- Password: root

- You can use Linux shell now.

- I2C 0 Bus type: i2cdetect -y -r 0

- RTC check: dmesg | grep rtc

- ETH0 works with udhcpc

- USB type "lsusb" or connect USB2.0 device

- Option Features

- Webserver to get access to Zynq

- insert IP on web browser to start web interface

- init.sh scripts

- add init.sh script on SD, content will be load automatically on startup (template included in ./misc/SD)

- add init.sh script on SD, content will be load automatically on startup (template included in ./misc/SD)

- Webserver to get access to Zynq

Vivado HW Manager

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

Open Vivado HW-Manager and add VIO signal to dashboard (*.ltx located on prebuilt folder)

- Control:

- Monitoring:

...

| anchor | Figure_VHM |

|---|---|

| title | Vivado Hardware Manager |

System Design - Vivado

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

Block Design

...

| anchor | Figure_BD |

|---|---|

| title | Block Design |

PS Interfaces

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

Activated interfaces:

...

| anchor | Table_PSI |

|---|---|

| title | PS Interfaces |

...

Constrains

Basic module constrains

| Code Block | ||||

|---|---|---|---|---|

| ||||

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

set_property CFGBVS VCCO [current_design]

set_property BITSTREAM.CONFIG.USR_ACCESS TIMESTAMP [current_design] |

Design specific constrain

| Code Block | ||||

|---|---|---|---|---|

| ||||

set_property PACKAGE_PIN K2 [get_ports {fclk[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {fclk[0]}]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets fclk_IBUF[0]] |

Software Design - Vitis

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

For SDK project creation, follow instructions from:

Application

...

| hidden | true |

|---|---|

| id | Comments |

----------------------------------------------------------

FPGA Example

scu

MCS Firmware to configure SI5338 and Reset System.

srec_spi_bootloader

TE modified 2019.2 SREC

Bootloader to load app or second bootloader from flash into DDR

Descriptions:

- Modified Files: blconfig.h, bootloader.c

- Changes:

- Add some console outputs and changed bootloader read address.

- Add bugfix for 2018.2 qspi flash

xilisf_v5_11

TE modified 2019.2 xilisf_v5_11

- Changed default Flash type to 5.

----------------------------------------------------------

Zynq Example:

zynq_fsbl

TE modified 2019.2 FSBL

General:

- Modified Files:main.c, fsbl_hooks.h/.c (search for 'TE Mod' on source code)

Add Files: te_fsbl_hooks.h/.c(for hooks and board)\n\

- General Changes:

- Display FSBL Banner and Device ID

Module Specific:

- Add Files: all TE Files start with te_*

- READ MAC from EEPROM and make Address accessible by UBOOT (need copy defines on uboot platform-top.h)

- CPLD access

- Read CPLD Firmware and SoC Type

- Configure Marvell PHY

zynq_fsbl_flash

TE modified 2019.2 FSBL

General:

- Modified Files: main.c

- General Changes:

- Display FSBL Banner

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

ZynqMP Example:

----------------------------------------------------------

zynqmp_fsbl

TE modified 2019.2 FSBL

General:

- Modified Files: xfsbl_main.c, xfsbl_hooks.h/.c, xfsbl_board.h/.c(search for 'TE Mod' on source code)

- Add Files: te_xfsbl_hooks.h/.c (for hooks and board)\n\

- General Changes:

- Display FSBL Banner and Device Name

Module Specific:

- Add Files: all TE Files start with te_*

- Si5338 Configuration

- ETH+OTG Reset over MIO

zynqmp_fsbl_flash

TE modified 2019.2 FSBL

General:

- Modified Files: xfsbl_initialisation.c, xfsbl_hw.h, xfsbl_handoff.c, xfsbl_main.c

- General Changes:

- Display FSBL Banner

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

zynqmp_pmufw

Xilinx default PMU firmware.

----------------------------------------------------------

General Example:

hello_te0820

Hello TE0820 is a Xilinx Hello World example as endless loop instead of one console output.

u-boot

U-Boot.elf is generated with PetaLinux. Vitis is used to generate Boot.bin.

Template location: ./sw_lib/sw_apps/

...

Software Design - PetaLinux

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

For PetaLinux installation and project creation, follow instructions from:

Config

Start with petalinux-config or petalinux-config --get-hw-description

Changes:

- No changes.

U-Boot

Start with petalinux-config -c u-boot

Changes:

- No changes.

Change platform-top.h:

...

| language | js |

|---|

Device Tree

| Code Block | ||

|---|---|---|

| ||

/include/ "system-conf.dtsi"

/ {

};

|

Kernel

Start with petalinux-config -c kernel

Changes:

- No changes.

Rootfs

Start with petalinux-config -c rootfs

Changes:

- No changes.

Applications

See: \os\petalinux\project-spec\meta-user\recipes-apps\

startup

Script App to load init.sh from SD Card if available.

webfwu

Webserver application accemble for Zynq access. Need busybox-httpd

...

| Page properties | ||||

|---|---|---|---|---|

| ||||

| Note: |

No additional software is needed.

SI5338

File location <design name>/misc/Si5338/Si5338-*.slabtimeproj

General documentation how you work with these project will be available on Si5338

SI5345

File location <design name>/misc/Si5345/Si5345-*.slabtimeproj

General documentation how you work with these project will be available on Si5345

...

|

Application

| Page properties | ||||

|---|---|---|---|---|

| ||||

simple_socket_server

Software example "Simple Socket Server" from SDK software eclipse (modified source files for TEI0006 board).

Template location: <basefolder>/source_files/software/simple_socket_server

Document Change History

To get content of older revision got to "Change History" of this page and select older document revision number.

...

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Legal Notices

| Include Page | ||||

|---|---|---|---|---|

|

...