| Page properties |

|---|

|

Design Name is always "TE Series Name" + Design name, for example "TE0720 Test Board"

| Date | Version | Changes | Author |

|---|

2022| 2023- | 0806- | 2413 | 3.1. | 11 | ma | 16 | - Design flow:

- added alternative programming files in Petalinux

- added chapter FSBL Patch in Software Design - Petalinux

| ma | | 2023-06-01 | 2022-01-25 | 3.1. | 1015 | | QSPI-Boot mode and SD-Boot mode. Is implemented in BOOT.bincorrected Boot Source File in Boot Script-File | ma | | 2023-06-01 | 3.1.14 | - expandable lists for revision history and supported hardware

| wh | | 2023-05-25 | ma | 2022-01-14 | 3.1. | 9extended notes for microblaze boot process with linux add u.boot.dtb to petalinux notes add dtb to prebuilt content replace 20.2 with 21.2

| jh | 13 | - updated according to Vivado 2022.2

| ma | | 2023-02-08 | 2021-06-28 | 3.1. | 8added boot process for Microblazeminor typos, formatting12 | - removed content of

- Special FSBL for QSPI programming

| ma | 2021 2022- | 0608- | 0124 | 3.1. | 7 | jh | 2021-05-0411 | | ma | 2022-01-25 | 3.1. | 610 | | zynq_ from zynq_fsbl | ma | 2022-01-14 | ma | 2021-04-28 | 3.1. | 59 | extended notes for microblaze boot process with linux add u.boot.dtb to petalinux notes add dtb to prebuilt content replace 20.2 with 21.2

| jh | | 2021-06-28 | 3.1.8 | - added boot process for Microblaze

| added macro "Scroll ignore" for suppression of horizontal dividing lines during .pdf-export | ma | | 2021- | 0406- | 2701 | 3.1. | 47 | | jh | | 2021-05-04 | 3.1.6 | - removed zynq_ from zynq_fsbl

| ma | | 2021-04-28 | 3.1.5 | - added macro "Scroll ignore" for suppression of horizontal dividing lines during .pdf-export

- minor typos, formatting

| ma | | 2021-04-27 | 3.1.4 | | Version Historychanged from - Design flow

- removed step 5 from Design flow

- changed link from TE Board Part Files to Vivado Board Part Flow

- changed cmd shell from picture to codeblock

- added hidden template for "Copy PetaLinux build image files", depending from hardware

- added hidden template for "Power on PCB", depending from hardware

- Usage update of boot process

- Requirements - Hardware

- added "*used as reference" for hardware requirements

- all

- placed a horizontal separation line under each chapter heading

- changed title-alignment for tables from left to center

- all tables

- added "<project folder>\board_files" in Vivado design sources

| ma |

| 3.1.3 | | ma |

| 3.1.2 | - minor typing corrections

- replaced SDK by Vitis

- changed from / to \ for windows paths

- replaced <design name> by <project folder>

- added "" for path names

- added boot.src description

- added USB for programming

| ma |

| 3.1.1 | - swapped order from prebuilt files

- minor typing corrections

- removed Win OS path length from Design flow, added as caution in Design flow

| ma |

| 3.1 | - Fix problem with pdf export and side scroll bar

- update 19.2 to 20.2

- add prebuilt content option

|

|

| 3.0 | - add fix table of content

- add table size as macro

- removed page initial creator

|

|

|

| Page properties |

|---|

|

Important General Note: Export PDF to download, if vivado revision is changed! Designate all graphics and pictures with a number and a description, Use "Scroll Title" macro - Use "Scroll Title" macro for pictures and table labels. Figure number must be set manually at the moment (automatically enumeration is planned by scrollPDF)

- ...

|

Overview

| Scroll Ignore |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

|

|

ZynqMP PS Design with Linux Example and simple frequency counter to measure SI5338 Reference CLK with Vivado HW-Manager.

Wiki Resources page: http://trenz.org/te0823-info

Key Features

| Page properties |

|---|

|

Notes : - Add basic key futures, which can be tested with the design

|

| Excerpt |

|---|

- Vitis/Vivado 20212022.2.1

- PetaLinux

- SD

- ETH

- USB

- I2C

- RTC

- FMeter

- MAC from EEPROM

- User LED

- Modified FSBL for SI5338 programming

- Special FSBL for QSPI programming

|

Revision History

| Page properties |

|---|

|

Notes : - add every update file on the download

- add design changes on description

|

| Expand |

|---|

|

| Scroll Title |

|---|

| anchor | Table_DRH |

|---|

| title-alignment | center |

|---|

| title | Design Revision History |

|---|

| | Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Vivado | Project Built | Authors | Description |

|---|

|

202210252021.1_noprebuilt2021192022102511045220230920091958.zip

TE0823-test_board_noprebuilt-vivado_ |

|

20211920221025110452| 20230920091958.zip | Manuela Strücker | |

|

2021.1script update | 2021-10-27 | 2020.2 | TE0823-test_board_noprebuilt-vivado_ |

|

202082021102709481420221108082219.zip

TE0823-test_board-vivado_ |

|

2020820211027094802Mohsen Chamanbaz/John Hartfiel | - replace 19.2 fsbl template with 20.2

- new variants

| | Manuela Strücker | - bugfix uncomment block design modifications in mod_bd.tcl

- added jtag2axi for test purposes

| | 2022-10-25 | 2021.2.1 |

|

2021-08-24 | 2020.2 | TE0823-test_board_noprebuilt-vivado_ |

|

202072021082410395220221025110452.zip

TE0823-test_board-vivado_ |

|

2020720210824103936Mohsen Chamanbaz | | Manuela Strücker | Release Vivado 2021.2.1 script update

|

|

startup application addedwebfwu application added0817| 27 | 2020.2 | TE0823-test_board_noprebuilt-vivado_2020.2-build_ |

|

72021081711350720211027094814.zip

TE0823-test_board-vivado_2020.2-build_ |

|

720210817113435| 20211027094802.zip | Mohsen Chamanbaz |

|

| | /John Hartfiel | - replace 19.2 fsbl template with 20.2

- new variants

| | 2021-08-24 | 2020 |

|

2020-03-16 | 2019| .2 | TE0823-test_board_noprebuilt-vivado_ |

|

201982020031616315020210824103952.zip

TE0823-test_board |

|

_noprebuilt2019820200316163202John Hartfiel | |

Release Notes and Know Issues

| Page properties |

|---|

|

Notes :- add known Design issues and general notes for the current revision

- do not delete known issue, add fixed version time stamp if issue fixed

|

| Mohsen Chamanbaz | - startup application added

- webfwu application added

| | 2021-08-17 | 2020.2 | TE0823-test_board_noprebuilt-vivado_2020.2-build_7_20210817113507.zip

TE0823-test_board-vivado_2020.2-build_7_20210817113435.zip | Mohsen Chamanbaz | | | 2020-03-16 | 2019.2 | TE0823-test_board-vivado_2019.2-build_8_20200316163150.zip

TE0823-test_board_noprebuilt-vivado_2019.2-build_8_20200316163202.zip | John Hartfiel | |

|

|

Release Notes and Know Issues

| Page properties |

|---|

|

Notes :- add known Design issues and general notes for the current revision

- do not delete known issue, add fixed version time stamp if issue fixed

|

| Scroll Title |

|---|

| anchor | Table_KI |

|---|

| title-alignment | center |

|---|

| title | Known Issues |

|---|

|

|

| Scroll Title |

|---|

| anchor | Table_KI |

|---|

| title-alignment | center |

|---|

| title | Known Issues |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Issues | Description | Workaround | To be fixed version |

|---|

| Xilinx Software | Incompatibility of board files for ZynqMP with eMMC activated for Vivado versions below/equal to 2021.2 and 2021.2.1 patch, see Xilinx Forum Request | use corresponding board files for the Vivado versions | -- |

|

Requirements

Software

| Page properties |

|---|

|

Notes : - list of software which was used to generate the design

|

| Scroll Title |

|---|

| anchor | Table_SW |

|---|

| title-alignment | center |

|---|

| title | Software |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Software | Version | Note |

|---|

| Vitis | 20212022.2.1 | needed

Vivado is included into Vitis installation | | PetaLinux | 20212022.2 | needed | | SI ClockBuilder Pro | --- | optional |

|

Hardware

| Page properties |

|---|

|

Notes : - list of hardware which was used to generate the design

- mark the module and carrier board, which was used tested with an *

|

Basic description of TE Board Part Files is available on TE Board Part Files.

Complete List is available on "<project folder>\board_files\*_board_files.csv"

Design supports following modules:

| Expand |

|---|

|

| Scroll Title |

|---|

| anchor | Table_HWM |

|---|

| title-alignment | center |

|---|

| title | Hardware Modules |

|---|

| | Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Module Model | Board Part Short Name | PCB Revision Support | DDR | QSPI Flash | EMMC | Others | Notes |

|---|

| TE0823-01-3PIU1FL | 3cg_1li_1gb | REV01 | 1GB | 128MB | 8GB | NA | Low Profile Connector | | TE0823-01-3PIU1FA | 3cg_1li_1gb | REV01 | 1GB | 128MB | 8GB | NA | NA | | TE0823-01-S001 | 3cg_1li_2gb | REV01 | 2GB | 128MB | 8GB | NA | Custom, AN:3PI?1FA | | TE0823-01-3PIU1ML | 3cg_1li_1gb | REV01 | 1GB | 128MB | 8GB | NA | Low Profile Connector, other emmC Manuf. | | TE0823-01-3PIU1MA | 3cg_1li_1gb | REV01 | 1GB | 128MB | 8GB | NA | other emmC Manuf. | | TE0823-01-S002 | 3cg_1li_2gb | REV01 | 2GB | 128MB | 8GB | NA | Custom, other emmC Manuf., AN:3PI?1FA | | TE0823-01-3PIU1MAZ | 3cg_1li_1gb | REV01 | 1GB | 128MB | 8GB | NA | other emmC Manuf. | | TE0823-01-S003 | 3cg_1li_2gb | REV01 | 2GB | 128MB | 8GB | NA | Custom, other emmC Manuf., AN:3PI?1FA |

*used as reference |

|

Design supports following carriers:

| Scroll Title |

|---|

| anchor | Table_HWC |

|---|

| title-alignment | center |

|---|

| title | Hardware Carrier |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Carrier Model | Notes |

|---|

| TE0701 | | | TE0703* | - Important: See restrictions on usage with 7 Serie Carriers: 4 x 5 cm carriers

- Used as reference carrier.

| | TE0705 | | | TE0706 | | | TEBA0841 | - Important: See restrictions on usage with 7 Serie Carriers: 4 x 5 SoM Carriers

- No SD Slot available, pins goes to Pin Header

- For TEBA0841 REV01, please contact TE support

| | TEF1001TEF1002 | |

*used as reference |

Additional HW Requirements:

| Scroll Title |

|---|

| anchor | Table_AHW |

|---|

| title-alignment | center |

|---|

| title | Additional Hardware |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Additional Hardware | Notes |

|---|

| USB Cable for JTAG/UART | Check Carrier Board and Programmer for correct typtype | | XMOD Programmer | Carrier Board dependent, only if carrier has no own FTDI | | Cooler | It's recommended to use cooler on ZynqMP device |

*used as reference |

Content

For general structure and of the reference design, see Project Delivery - Xilinx AMD devices

Design Sources

| Scroll Title |

|---|

| anchor | Table_DS |

|---|

| title-alignment | center |

|---|

| title | Design sources |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Type | Location | Notes |

|---|

Vivado | <project folder>\block_design

<project folder>\constraints

<project folder>\ip_lib

<project folder>\board_files | Vivado Project will be generated by TE Scripts | Vitis | <project folder>\sw_lib | Additional Software Template for Vitis and apps_list.csv with settings automatically for Vitis app generation | PetaLinux | <project folder>\os\petalinux | PetaLinux template with current configuration |

|

Additional Sources

| Scroll Title |

|---|

| anchor | Table_ADS |

|---|

| title-alignment | center |

|---|

| title | Additional design sources |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Type | Location | Notes |

|---|

SI5338 | <project folder>\misc\PLL\Si5338 | SI5338 Project with current PLL Configuration | init.sh | <project folder>\misc\sd | Additional Initialization Script for Linux |

|

Prebuilt

| Page properties |

|---|

|

Notes : prebuilt files Template Table:

| Scroll Title |

|---|

| anchor | Table_PF |

|---|

| title-alignment | center |

|---|

| title | Prebuilt files |

|---|

| | Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

File | File-Extension | Description |

|---|

| BIF-File | *.bif | File with description to generate Bin-File | | BIN-File | *.bin | Flash Configuration File with Boot-Image (Zynq-FPGAs) | | BIT-File | *.bit | FPGA (PL Part) Configuration File | | Boot Script-File | *.scr | Distro Boot Script file | | DebugProbes-File | *.ltx | Definition File for Vivado/Vivado Labtools Debugging Interface | Debian SD-Image | *.img | Debian Image for SD-Card | | Diverse Reports | --- | Report files in different formats | | Device Tree | *.dts | Device tree (2 possible, one for u-boot and one for linux) | | Hardware-Platform-Description-File | *.xsa | Exported Vivado hardware description file for Vitis and PetaLinux | | LabTools Project-File | *.lpr | Vivado Labtools Project File | MCS-File | *.mcs | Flash Configuration File with Boot-Image (MicroBlaze or FPGA part only) | MMI-File | *.mmi | File with BRAM-Location to generate MCS or BIT-File with *.elf content (MicroBlaze only) | | OS-Image | *.ub | Image with Linux Kernel (On Petalinux optional with Devicetree and RAM-Disk) | | Software-Application-File | *.elf | Software Application for Zynq or MicroBlaze Processor Systems | SREC-File | *.srec | Converted Software Application for MicroBlaze Processor Systems |

|

|

| Scroll Title |

|---|

| anchor | Table_PF |

|---|

| title-alignment | center |

|---|

| title | Prebuilt files (only on ZIP with prebult content) |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

File | File-Extension | Description |

|---|

| BIF-File | *.bif | File with description to generate Bin-File | | BIN-File | *.bin | Flash Configuration File with Boot-Image (Zynq-FPGAs) | | BIT-File | *.bit | FPGA (PL Part) Configuration File | | Boot Script-File | *.scr | Distro Boot Script file | | DebugProbes-File | *.ltx | Definition File for Vivado/Vivado Labtools Debugging Interface | | Diverse Reports | --- | Report files in different formats | | Device Tree | *.dts | Device tree (2 possible, one for u-boot and one for linux) | | Hardware-Platform-Description-File | *.xsa | Exported Vivado hardware description file for Vitis and PetaLinux | | LabTools Project-File | *.lpr | Vivado Labtools Project File | | OS-Image | *.ub | Image with Linux Kernel (On Petalinux optional with Devicetree and RAM-Disk) | | Software-Application-File | *.elf | Software Application for Zynq or MicroBlaze Processor Systems |

|

Download

Reference Design is only usable with the specified Vivado/Vitis/PetaLinux version. Do never use different Versions of Xilinx Software for the same Project.

Reference Design is available on:

Design Flow

| Scroll Ignore |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

|

|

| Note |

|---|

Reference Design is available with and without prebuilt files. It's recommended to use TE prebuilt files for first launch. |

Trenz Electronic provides a tcl based built environment based on Xilinx Design Flow.

See also:

The Trenz Electronic FPGA Reference Designs are TCL-script based project. Command files for execution will be generated with "_create_win_setup.cmd" on Windows OS and "_create_linux_setup.sh" on Linux OS.

TE Scripts are only needed to generate the vivado project, all other additional steps are optional and can also executed by Xilinx Vivado/SDK GUI. For currently Scripts limitations on Win and Linux OS see: Project Delivery Currently limitations of functionality

| Note |

|---|

Caution! Win OS has a 260 character limit for path lengths which can affect the Vivado tools. To avoid this issue, use Virtual Drive or the shortest possible names and directory locations for the reference design (for example "x:\<project folder>") |

Run _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

| Code Block |

|---|

| language | bash |

|---|

| theme | Midnight |

|---|

| title | _create_win_setup.cmd/_create_linux_setup.sh |

|---|

|

------------------------Set design paths----------------------------

-- Run Design with: _create_win_setup

-- Use Design Path: <absolute project path>

--------------------------------------------------------------------

-------------------------TE Reference Design---------------------------

--------------------------------------------------------------------

-- (0) Module selection guide, project creation...prebuilt export...

-- (1) Create minimum setup of CMD-Files and exit Batch

-- (2) Create maximum setup of CMD-Files and exit Batch

-- (3) (internal only) Dev

-- (4) (internal only) Prod

-- (c) Go to CMD-File Generation (Manual setup)

-- (d) Go to Documentation (Web Documentation)

-- (g) Install Board Files from Xilinx Board Store (beta)

-- (a) Start design with unsupported Vivado Version (beta)

-- (x) Exit Batch (nothing is done!)

----

Select (ex.:'0' for module selection guide): |

- Press 0 and enter to start "Module Selection Guide"

- Createproject and follow instructions of the product selection guide, settings file will be configured automatically during this process.

Create hardware description file (.xsa file) for PetaLinux project and export to prebuilt folder

| Code Block |

|---|

| language | py |

|---|

| theme | Midnight |

|---|

| title | run on Vivado TCL (Script generates design and export files into "<project folder>\prebuilt\hardware\<short name>") |

|---|

|

TE::hw_build_design -export_prebuilt |

| Info |

|---|

Using Vivado GUI is the same, except file export to prebuilt folder. |

- Create and configure your PetaLinux project with exported .xsa-file, see PetaLinux KICKstart

- use TE Template from "<project folder>\os\petalinux"

use exported .xsa file from "<project folder>\prebuilt\hardware\<short name>" . Note: HW Export from Vivado GUI creates another path as default workspace.

The build images are located in the "<plnx-proj-root>/images/linux" directory

- Configure the boot.scr file as needed, see Distro Boot with Boot.scr

- Generate Programming Files with Vitis (recommended)

- Copy PetaLinux build image files to prebuilt folder

u-boot

system

dtb

, bl31.elf and boot.

, u-boot.dtb- , system.dtb, image.ub and boot.scr from "<plnx-proj-root>/images/linux" to prebuilt folder

for ZynqMP

|

u-boot.dtb, - system.dtb, bl31.elf, image.ub and boot.scr from "<plnx-proj-root>/images/linux" to prebuilt folder

for Microblaze |

Generate - Generate Programming Files with Vitis

| Code Block |

|---|

| language | py |

|---|

| theme | Midnight |

|---|

| title | run on Vivado TCL (Script generates applications and bootable files, which are defined in "test_board\sw_lib\apps_list.csv") |

|---|

|

TE::sw_run_vitis -all

TE::sw_run_vitis (optional; Start Vitis from Vivado GUI or start with TE Scripts on Vivado TCL) |

| Note |

|---|

TCL scripts generate also platform project, this must be done manually in case GUI is used. See Vitis |

- Generate Programming Files with Petalinux (alternative), see PetaLinux KICKstart

Launch

| Scroll Ignore |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

|

|

| Page properties |

|---|

|

Note: - Programming and Startup procedure

|

Programming

| Note |

|---|

Check Module and Carrier TRMs for proper HW configuration before you try any design. Reference Design is also available with prebuilt files. It's recommended to use TE prebuilt files for first launch. |

Xilinx documentation for programming and debugging: Vivado/Vitis/SDSoC-Xilinx Software Programming and Debugging

Note: Depending on CPLD Firmware and Boot Mode settings, QSPI boot with Linux image on SD or complete SD Boot is possible.

Get prebuilt boot binaries

- Run _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell

- Press 0 and enter to start "Module Selection Guide"

- Select assembly version

- Validate selection

Select Create and open delivery binary folder

| Info |

|---|

Note: Folder "<project folder>\_binaries_<Article Name>" with subfolder "boot_<app name>" for different applications will be generated |

QSPI-Boot mode

Option for Boot.bin on QSPI Flash and image.ub and boot.scr on SD or USB.

- Connect JTAG and power on carrier with module

Open Vivado Project with "vivado_open_existing_project_guimode.cmd" or if not created, create with "vivado_create_project_guimode.cmd"

| Code Block |

|---|

| language | py |

|---|

| theme | Midnight |

|---|

| title | run on Vivado TCL (Script programs BOOT.bin on QSPI flash) |

|---|

|

TE::pr_program_flash -swapp u-boot

TE::pr_program_flash -swapp hello_te0823 (optional) |

| Note |

|---|

To program with Vitis/Vivado GUI, use special FSBL (fsbl_flash) on setup |

- Copy image.ub and boot.scr on SD or USB

- use files from "<project folder>\_binaries_<Article Name>\boot_linux" from generated binary folder,see: Get prebuilt boot binaries

- or use prebuilt file location, see "<project folder>\prebuilt\file_location.txt"

- Set Boot Mode to QSPI-Boot and insert SD or USB.

- Depends on Carrier, see carrier TRM.

SD-Boot mode

- Copy image.ub, boot.src and Boot.bin on SD

- use files from "<project folder>\_binaries_<Article Name>\boot_linux" from generated binary folder, see: Get prebuilt boot binaries

- or use prebuilt file location, see "<project folder>\prebuilt\file_location.txt"

- Set Boot Mode to SD-Boot.

- Depends on Carrier, see carrier TRM.

- Insert SD-Card in SD-Slot.

JTAG

Not used on this Example.

Usage

- Prepare HW like described on section Programming

- Connect UART USB (most cases same as JTAG)

Select SD Card or QSPI as Boot Mode (Depends on used programming variant)

| Info |

|---|

Note: See TRM of the Carrier, which is used. |

| Tip |

|---|

Starting with Petalinux version 2020.1, the industry standard "Distro-Boot" boot flow for U-Boot was introduced, which significantly expands the possibilities of the boot process and has the primary goal of making booting much more standardised and predictable.

The boot options described above describe the common boot processes for this hardware; other boot options are possible.

For more information see Distro Boot with Boot.scr |

Power On PCB

| Expand |

|---|

|

1. ZynqMP Boot ROM loads PMU Firmware and FSBL from SD/QSPI Flash into OCM 2. FSBL init PS, programs PL using the bitstream and loads U-boot from SD into DDR, 3. U-boot loads Linux (image.ub) from SD/QSPI/... into DDR |

| Page properties |

|---|

|

This step depends on Xilinx Device/Hardware for Zynq-7000 series 1. Zynq Boot ROM loads FSBL from SD/QSPI into OCM, 2. FSBL init the PS, programs the PL using the bitstream and loads U-boot from SD/QSPI into DDR, 3. U-boot loads Linux (image.ub) from SD/QSPI/... into DDR

for ZynqMP??? 1. ZynqMP Boot ROM loads FSBL from SD/QSPI into OCM, 2. FSBL init the PS, programs the PL using the bitstream and loads PMU, ATF and U-boot from SD/QSPI into DDR, 3. U-boot loads Linux (image.ub) from SD/QSPI/... into DDR

for Microblaze 1. FPGA Loads Bitfile from Flash, 2. MCS Firmware configure SI5338 and starts Microblaze, 3. SREC Bootloader from Bitfile Firmware loads U-Boot into DDR (This takes a while), 4. U-boot loads Linux from QSPI Flash into DDR

for native FPGA

... |

Linux

- Open Serial Console (e.g. putty)

- Speed: 115200

Select COM Port

| Info |

|---|

Win OS, see device manager, Linux OS see dmesg |grep tty (UART is *USB1) |

Linux Console:

| Code Block |

|---|

| language | bash |

|---|

| theme | Midnight |

|---|

|

# password default disabled with 2021.2 petalinux release

petalinux login: root

Password: root |

| Info |

|---|

Note: Wait until Linux boot finished |

You can use Linux shell now.

| Code Block |

|---|

| language | bash |

|---|

| theme | Midnight |

|---|

|

i2cdetect -y -r 0 (check I2C 0 Bus)

dmesg | grep rtc (RTC check)

udhcpc (ETH0 check)

lsusb (USB check) |

Option Features

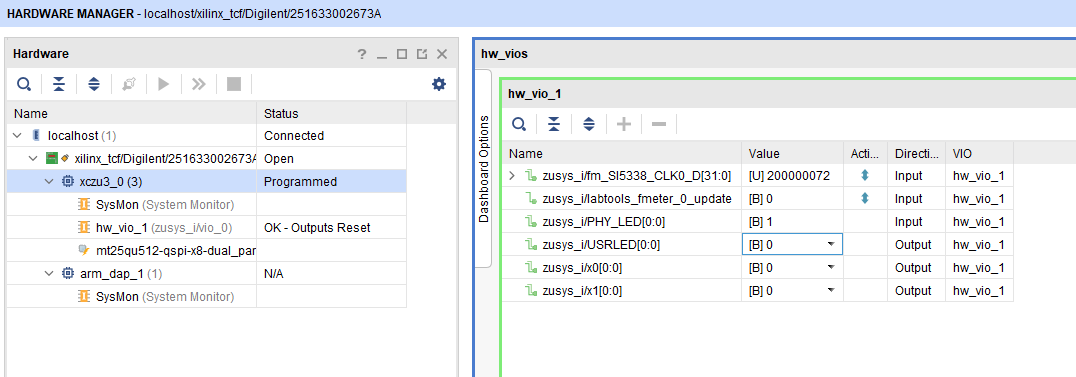

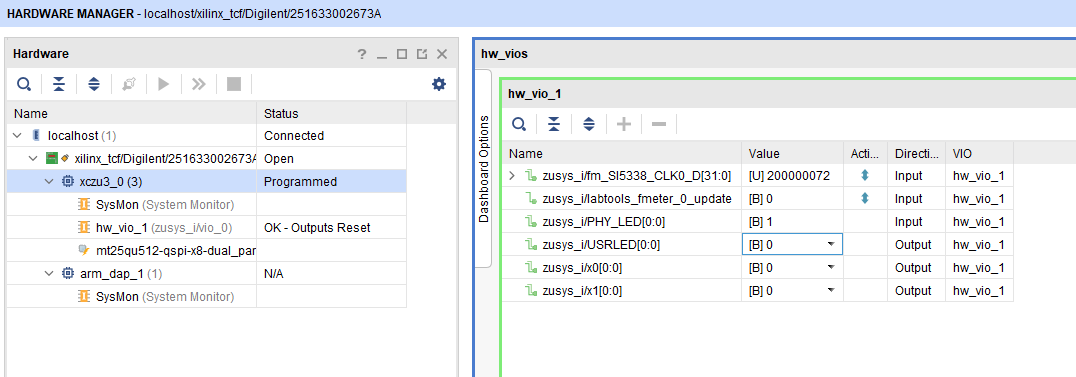

Vivado HW Manager

Open Vivado HW-Manager and add VIO signal to dashboard (*.ltx located on prebuilt folder).Control:

- GTR Power: set X0=0 and X1=1 to disable GTR Power

- USER LED: On/OFF

Monitoring:

- SI5338_CLK0 Counter: 200MHz with example Design

- Set radix from VIO signals to unsigned integer.

Note: Frequency Counter is inaccurate and displayed unit is Hz

- ETH PHY LEDs

| Scroll Title |

|---|

| anchor | Figure_VHM |

|---|

| title-alignment | center |

|---|

| title | Vivado Hardware Manager |

|---|

|

|

System Design - Vivado

| Scroll Ignore |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

|

|

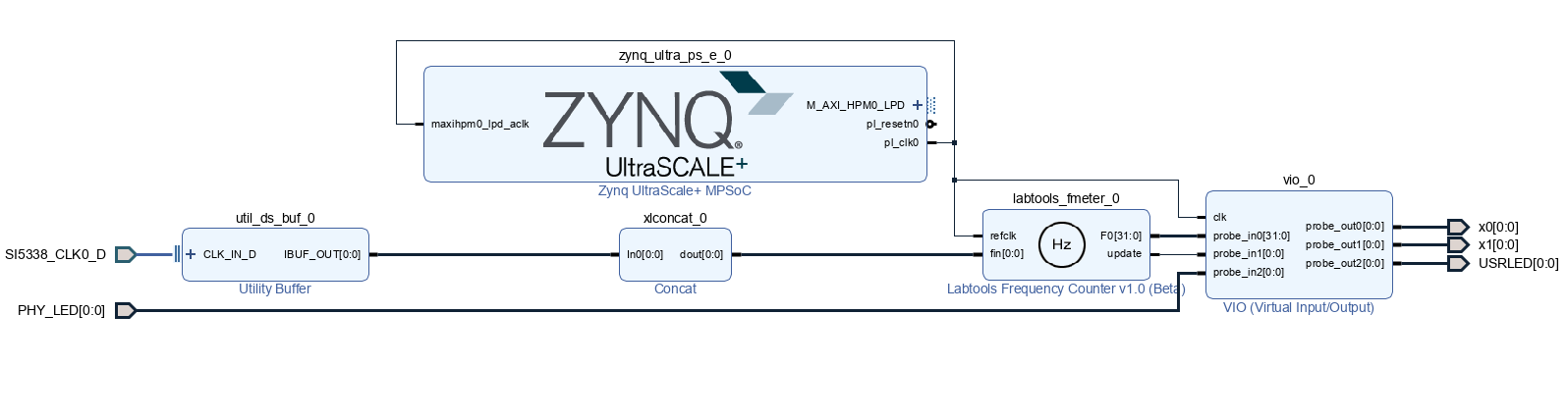

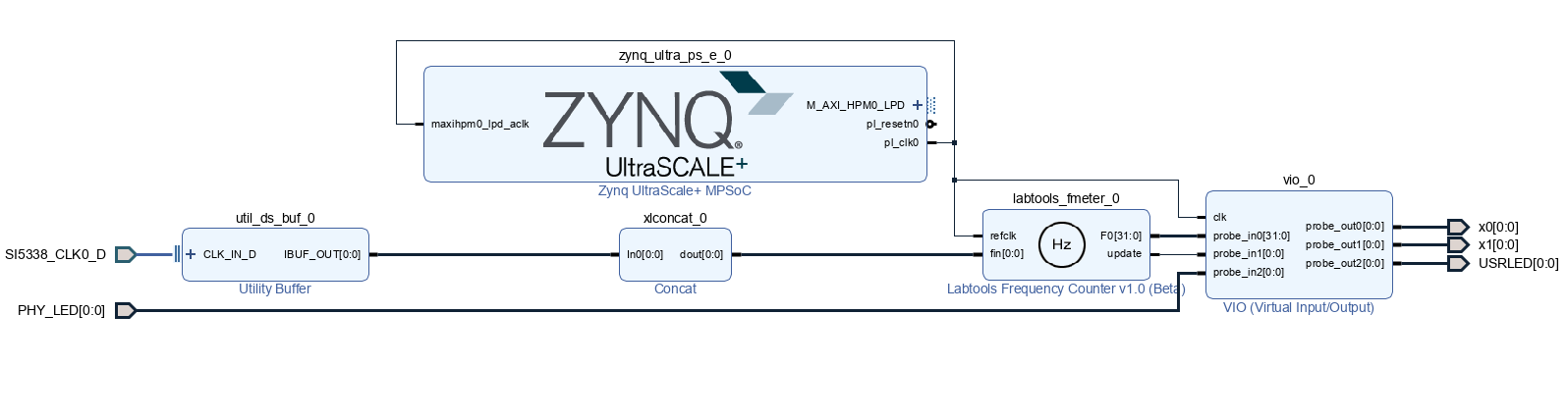

Block Design

| Scroll Title |

|---|

| anchor | Figure_BD |

|---|

| title-alignment | center |

|---|

| title | Block Design |

|---|

|

Image Removed Image Removed

|

PS Interfaces

| border | true |

|---|

| |

|---|

| diagramName | TE0823_block_design |

|---|

| simpleViewer | false |

|---|

| width | 1000 |

|---|

| links | auto |

|---|

| tbstyle | top |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| diagramWidth | 1369 |

|---|

| revision | 1 |

|---|

|

|

PS Interfaces

Activated interfaces:

| Scroll Title |

|---|

| anchor | Table_PSI |

|---|

| title-alignment | center |

|---|

| title | PS Interfaces |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Type | Note |

|---|

| DDR |

| | QSPI | MIO | | SD0 | MIO | | SD1 | MIO | | I2C0 | MIO | | UART0 | MIO | | GPIO0 | MIO | | SWDT0..1 |

| | TTC0..3 |

| | GEM3 | MIO | | USB0 | MIO, USB2 only |

|

Constrains

Basic module constrains

| Code Block |

|---|

| language | ruby |

|---|

| title | _i_bitgen_common.xdc |

|---|

|

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property BITSTREAM.CONFIG.UNUSEDPIN PULLNONE [current_design |

Design specific constrain

| Code Block |

|---|

| language | ruby |

|---|

| title | _i_io.xdc |

|---|

|

set_property PACKAGE_PIN K9 [get_ports {SI5338_CLK0_D_clk_p[0]}]

set_property IOSTANDARD LVDS [get_ports {SI5338_CLK0_D_clk_p[0]}]

set_property DIFF_TERM TRUE [get_ports {SI5338_CLK0_D_clk_p[0]}]

set_property PACKAGE_PIN B13 [get_ports {x0[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {x0[0]}]

set_property PACKAGE_PIN B14 [get_ports {x1[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {x1[0]}]

set_property PACKAGE_PIN C13 [get_ports {PHY_LED[0]}]

set_property PACKAGE_PIN C14 [get_ports {PHY_LED[1]}]

set_property IOSTANDARD LVCMOS18 [get_ports {PHY_LED*}]

set_property PACKAGE_PIN A15 [get_ports {USRLED[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {USRLED*}]

set_property PACKAGE_PIN B14 [get_ports {x1[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {x1[0]}] |

Software Design - Vitis

| Scroll Ignore |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

|

|

For Vitis project creation, follow instructions from:

Vitis

Application

| Page properties |

|---|

|

---------------------------------------------------------- FPGA Example ---------------------------------------------------------- scuMCS Firmware to configure SI5338 and Reset System. srec_spi_bootloaderTE modified 20212022.2 SREC Bootloader to load app or second bootloader from flash into DDR Descriptions: - Modified Files: blconfig.h, bootloader.c

- Changes:

- Add some console outputs and changed bootloader read address.

- Add bugfix for 2018.2 qspi flash

xilisf_v5_11TE modified 20212022.2 xilisf_v5_11 - Changed default Flash type to 5.

---------------------------------------------------------- Zynq Example: ---------------------------------------------------------- fsblTE modified 20212022.2 FSBL General: Module Specific: - Add Files: all TE Files start with te_*

- READ MAC from EEPROM and make Address accessible by UBOOT (need copy defines on uboot platform-top.h)

- CPLD access

- Read CPLD Firmware and SoC Type

- Configure Marvell PHY

fsbl_flashTE modified 2021.2 FSBL General: - Modified Files: main.c

- General Changes:

- Display FSBL Banner

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

ZynqMP Example:

---------------------------------------------------------- ZynqMP Example: ---------------------------------------------------------- zynqmpzynqmp_fsblTE modified 20212022.2 FSBL General: - Modified Files: xfsbl_main.c, xfsbl_hooks.h/.c, xfsbl_board.h/.c (search for 'TE Mod' on source code)

- Add Files: te_xfsbl_hooks.h/.c (for hooks and board)

- General Changes:

- Display FSBL Banner and Device Name

Module Specific: - Add Files: all TE Files start with te_*

- Si5338 Configuration

- ETH+OTG Reset over MIO

zynqmp_fsbl_flashTE modified 2021.2 FSBL General: - Modified Files: xfsbl_initialisation.c, xfsbl_hw.h, xfsbl_handoff.c, xfsbl_main.c

- General Changes:

- Display FSBL Banner

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

zynqmp_pmufwXilinx default PMU firmware. pmufwXilinx default PMU firmware. ---------------------------------------------------------- General Example: ---------------------------------------------------------- General Example: hello_te0820Hello TE0820 is a Xilinx Hello World example as endless loop instead of one console output. u-bootU-Boot.elf is generated with PetaLinux. Vitis is used to generate Boot.bin. |

Template location: "<project folder>\sw_lib\sw_apps\"zynqmp_fsbl

TE modified 20212022.2 FSBL

General:

- Modified Files: xfsbl_main.c, xfsbl_hooks.h/.c, xfsbl_board.h/.c (search for 'TE Mod' on source code)

- Add Files: te_xfsbl_hooks.h/.c (for hooks and board)

- General Changes:

- Display FSBL Banner and Device Name

Module Specific:

- Add Files: all TE Files start with te_*

- Si5338 Configuration

- ETH+OTG Reset over MIO

zynqmp_

fsbl_flashpmufw

Xilinx default PMU firmware.

hello

TE modified 2021.2 FSBL

General:

- Modified Files: xfsbl_initialisation.c, xfsbl_hw.h, xfsbl_handoff.c, xfsbl_main.c

- General Changes:

- Display FSBL Banner

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

zynqmp_pmufw

Xilinx default PMU firmware.

hello_te0823

Hello TE0823 is a Xilinx Hello World example as endless loop instead of one console output.

u-boot

U-Boot.elf is generated with PetaLinux. Vitis is used to generate Boot.bin.

Software Design - PetaLinux

| Scroll Ignore |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

|

|

For PetaLinux installation and project creation, follow instructions from:

Config

Start with petalinux-config or petalinux-config --get-hw-description

Changes:

- select SD default instead of eMMC:

- CONFIG_SUBSYSTEM_PRIMARY_SD_PSU_SD_1_SELECT=y

- generate u-boot.dtb:

- CONFIG_SUBSYSTEM_UBOOT_EXT_DTB=y

- add new flash partition for bootscr and sizing

- CONFIG_SUBSYSTEM_FLASH_PSU_QSPI_0_BANKLESS_PART0_SIZE=0x2000000

- CONFIG_SUBSYSTEM_FLASH_PSU_QSPI_0_BANKLESS_PART1_SIZE=0x2000000

- CONFIG_SUBSYSTEM_FLASH_PSU_QSPI_0_BANKLESS_PART2_SIZE=0x20000000x40000

- CONFIG_SUBSYSTEM_FLASH_PSU_QSPI_0_BANKLESS_PART3_NAME="bootscr"

- CONFIG_SUBSYSTEM_FLASH_PSU_QSPI_0_BANKLESS_PART3_SIZE=0x80000

U-Boot

- Identification

- CONFIG_SUBSYSTEM_HOSTNAME="trenz"

- CONFIG_SUBSYSTEM_PRODUCT="TE0823"

U-Boot

Start with petalinux-config -c u-boot

Changes:

- MAC from eeprom together with uboot and device tree settings:

- CONFIG_ENV_OVERWRITE=y

- CONFIG_ZYNQ_GEMMAC_I2C_MAC_OFFSET=0xFAIN_EEPROM is not set

- CONFIG_SYSNET_I2C_EEPROM_ADDR=0x50RANDOM_ETHADDR is not set

- Boot Modes:

- CONFIG_QSPI_BOOT=y

- CONFIG_SD_BOOT=y

- CONFIG_ENV_IS_IN_FAT is not set

- # CONFIG_ENV_IS_IN_NAND is not set

- CONFIG_ENV_IS_IN_SPI_FLASH is not set

- CONFIG_SYS_REDUNDAND_ENVIRONMENT is not set

- CONFIG_BOOT_SCRIPT_OFFSET=0x4040000

- Identification

- CONFIG_IDENT_STRING=" TE0823"

Change platform-top.h:

| Code Block |

|---|

|

#include <configs/xilinx_zynqmp.h>

#no changes |

Device Tree

| Code Block |

|---|

| language | js |

|---|

| title | project-spec\meta-user\recipes-bsp\device-tree\files\system-user.dtsi |

|---|

|

/include/ "system-conf.dtsi"

/*------------------------- QSPI --SD1 sd2.0 ----------------------- */

&qspisdhci1 {

#address-cells = <1>;

#size-cells = <0>;disable-wp;

no-1-8-v;

};

/*----------------------- USB 2.0 only --------------------*/

&dwc3_0 {

status = "okay";

flash0: flash@0 {

dr_mode = "host";

//compatible maximum-speed = "flash name, "micron,m25p80"high-speed";

/delete-property/phy-names;

compatible = "jedec,spi-nor"/delete-property/phys;

/delete-property/snps,usb3_lpm_capable;

reg = <0x0>snps,dis_u2_susphy_quirk;

snps,dis_u3_susphy_quirk;

};

&usb0 {

#address-cells status = <1>"okay";

/delete-property/ clocks;

#size-cells/delete-property/ clock-names;

clocks = <1><0x3 0x20>;

}clock-names = "bus_clk";

};

/*------------------------- SD1ETH sd2.0PHY -----------------------*/

&sdhci1gem3 {

disable-wp/delete-property/ local-mac-address;

no-1-8-v;

};

/*------------------------- ETH PHY -----------------------*/

&gem3 {

phy-handle = <&phy0>;

nvmem-cells = <ð0_addr>;

nvmem-phy-handle = <&phy0>;

nvmem-cells = <ð0_addr>;

nvmem-cell-names = "mac-address";

phy0: phy0@1 {

device_type = "ethernet-phy";

reg = <1>;

};

};

/*------------------------- USB 2.0 only QSPI -----------------------*/-- */

&dwc3_0qspi {

status#address-cells = "okay"<1>;

dr_mode#size-cells = "host"<0>;

maximum-speedstatus = "high-speedokay";

/delete-property/phy-names;

/delete-property/phys;

flash0: flash@0 {

/delete-property/snps,usb3_lpm_capable;

compatible = snps,dis_u2_susphy_quirk"jedec,spi-nor";

snps,dis_u3_susphy_quirk;

};

&usb0 {reg = <0x0>;

status = "okay";

#address-cells /delete-property/ clocks= <1>;

/delete-property/ clock-names;

clocks#size-cells = <0x3 0x20><1>;

clock-names = "bus_clk"};

};

/*---------------------------- I2C ------------------------*/

&i2c0 {

eeprom: eeprom@50 {

compatible = "microchip,24aa025", "atmel,24c02";

reg = <0x50>;

#address-cells = <1>;

#size-cells = <1>;

eth0_addr: eth-mac-addr@FA {

reg = <0xFA 0x06>;

}; };

};

};

|

| Code Block |

|---|

| language | js |

|---|

| title | project-spec\meta-user\recipes-bsp\uboot-device-tree\files\system-user.dtsi |

|---|

|

/include/ "system-conf.dtsi"

/*------------------------- QSPI ------------------------- */

&qspi {

#address-cells = <1>;

#size-cells = <0>;

status = "okay";

flash0: flash@0 {

//compatible = "flash name, "micron,m25p80";

compatible = "jedec,spi-nor";

reg = <0x0>;

#address-cells = <1>;

#size-cells = <1>;

};

};

/*----------------------- SD1 sd2.0 -----------------------*/

&sdhci1 {

disable-wp;

no-1-8-v;

};

/*------------------------- ETH PHY -----------------------*/

&gem3 {

phy-handle = <&phy0>;

nvmem-cells = <ð0_addr>;

nvmem-cell-names = "mac-address";

phy0: phy0@1 {

device_type = "ethernet-phy";

reg = <1>;

};

};

/*----------------------- USB 2.0 only --------------------*/

&dwc3_0 {

status = "okay";

dr_mode = "host";

maximum-speed = "high-speed";

/delete-property/phy-names;

/delete-property/phys;

/delete-property/snps,usb3_lpm_capable;

snps,dis_u2_susphy_quirk;

snps,dis_u3_susphy_quirk;

};

&usb0 {

status = "okay";

/delete-property/ clocks;

/delete-property/ clock-names;

clocks = <0x3 0x20>;

clock-names = "bus_clk";

};

/*---------------------------- I2C ------------------------*/

&i2c0 {

eeprom: eeprom@50 {

compatible = "microchip,24aa025", "atmel,24c02";

reg = <0x50>;

#address-cells = <1>;

#size-cells = <1>;

eth0_addr: eth-mac-addr@FA {

reg = <0xFA 0x06>;

};

};

};

|

FSBL patch

Must be add manually, see template

KernelStart with petalinux-config -c kernel

Changes:

Rootfs

Start with petalinux-config -c rootfs

Changes:

For web server app:Kernel

Start with petalinux-config -c kernel

Changes:

Rootfs

Start with petalinux-config -c rootfs

Changes:

- For web server app:

- For additional test tools only:

- CONFIG_i2c-tools=y

- CONFIG_packagegroup-petalinux-utils=y (util-linux,cpufrequtils,bridge-utils,mtd-utils,usbutils,pciutils,canutils,i2c-tools,smartmontools,e2fsprogs)

- For auto login:

- CONFIG_auto-login=y

- CONFIG_ADD_EXTRA_USERS="root:root;petalinux:;"

FSBL patch (alternative for vitis fsbl trenz patch)

See "<project folder>\os\petalinux\project-spec\meta-user\recipes-bsp\embeddedsw"

te_* files are identical to files in "<project folder>\sw_lib\sw_apps\zynqmp_fsbl\src" except for the PLL files (SI5338) which depend on PLL revision. The PLL files may have to be copied again manually into the appropriate petalinux folder "<project folder>\os\petalinux\project-spec\meta-user\recipes-bsp\embeddedsw\fsbl-firmware\git\lib\sw_apps\zynqmp_fsbl\src"

For additional test tools only:CONFIG_i2c-tools=yCONFIG_packagegroup-petalinux-utils=y (util-linux,cpufrequtils,bridge-utils,mtd-utils,usbutils,pciutils,canutils,i2c-tools,smartmontools,e2fsprogs)Applications

See "<project folder>\os\petalinux\project-spec\meta-user\recipes-apps\"

startup

Script App to load init.sh from SD Card if available.

webfwu

Webserver application suitable for Zynq access. Need busybox-httpd

Additional Software

| Scroll Ignore |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

|

|

| Page properties |

|---|

|

Note:

- Add description for other Software, for example SI CLK Builder ...

- SI5338 and SI5345 also Link to:

|

SI5338

File location "<project folder>\misc\PLL\Si5338\Si5338-*.slabtimeproj"

General documentation how you work with these project will be available on Si5338

Appx. A: Change History and Legal Notices

| Scroll Ignore |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

|

|

Document Change History

To get content of older revision got to "Change History" of this page and select older document revision number.

| Page properties |

|---|

|

- Note this list must be only updated, if the document is online on public doc!

- It's semi automatically, so do following

Add new row below first Copy "Page Information Macro(date)" Macro-Preview, Metadata Version number, Author Name and description to the empty row. Important Revision number must be the same as the Wiki document revision number Update Metadata = "Page Information Macro (current-version)" Preview+1 and add Author and change description. --> this point is will be deleted on newer pdf export template - Metadata is only used of compatibility of older exports

|

| Scroll Title |

|---|

| anchor | Table_dch |

|---|

| title-alignment | center |

|---|

| title | Document change history. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| widths | 2*,*,3*,4* |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Document Revision | Authors | Description |

|---|

| Page info |

|---|

| modified-date |

|---|

| modified-date |

|---|

| dateFormat | yyyy-MM-dd |

|---|

|

| | Page info |

|---|

| current-version |

|---|

| current-version |

|---|

| prefix | v. |

|---|

|

| | Page info |

|---|

| modified-user |

|---|

| modified-user |

|---|

|

| - Release Vivado 2022.2

- new variants

| | 2022-11.18 | v.13 | Manuela Strücker | - bugfix uncomment block design modifications in mod_bd.tcl

- added jtag2axi for test purposes

| | 2022-10-25 | v.11 | Manuela Strücker | | | 2022-10-27 | v.9 | John Hartfiel | - new design files and variants

| | 2021-08-24 | v.8 | John Hartfiel | - startup application added

- webfwu application added

| | 2021-08-18 | v.7 | Mohsen Chamanbaz | | | 2020-03-17 | v.4 | John Hartfiel | |

| All | | Page info |

|---|

| modified-users |

|---|

| modified-users |

|---|

|

|

|

|

Legal Notices

| Include Page |

|---|

| IN:Legal Notices |

|---|

| IN:Legal Notices |

|---|

|