Note:

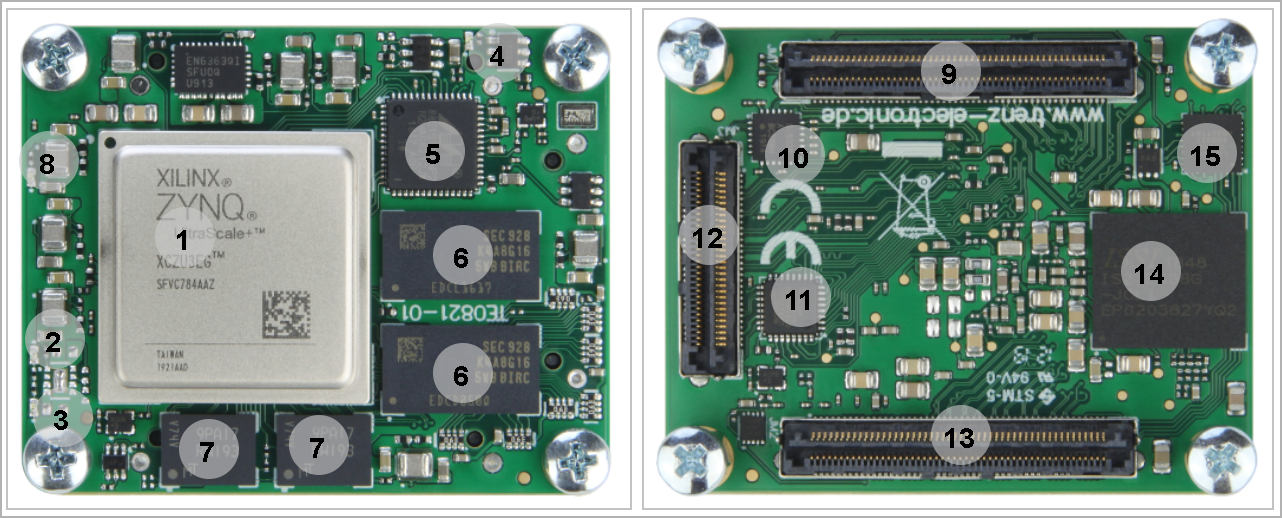

'description: Important components and connector or other Features of the module

→ please sort and indicate assembly options Key Features' must be split into 6 main groups for modules and mainboards: - SoC/FPGA

- Package: SFVC784

- Device: ZU2...ZU5*

- Engine: CG, EG, EV*

- Speed: -1LI, -2LE,*, **

- Temperature: I, E,*, **

- RAM/Storage

- Low Power DDR4 on PS

- Data width: 32bit

- Size: def. 2GB*

- Speed:***

- eMMC

- Data width: 8Bit

- size: def. 8GB *

- QSPI boot Flash in dual parallel mode (size depends on assembly version)

- Data width: 8bit

- size: def. 128MB *

- HyperRAM/Flash (optional, default not assembled)

- MAC address serial EEPROM with EUI-48™ node identity (Microchip 24AA025E48)

- On Board

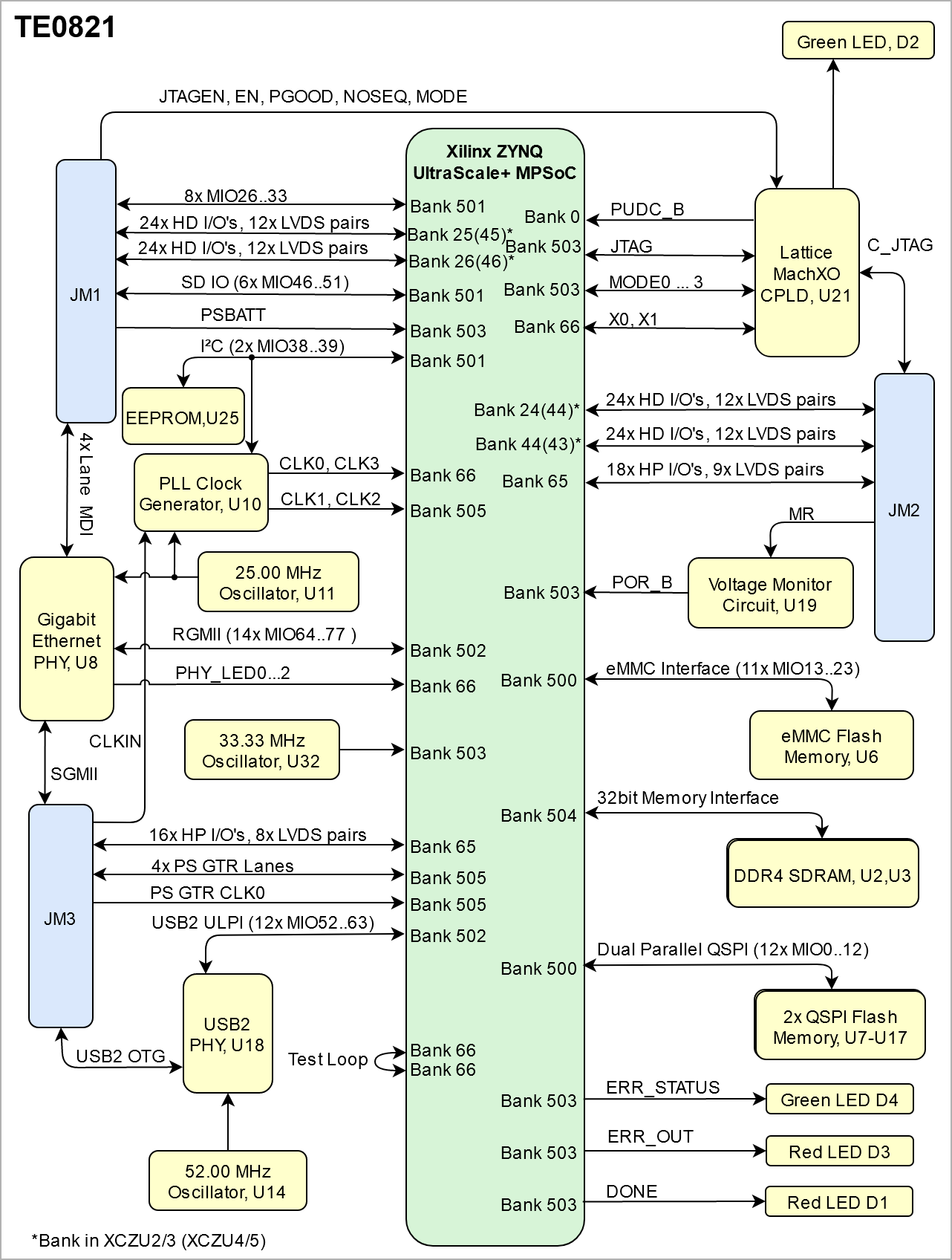

- Lattice LCMXO2

- PLL SI5338

- Gigabit Ethernet transceiver PHY (Marvell Alaska 88E1512)

- Hi-speed USB2 ULPI transceiver with full OTG support (Microchip USB3320C)

- Interface

- 132 x HP PL I/Os (3 banks)

- ETH

- USB

- 4 GTR (for USB3, Sata, PCIe, DP)

- MIO for UART

- MIO for SD

- MIO for PJTAG

- JTAG

- Ctrl

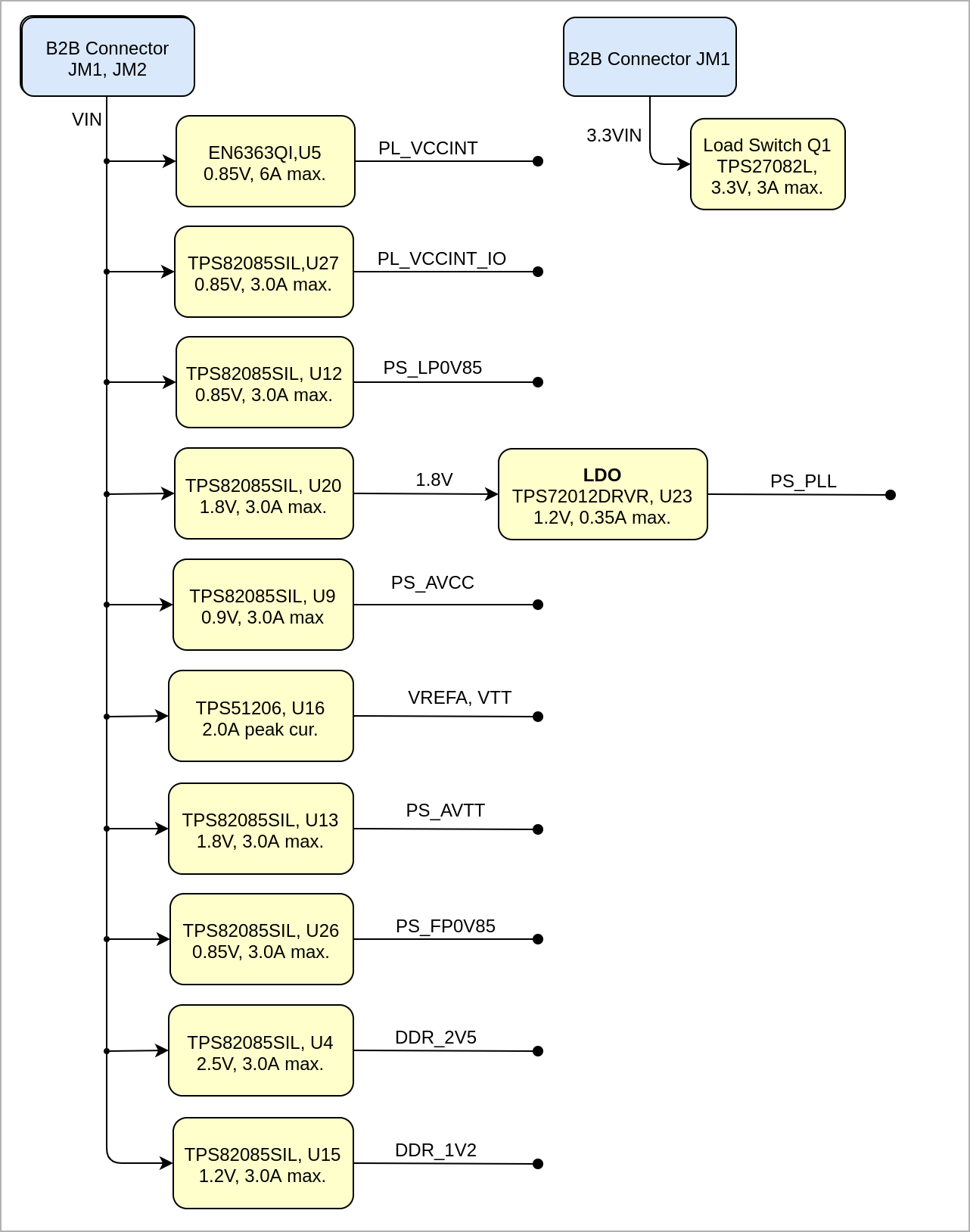

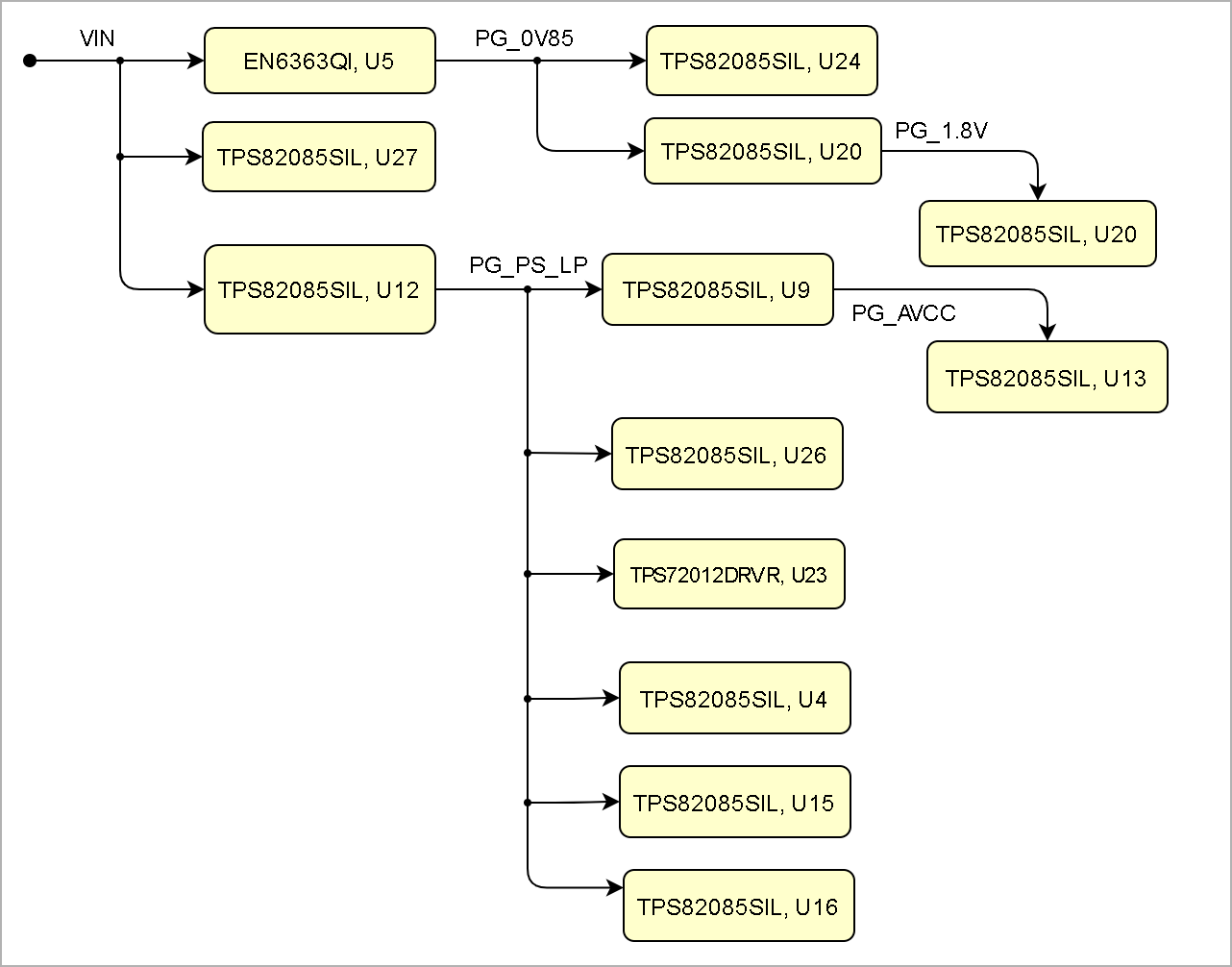

- Power

- 3.3V-5V Main Input

- 3.3V Controller Input

- Variable Bank IO Power Input

- Dimension

- Notes

- * depends on assembly version

- ** also non low power assembly options possible

- *** depends on used U+ Zynq and DDR4 combination

Key Features' must be split into 6 main groups for carrier: - Modules

- TE0808, TE807, TE0803,...

- RAM/Storage

- On Board

- Interface

- E.g. ETH, USB, B2B, Display port

- Power

- E.g. Input supply voltage

- Dimension

|