<!-- Template Revision 1.2 Basic Notes - export PDF to download, if vivado revision is changed! - Template is for different design and SDSoC and examples, remove unused or wrong description! --> |

Online version of this manual and other related documents can be found at https://wiki.trenz-electronic.de/display/PD/Trenz+Electronic+Documentation |

Table of contents |

<!-- General Design description --> |

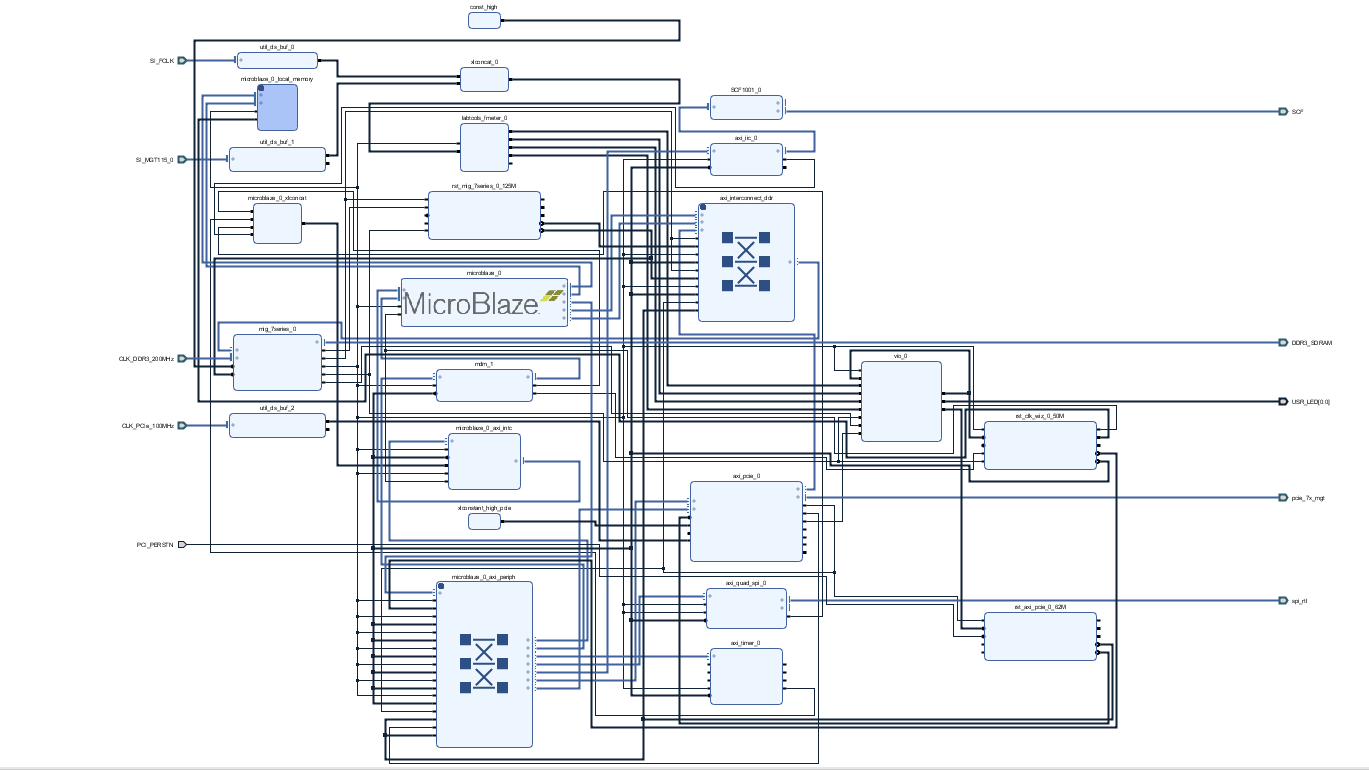

TEF1001 SI5338 Configuration and PCIe Core Example Design.

<!-- Add Basic Key Features of the design (should be tested) --> |

|

<!-- - Add changes from design - Export PDF to download, if vivado revision is changed! --> |

| Date | Vivado | Project Built | Authors | Description |

|---|---|---|---|---|

| 2018-03-07 | 2017.4 | TEF1001-test_board_noprebuilt-vivado_2017.4-build_06_20180307102924.zip TEF1001-test_board-vivado_2017.4-build_06_20180307102845.zip | John Hartfiel | 2017.4 update, new assembly variant |

| 2017-11-28 | 2017.2 | TEF1001-test_board-vivado_2017.2-build_05_20171128114335.zip TEF1001-test_board_noprebuilt-vivado_2017.2-build_05_20171128114350.zip | John Hartfiel | initial release |

<!-- - add known Design issues and general Notes for the current revision --> |

| Issues | Description | Workaround | To be fixed version |

|---|---|---|---|

| No known issues | --- | --- | --- |

<!-- Add needed external Software --> |

| Software | Version | Note |

|---|---|---|

| Vivado | 2017.4 | needed |

| SDK | 2017.4 | needed |

| SI5338 Clock Builder | --- | optional |

<!-- Hardware Support --> |

Basic description of TE Board Part Files is available on TE Board Part Files.

Complete List is available on <design name>/board_files/*_board_files.csv

Design supports following modules:

| Module Model | Board Part Short Name | PCB Revision Support | DDR | QSPI Flash | Others | Notes |

|---|---|---|---|---|---|---|

| TEF1001-01-160-2I | 160_2 | REV01 | SODIMM | 32MB | please, set correct DDR settings on MIG manually | |

| TEF1001-01-325-2C | 325_2 | REV02 | SODIMM | 32MB | please, set correct DDR settings on MIG manually |

Design supports following carriers:

| Carrier Model | Notes |

|---|---|

| PC with PCIe Card slot |

Additional HW Requirements:

| Additional Hardware | Notes |

|---|---|

| JTAG Programmer | TE0790 with TE0791 or other Programmer |

<!-- Remove unused content --> |

For general structure and of the reference design, see Project Delivery

| Type | Location | Notes |

|---|---|---|

| Vivado | <design name>/block_design <design name>/constraints <design name>/ip_lib | Vivado Project will be generated by TE Scripts |

| SDK/HSI | <design name>/sw_lib | Additional Software Template for SDK/HSI and apps_list.csv with settings for HSI |

| Type | Location | Notes |

|---|---|---|

| SI5338 | <design name>/misc/Si5338 | SI5338 Project with current PLL Configuration |

<!-- <table width="100%"> <tr> <th>File </th> <th>File-Extension</th> <th>Description </th> </tr> <tr> <td>BIF-File </td> <td>*.bif </td> <td>File with description to generate Bin-File </td> </tr> <tr> <td>BIN-File </td> <td>*.bin </td> <td>Flash Configuration File with Boot-Image (Zynq-FPGAs) </td> </tr> <tr> <td>BIT-File </td> <td>*.bit </td> <td>FPGA Configuration File </td> </tr> <tr> <td>DebugProbes-File </td> <td>*.ltx </td> <td>Definition File for Vivado/Vivado Labtools Debugging Interface </td> </tr> <tr> <td>Debian SD-Image </td> <td>*.img </td> <td>Debian Image for SD-Card </td> </tr> <tr> <td>Diverse Reports </td> <td> --- </td> <td>Report files in different formats </td> </tr> <tr> <td>Hardware-Platform-Specification-Files</td> <td>*.hdf </td> <td>Exported Vivado Hardware Specification for SDK/HSI </td> </tr> <tr> <td>LabTools Project-File </td> <td>*.lpr </td> <td>Vivado Labtools Project File </td> </tr> <tr> <td>MCS-File </td> <td>*.mcs </td> <td>Flash Configuration File with Boot-Image (MicroBlaze or FPGA part only) </td> </tr> <tr> <td>MMI-File </td> <td>*.mmi </td> <td>File with BRAM-Location to generate MCS or BIT-File with *.elf content (MicroBlaze only) </td> </tr> <tr> <td>OS-Image </td> <td>*.ub </td> <td>Image with Linux Kernel (On Petalinux optional with Devicetree and RAM-Disk) </td> </tr> <tr> <td>Software-Application-File </td> <td>*.elf </td> <td>Software Application for Zynq or MicroBlaze Processor Systems </td> </tr> <tr> <td>SREC-File </td> <td>*.srec </td> <td>Converted Software Application for MicroBlaze Processor Systems </td> </tr> </table> --> |

File | File-Extension | Description |

|---|---|---|

| BIT-File | *.bit | FPGA (PL Part) Configuration File |

| DebugProbes-File | *.ltx | Definition File for Vivado/Vivado Labtools Debugging Interface |

| Diverse Reports | --- | Report files in different formats |

| Hardware-Platform-Specification-Files | *.hdf | Exported Vivado Hardware Specification for SDK/HSI and PetaLinux |

| LabTools Project-File | *.lpr | Vivado Labtools Project File |

MCS-File | *.mcs | Flash Configuration File with Boot-Image (MicroBlaze or FPGA part only) |

MMI-File | *.mmi | File with BRAM-Location to generate MCS or BIT-File with *.elf content (MicroBlaze only) |

| Software-Application-File | *.elf | Software Application for Zynq or MicroBlaze Processor Systems |

Reference Design is only usable with the specified Vivado/SDK/PetaLinux/SDx version. Do never use different Versions of Xilinx Software for the same Project.

<!-- Add correct path:https://shop.trenz-electronic.de/en/Download/?path=Trenz_Electronic/TE0803/Reference_Design/2017.1/Starterkit --> |

Reference Design is available on:

<!-- Basic Design Steps Add/ Remove project specific --> |

Reference Design is available with and without prebuilt files. It's recommended to use TE prebuilt files for first lunch. |

Trenz Electronic provides a tcl based built environment based on Xilinx Design Flow.

See also:

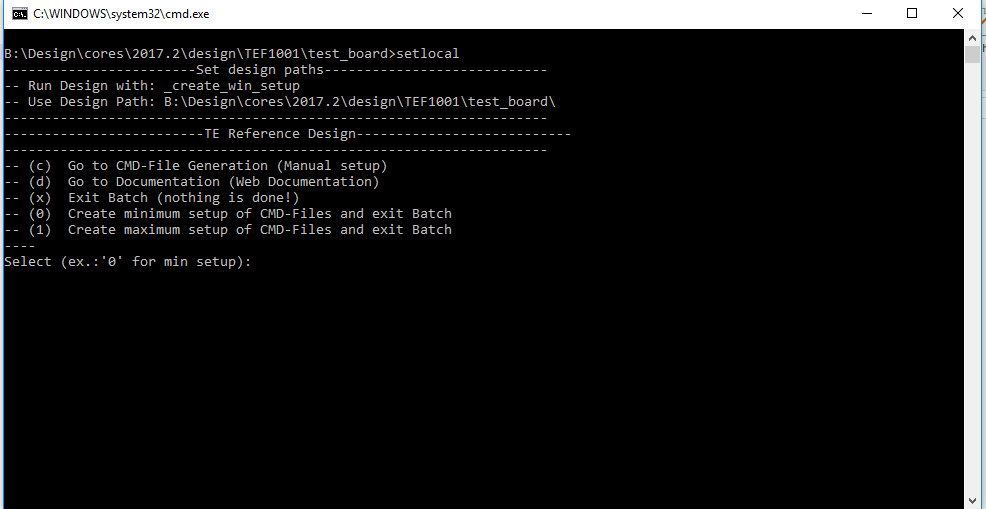

The Trenz Electronic FPGA Reference Designs are TCL-script based project. Command files for execution will be generated with "_create_win_setup.cmd" on Windows OS and "_create_linux_setup.sh" on Linux OS.

TE Scripts are only needed to generate the vivado project, all other additional steps are optional and can also executed by Xilinx Vivado/SDK GUI. For currently Scripts limitations on Win and Linux OS see: Project Delivery Currently limitations of functionality

<!-- Description of Block Design, Constrains... BD Pictures from Export... --> |

Check Module and Carrier TRMs for proper HW configuration before you try any design. |

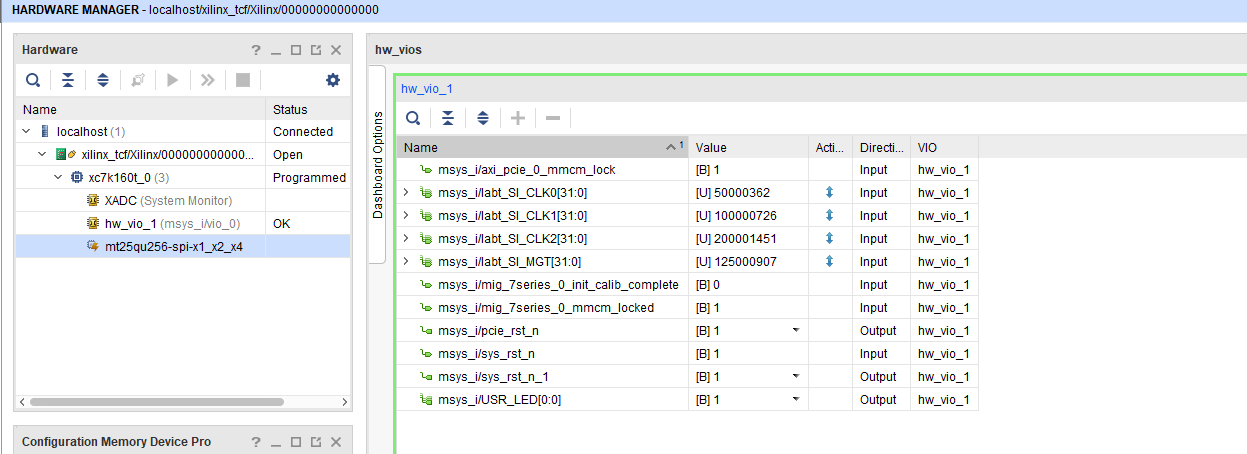

Xilinx documentation for programming and debugging: Vivado/SDK/SDSoC-Xilinx Software Programming and Debugging

<!-- Example: Connect JTAG and power on PCB (if not done) Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd" or open with "vivado_open_project_guimode.cmd", if generated. Type on Vivado Console: TE::pr_program_flash_mcsfile -swapp u-boot Note: Alternative use SDK or setup Flash on Vivado manually Reboot (if not done automatically) --> |

Not used on this Example.

Not used on this Example.

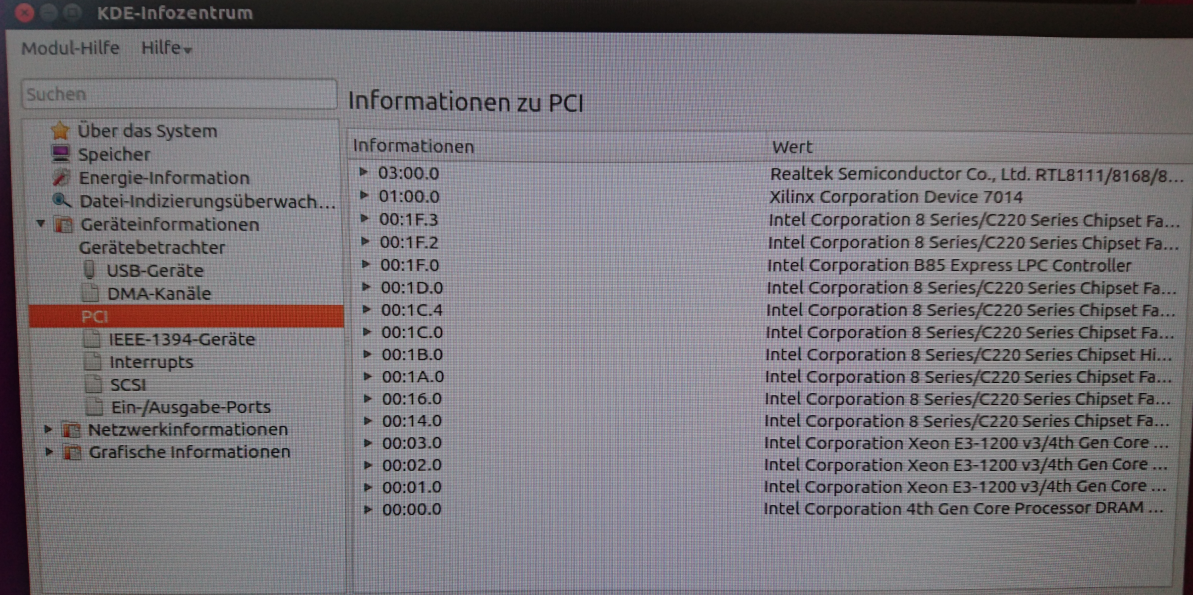

Use for example PCI-Z (Win) or KInfoCenter (Linux) to detect PCIe Card

<!-- Description of Block Design, Constrains... BD Pictures from Export... --> |

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design] set_property BITSTREAM.CONFIG.CONFIGRATE 66 [current_design] set_property CONFIG_VOLTAGE 1.8 [current_design] set_property CFGBVS GND [current_design] set_property CONFIG_MODE SPIx4 [current_design] set_property BITSTREAM.CONFIG.SPI_32BIT_ADDR YES [current_design] set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design] set_property BITSTREAM.CONFIG.M1PIN PULLNONE [current_design] set_property BITSTREAM.CONFIG.M2PIN PULLNONE [current_design] set_property BITSTREAM.CONFIG.M0PIN PULLNONE [current_design] set_property BITSTREAM.CONFIG.USR_ACCESS TIMESTAMP [current_design] |

#----------

#USER LED

# FEX11

set_property PACKAGE_PIN B21 [get_ports {USR_LED[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {USR_LED[0]}]

#----------

#CLK DDR3

set_property PACKAGE_PIN AC9 [get_ports CLK_DDR3_200MHz_clk_p]

set_property IOSTANDARD DIFF_SSTL15 [get_ports CLK_DDR3_200MHz_clk_p]

set_property IOSTANDARD DIFF_SSTL15 [get_ports CLK_DDR3_200MHz_clk_n]

#----------

#QSPI

set_property PACKAGE_PIN C23 [get_ports {spi_rtl_ss_io[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {spi_rtl_ss_io[0]}]

set_property PACKAGE_PIN B24 [get_ports spi_rtl_io0_io]

set_property PACKAGE_PIN A25 [get_ports spi_rtl_io1_io]

set_property PACKAGE_PIN B22 [get_ports spi_rtl_io2_io]

set_property PACKAGE_PIN A22 [get_ports spi_rtl_io3_io]

set_property IOSTANDARD LVCMOS18 [get_ports spi_rtl_io0_io]

set_property IOSTANDARD LVCMOS18 [get_ports spi_rtl_io1_io]

set_property IOSTANDARD LVCMOS18 [get_ports spi_rtl_io2_io]

set_property IOSTANDARD LVCMOS18 [get_ports spi_rtl_io3_io]

#----------

#IIC to CPLD

set_property PACKAGE_PIN G26 [get_ports SCF_cpld_1_scl]

set_property PACKAGE_PIN F25 [get_ports SCF_cpld_14_oe]

set_property PACKAGE_PIN G25 [get_ports SCF_cpld_16_sda]

set_property IOSTANDARD LVCMOS18 [get_ports SCF_cpld_1_scl]

set_property IOSTANDARD LVCMOS18 [get_ports SCF_cpld_14_oe]

set_property IOSTANDARD LVCMOS18 [get_ports SCF_cpld_16_sda]

#----------

#SI5338 CLKs

set_property PACKAGE_PIN H6 [get_ports {SI_MGT115_0_clk_p[0]}]

set_property PACKAGE_PIN G22 [get_ports {SI_FCLK_clk_p[1]}]

set_property PACKAGE_PIN D23 [get_ports {SI_FCLK_clk_p[2]}]

set_property PACKAGE_PIN G24 [get_ports {SI_FCLK_clk_p[0]}]

set_property IOSTANDARD LVDS_25 [get_ports {SI_FCLK_*}] |

#----------

# FEX0

set_property PACKAGE_PIN B20 [get_ports {PCI_PERSTN}]

set_property IOSTANDARD LVCMOS18 [get_ports {PCI_PERSTN}]

#----------

set_property PACKAGE_PIN K6 [get_ports {CLK_PCIe_100MHz_clk_p[0]}]

set_property PACKAGE_PIN N4 [get_ports {pcie_7x_mgt_rxp[2]}]

set_property PACKAGE_PIN R4 [get_ports {pcie_7x_mgt_rxp[3]}]

set_property PACKAGE_PIN L4 [get_ports {pcie_7x_mgt_rxp[1]}]

set_property PACKAGE_PIN J4 [get_ports {pcie_7x_mgt_rxp[0]}] |

<!-- optional chapter separate sections for different apps --> |

For SDK project creation, follow instructions from:

Si5338 I2C Configuration example.

<!-- Add Description for other Software, for example SI CLK Builder ... --> |

SI5338 CLKBuilder

To get content of older revision got to "Change History" of this page and select older document revision number.

<!-- Generate new entry: 1:add new row below first 2:Copy Page Information Macro(date+user) Preview, Page Information Macro Preview 3.Update Metadate =Page Information Macro Preview+1 --> |

| Date | Document Revision | Authors | Description |

|---|---|---|---|

| |||

| 2018-02-08 | v.5 | John Hartfiel |

|

| 2017-11-28 | v.1 |

| |

| All |