<!-- Template Revision 1.4.1 Basic Notes - export PDF to download, if vivado revision is changed! - Template is for different design and SDSoC and examples, remove unused or wrong description! --> |

Online version of this manual and other related documents can be found at https://wiki.trenz-electronic.de/display/PD/Trenz+Electronic+Documentation |

Table of contents |

<!-- General Design description --> |

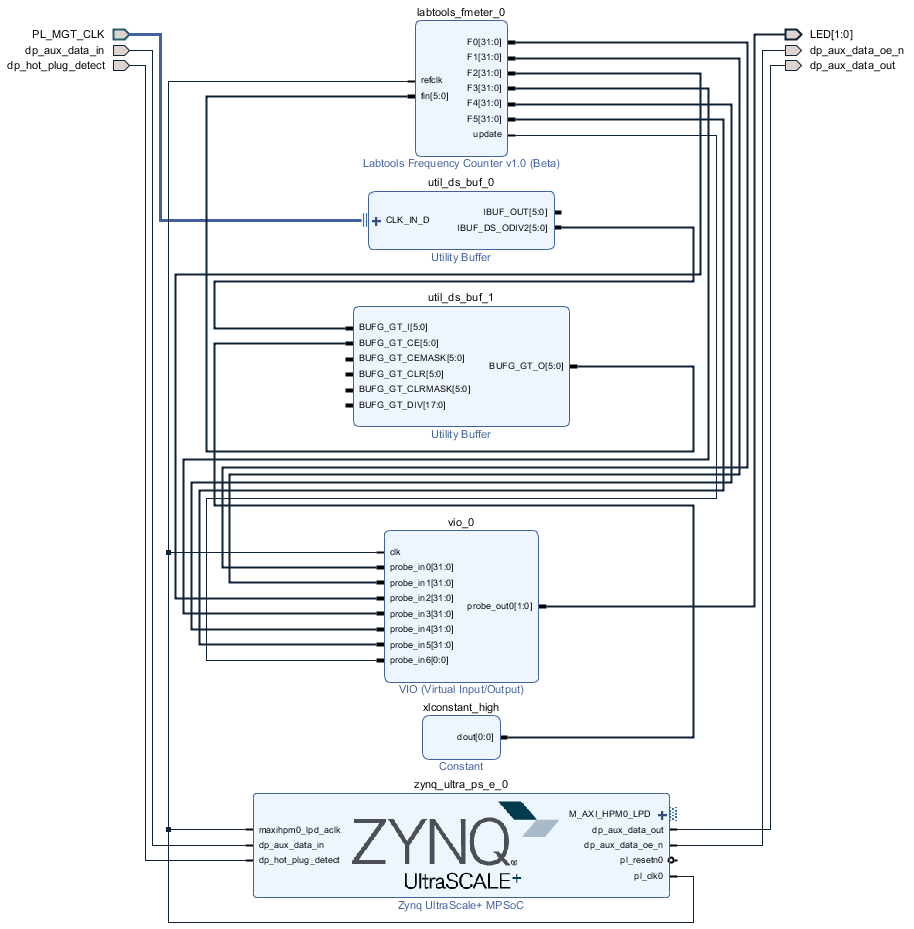

Design example with Linux and MGT-CLK frequency monitoring over VIO.

<!-- Add Basic Key Features of the design (should be tested) --> |

|

<!-- - Add changes from design - Export PDF to download, if vivado revision is changed! --> |

| Date | Vivado | Project Built | Authors | Description |

|---|---|---|---|---|

| 2018-07-20 | 2018.2 | TEB0911-test_board_noprebuilt-vivado_2018.2-build_02_20180719153443.zip TEB0911-test_board-vivado_2018.2-build_02_20180719153429.zip | John Hartfiel |

|

<!-- - add known Design issues and general Notes for the current revision --> |

| Issues | Description | Workaround | To be fixed version |

|---|---|---|---|

| No known issues | --- | --- | --- |

<!-- Add needed external Software --> |

| Software | Version | Note |

|---|---|---|

| Vivado | 2018.2 | needed |

| SDK | 2018.2 | needed |

| PetaLinux | 2018.2 | needed |

<!-- Hardware Support --> |

Basic description of TE Board Part Files is available on TE Board Part Files.

Complete List is available on <design name>/board_files/*_board_files.csv

Design supports following modules:

| Module Model | Board Part Short Name | PCB Revision Support | DDR | QSPI Flash | Others | Notes |

|---|---|---|---|---|---|---|

| REV02, REV01 | SODIMM, configured for 4GB: KVR24S17S8/8 | 64MB |

| |||

| TEB0911-03-09EG-1E | 9eg_1e | REV03, REV02 | SODIMM, configured for 8GB: CT8G4SFS824A | 64MB |

Additional HW Requirements:

| Additional Hardware | Notes |

|---|

<!-- Remove unused content --> |

For general structure and of the reference design, see Project Delivery

| Type | Location | Notes |

|---|---|---|

| Vivado | <design name>/block_design <design name>/constraints <design name>/ip_lib | Vivado Project will be generated by TE Scripts |

| SDK/HSI | <design name>/sw_lib | Additional Software Template for SDK/HSI and apps_list.csv with settings for HSI |

| PetaLinux | <design name>/os/petalinux | PetaLinux template with current configuration |

| SDSoC | <design name>/../SDSoC_PFM | SDSoC Platform will be generated by TE Scripts or as separate download |

| Type | Location | Notes |

|---|---|---|

| SI5345 | <design name>/misc/Si5345 | SI5345 Project with current PLL Configuration |

| SI5338 | <design name>/misc/Si5338 | SI5338 Project with current PLL Configuration |

| init.sh | <design name>/misc/init_script | Additional Initialization Script for Linux |

<!-- <table width="100%"> <tr> <th>File </th> <th>File-Extension</th> <th>Description </th> </tr> <tr> <td>BIF-File </td> <td>*.bif </td> <td>File with description to generate Bin-File </td> </tr> <tr> <td>BIN-File </td> <td>*.bin </td> <td>Flash Configuration File with Boot-Image (Zynq-FPGAs) </td> </tr> <tr> <td>BIT-File </td> <td>*.bit </td> <td>FPGA Configuration File </td> </tr> <tr> <td>DebugProbes-File </td> <td>*.ltx </td> <td>Definition File for Vivado/Vivado Labtools Debugging Interface </td> </tr> <tr> <td>Debian SD-Image </td> <td>*.img </td> <td>Debian Image for SD-Card </td> </tr> <tr> <td>Diverse Reports </td> <td> --- </td> <td>Report files in different formats </td> </tr> <tr> <td>Hardware-Platform-Specification-Files</td> <td>*.hdf </td> <td>Exported Vivado Hardware Specification for SDK/HSI </td> </tr> <tr> <td>LabTools Project-File </td> <td>*.lpr </td> <td>Vivado Labtools Project File </td> </tr> <tr> <td>MCS-File </td> <td>*.mcs </td> <td>Flash Configuration File with Boot-Image (MicroBlaze or FPGA part only) </td> </tr> <tr> <td>MMI-File </td> <td>*.mmi </td> <td>File with BRAM-Location to generate MCS or BIT-File with *.elf content (MicroBlaze only) </td> </tr> <tr> <td>OS-Image </td> <td>*.ub </td> <td>Image with Linux Kernel (On Petalinux optional with Devicetree and RAM-Disk) </td> </tr> <tr> <td>Software-Application-File </td> <td>*.elf </td> <td>Software Application for Zynq or MicroBlaze Processor Systems </td> </tr> <tr> <td>SREC-File </td> <td>*.srec </td> <td>Converted Software Application for MicroBlaze Processor Systems </td> </tr> </table> --> |

File | File-Extension | Description |

|---|---|---|

| BIF-File | *.bif | File with description to generate Bin-File |

| BIN-File | *.bin | Flash Configuration File with Boot-Image (Zynq-FPGAs) |

| BIT-File | *.bit | FPGA (PL Part) Configuration File |

| DebugProbes-File | *.ltx | Definition File for Vivado/Vivado Labtools Debugging Interface |

| Diverse Reports | --- | Report files in different formats |

| Hardware-Platform-Specification-Files | *.hdf | Exported Vivado Hardware Specification for SDK/HSI and PetaLinux |

| LabTools Project-File | *.lpr | Vivado Labtools Project File |

| OS-Image | *.ub | Image with Linux Kernel (On Petalinux optional with Devicetree and RAM-Disk) |

| Software-Application-File | *.elf | Software Application for Zynq or MicroBlaze Processor Systems |

Reference Design is only usable with the specified Vivado/SDK/PetaLinux/SDx version. Do never use different Versions of Xilinx Software for the same Project.

<!-- Add correct path:https://shop.trenz-electronic.de/en/Download/?path=Trenz_Electronic/TE0803/Reference_Design/2017.1/Starterkit --> |

Reference Design is available on:

<!-- Basic Design Steps Add/ Remove project specific --> |

Reference Design is available with and without prebuilt files. It's recommended to use TE prebuilt files for first lunch. |

Trenz Electronic provides a tcl based built environment based on Xilinx Design Flow.

See also:

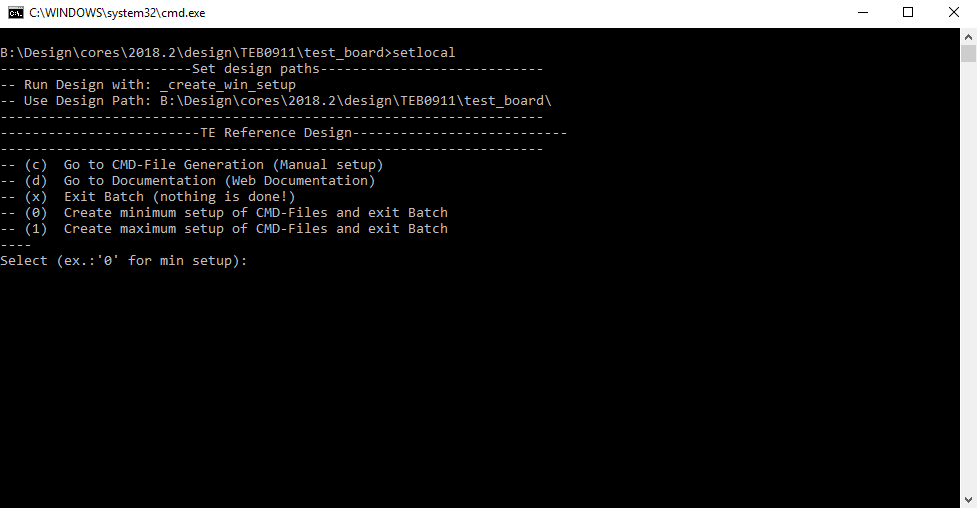

The Trenz Electronic FPGA Reference Designs are TCL-script based project. Command files for execution will be generated with "_create_win_setup.cmd" on Windows OS and "_create_linux_setup.sh" on Linux OS.

TE Scripts are only needed to generate the vivado project, all other additional steps are optional and can also executed by Xilinx Vivado/SDK GUI. For currently Scripts limitations on Win and Linux OS see: Project Delivery Currently limitations of functionality

<!-- Description of Block Design, Constrains... BD Pictures from Export... --> |

Check Module and Carrier TRMs for proper HW configuration before you try any design. |

Xilinx documentation for programming and debugging: Vivado/SDK/SDSoC-Xilinx Software Programming and Debugging

Optional for Boot.bin on QSPI Flash and image.ub on SD.

Not used on this Example.

(coming soon)

<!-- Description of Block Design, Constrains... BD Pictures from Export... --> |

Activated interfaces:

| Typ | Not |

|---|---|

| DDR | SODIMM, setting depends on used memory |

| QSPI | MIO |

| SD0 | MIO |

| SD1 | MIO |

| I2C0 | MIO |

| PJTAG0 | MIO |

| UART0 | MIO |

| GPIO0 | MIO |

| SWDT0..1 | |

| TTC0..3 | |

| GEM3 | MIO |

| USB0 | MIO/GTP |

| PCIe | MIO/GTP |

| DisplayPort | EMIO/GTP |

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design] set_property BITSTREAM.CONFIG.UNUSEDPIN PULLNONE [current_design] |

# GT Clocks

#B128-1

set_property PACKAGE_PIN N27 [get_ports {PL_MGT_CLK_clk_p[0]}]

#B129-1

set_property PACKAGE_PIN J27 [get_ports {PL_MGT_CLK_clk_p[1]}]

#B228-1

set_property PACKAGE_PIN J8 [get_ports {PL_MGT_CLK_clk_p[2]}]

#B130-1

set_property PACKAGE_PIN E27 [get_ports {PL_MGT_CLK_clk_p[3]}]

#B229-1

set_property PACKAGE_PIN E8 [get_ports {PL_MGT_CLK_clk_p[4]}]

#B230-1

set_property PACKAGE_PIN B10 [get_ports {PL_MGT_CLK_clk_p[5]}]

## DP

set_property PACKAGE_PIN AB1 [get_ports dp_aux_data_in]

set_property PACKAGE_PIN V9 [get_ports dp_hot_plug_detect]

set_property PACKAGE_PIN AA8 [get_ports dp_aux_data_out]

set_property PACKAGE_PIN AA3 [get_ports dp_aux_data_oe_n]

set_property IOSTANDARD LVCMOS18 [get_ports dp_*]

## LED

set_property PACKAGE_PIN K14 [get_ports {LED[0]}]

set_property PACKAGE_PIN K10 [get_ports {LED[1]}]

set_property IOSTANDARD LVCMOS18 [get_ports {LED*}]

|

<!-- optional chapter separate sections for different apps --> |

For SDK project creation, follow instructions from:

SDK template in ./sw_lib/sw_apps/ available.

TE modified 2018.2 FSBL

Changes:

Note: Remove compiler flags "-Os -flto -ffat-lto-objects" on 2018.2 SDK to generate FSBL

TE modified 2018.2 FSBL

Changes:

Note: Remove compiler flags "-Os -flto -ffat-lto-objects" on 2018.2 SDK to generate FSBL

Xilinx default PMU firmware.

Hello TEB0911 is a Xilinx Hello World example as endless loop instead of one console output.

U-Boot.elf is generated with PetaLinux. SDK/HSI is used to generate Boot.bin.

<!-- optional chapter Add "No changes." or "Activate: and add List" --> |

For PetaLinux installation and project creation, follow instructions from:

Activate:

Change platform-top.h

#include <configs/platform-auto.h>

#define CONFIG_SYS_BOOTM_LEN 0xF000000

#define DFU_ALT_INFO_RAM \

"dfu_ram_info=" \

"setenv dfu_alt_info " \

"image.ub ram $netstart 0x1e00000\0" \

"dfu_ram=run dfu_ram_info && dfu 0 ram 0\0" \

"thor_ram=run dfu_ram_info && thordown 0 ram 0\0"

#define DFU_ALT_INFO_MMC \

"dfu_mmc_info=" \

"set dfu_alt_info " \

"${kernel_image} fat 0 1\\\\;" \

"dfu_mmc=run dfu_mmc_info && dfu 0 mmc 0\0" \

"thor_mmc=run dfu_mmc_info && thordown 0 mmc 0\0"

/*Required for uartless designs */

#ifndef CONFIG_BAUDRATE

#define CONFIG_BAUDRATE 115200

#ifdef CONFIG_DEBUG_UART

#undef CONFIG_DEBUG_UART

#endif

#endif

/*Define CONFIG_ZYNQMP_EEPROM here and its necessaries in u-boot menuconfig if you had EEPROM memory. */

#ifdef CONFIG_ZYNQMP_EEPROM

#define CONFIG_SYS_I2C_EEPROM_ADDR_LEN 1

#define CONFIG_CMD_EEPROM

#define CONFIG_ZYNQ_EEPROM_BUS 5

#define CONFIG_ZYNQ_GEM_EEPROM_ADDR 0x54

#define CONFIG_ZYNQ_GEM_I2C_MAC_OFFSET 0x20

#endif

|

/include/ "system-conf.dtsi"

/ {

};

/* USB */

&dwc3_0 {

status = "okay";

dr_mode = "host";

};

/* QSPI */

&qspi {

#address-cells = <1>;

#size-cells = <0>;

status = "okay";

flash0: flash@0 {

compatible = "jedec,spi-nor";

reg = <0x0>;

#address-cells = <1>;

#size-cells = <1>;

};

};

/* ETH */

&gem3 {

phy-handle = <&phy0>;

phy0: phy0@1 {

device_type = "ethernet-phy";

reg = <1>;

};

};

/* SD1 */

&sdhci1 {

// disable-wp;

no-1-8-v;

};

&i2c0 {

i2cswitch@76 { // I2C Switch U13

compatible = "nxp,pca9548";

#address-cells = <1>;

#size-cells = <0>;

reg = <0x76>;

i2c-mux-idle-disconnect;

i2c@2 { // FMCD (/dev/i2c-3)

#address-cells = <1>;

#size-cells = <0>;

reg = <2>;

};

i2c@3 { // FMCE (/dev/i2c-4)

#address-cells = <1>;

#size-cells = <0>;

reg = <3>;

};

i2c@4 { // FMCB (/dev/i2c-5)

#address-cells = <1>;

#size-cells = <0>;

reg = <4>;

};

i2c@5 { // FMCC (/dev/i2c-6)

#address-cells = <1>;

#size-cells = <0>;

reg = <5>;

};

i2c@6 { // PLL (/dev/i2c-7)

#address-cells = <1>;

#size-cells = <0>;

reg = <6>;

si570_2: clock-generator3@5d {

#clock-cells = <0>;

compatible = "silabs,si570";

reg = <0x5d>;

temperature-stability = <50>;

factory-fout = <156250000>;

clock-frequency = <78800000>;

};

};

};

i2cswitch@77 { // I2C Switch U37

compatible = "nxp,pca9548";

#address-cells = <1>;

#size-cells = <0>;

reg = <0x77>;

i2c-mux-idle-disconnect;

i2c@0 { // SFP2 (/dev/i2c-9)

#address-cells = <1>;

#size-cells = <0>;

reg = <0>;

};

i2c@1 { // FMCA (/dev/i2c-10)

#address-cells = <1>;

#size-cells = <0>;

reg = <1>;

};

i2c@2 { // FMCF (/dev/i2c-11)

#address-cells = <1>;

#size-cells = <0>;

reg = <2>;

};

i2c@3 { // SFP0 (/dev/i2c-12)

#address-cells = <1>;

#size-cells = <0>;

reg = <3>;

};

i2c@4 { // SFP1 (/dev/i2c-13)

#address-cells = <1>;

#size-cells = <0>;

reg = <4>;

};

i2c@5 { // MEM (/dev/i2c-14)

// Low frequency to work with CPLD

clock-frequency = <100000>;

#address-cells = <1>;

#size-cells = <0>;

reg = <5>;

};

i2c@6 { // DDR4 (/dev/i2c-15)

#address-cells = <1>;

#size-cells = <0>;

reg = <6>;

};

i2c@7 { // USBH (/dev/i2c-16)

#address-cells = <1>;

#size-cells = <0>;

reg = <7>;

};

};

};

/* UNUSED DMA disable */

&lpd_dma_chan1 {

status = "disabled";

};

&lpd_dma_chan2 {

status = "disabled";

};

&lpd_dma_chan3 {

status = "disabled";

};

&lpd_dma_chan4 {

status = "disabled";

};

&lpd_dma_chan5 {

status = "disabled";

};

&lpd_dma_chan6 {

status = "disabled";

};

&lpd_dma_chan7 {

status = "disabled";

};

&lpd_dma_chan8 {

status = "disabled";

};

|

Deactivate:

CONFIG_CPU_IDLE (only needed to fix JTAG Debug issue)

CONFIG_CPU_FREQ (only needed to fix JTAG Debug issue)

Activate:

Script App to load init.sh from SD Card if available.

See: \os\petalinux\project-spec\meta-user\recipes-apps\startup\files

<!-- Add Description for other Software, for example SI CLK Builder ... --> |

No additional software is needed.

Download ClockBuilder Desktop for SI5338

Download ClockBuilder Pro for SI5345

To get content of older revision got to "Change History" of this page and select older document revision number.

<!-- Generate new entry: 1:add new row below first 2:Copy Page Information Macro(date+user) Preview, Page Information Macro Preview 3.Update Metadate =Page Information Macro Preview+1 --> |

| Date | Document Revision | Authors | Description |

|---|---|---|---|

| |||

| 2018-07-20 | v.1 |

| |

| All |