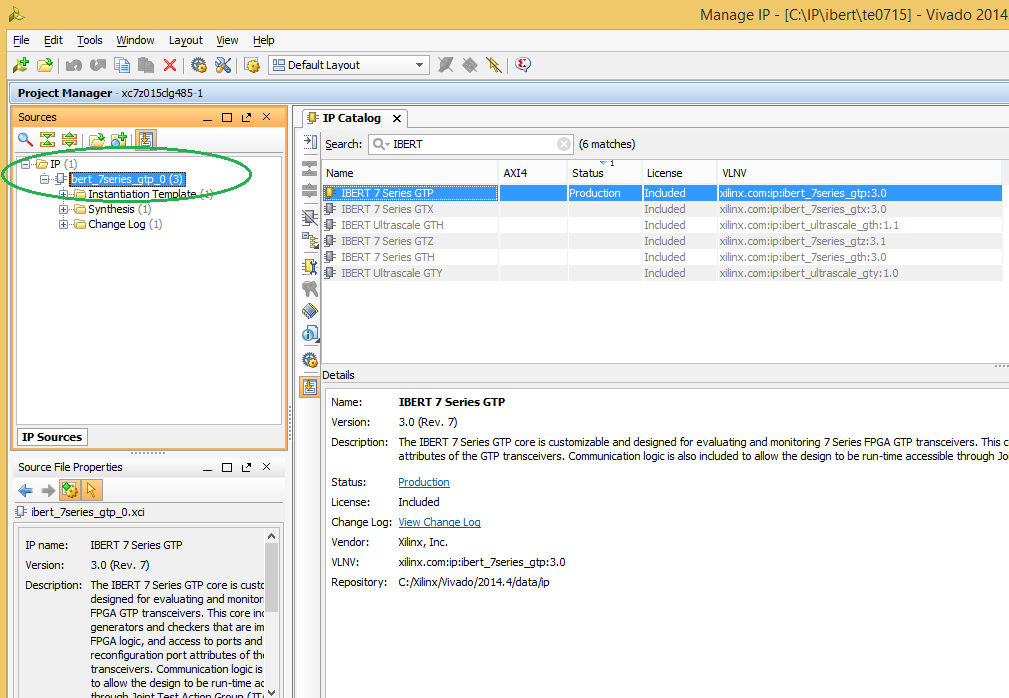

The customizable IBERT core for 7 series FPGA can be used for evaluating and monitoring the GTs.

The IBERT core can be defined and generated using the Vivado built-in IP Cores. And with the generated example designs the IBERT Test can be implemented.

| GT Clock Location | GT Clock(MHz) | Notes | |

|---|---|---|---|

| TE0712 | Quad_216 CLK0 | 125 | Si5338 Clock is connected to GT CLK2 input |

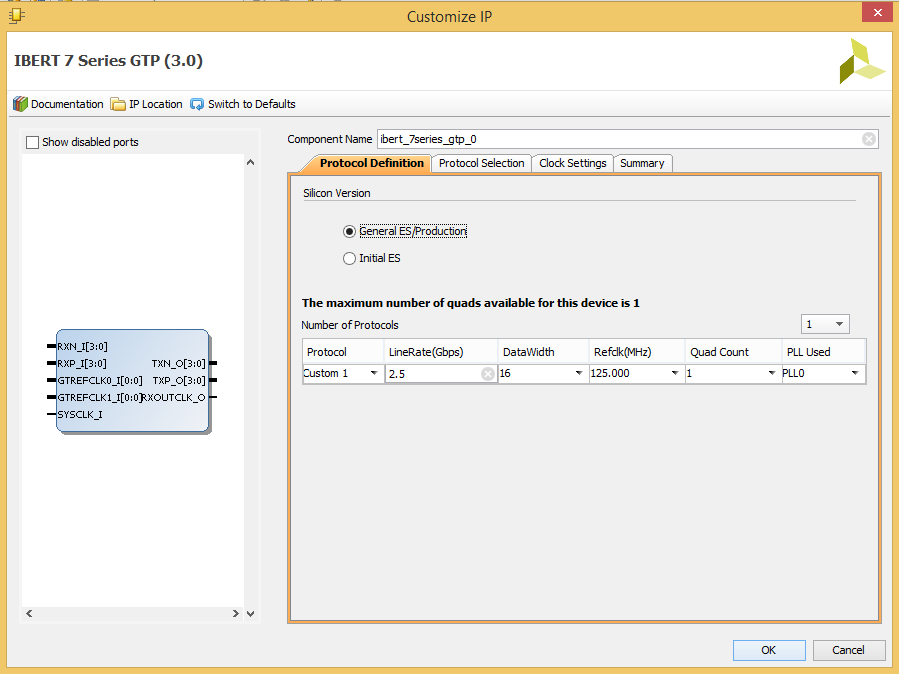

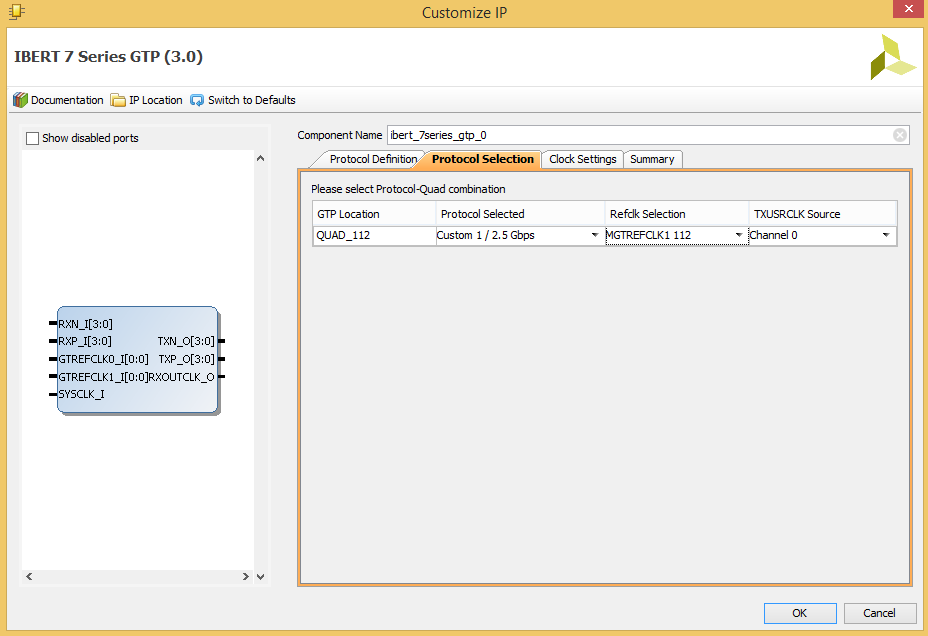

| TE0715 | Quad_112 CLK1 | 125 | Si5338 Clock is connected to GT CLK2 input |

| TE0741 | Quad_115 CLK0, Quad_116 CLK0 | 125 | Si5338 |

Step to Step to generate the IBERT core:

- Create a new IP Location.

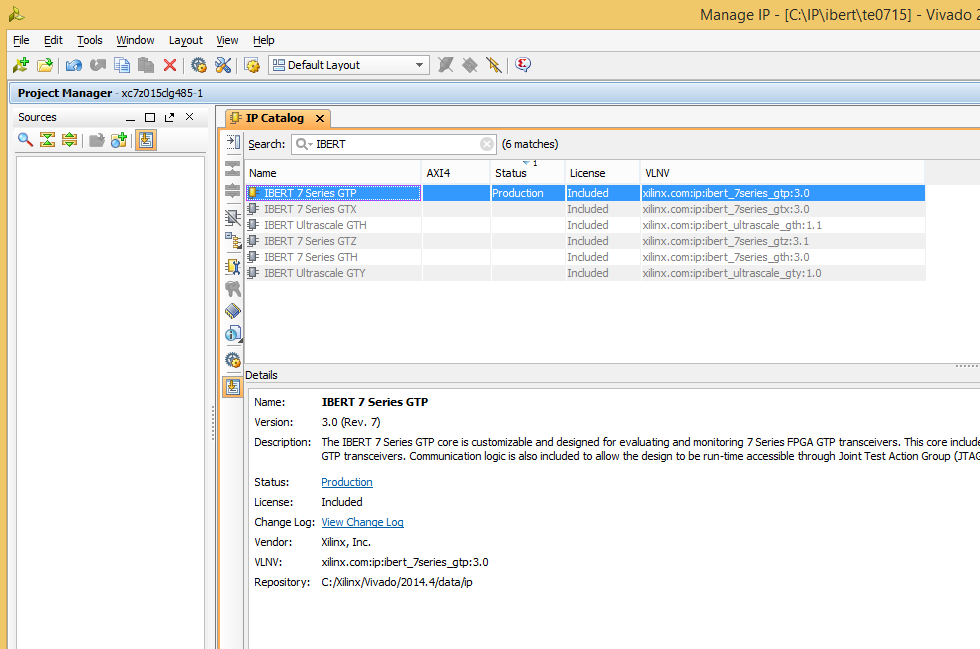

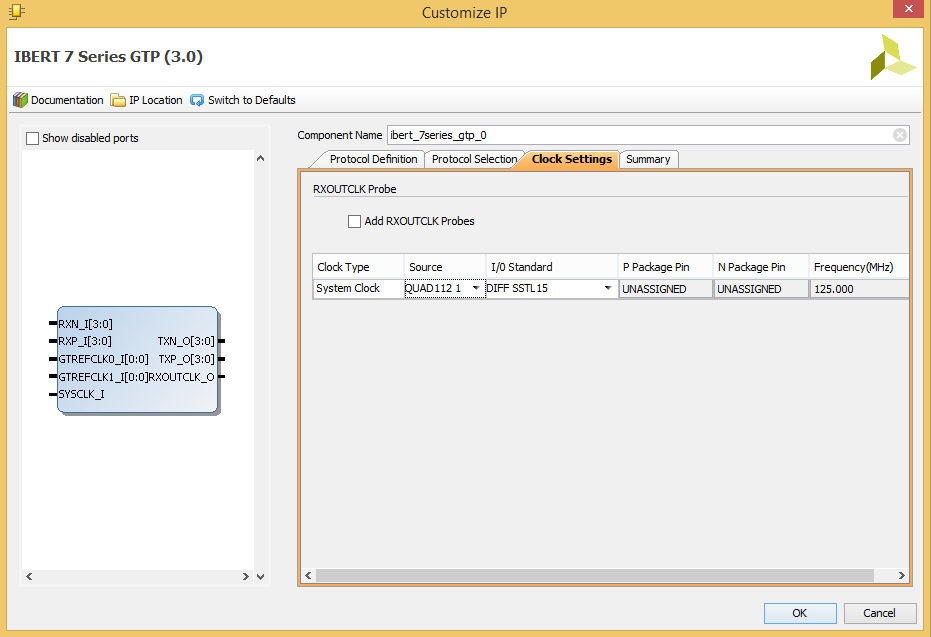

- Double-click IBERT 7 series GTP (or GTX).

- Define the new IBERT. Set the LineRate, select the Quad count, select the Refclk and Clock Source.

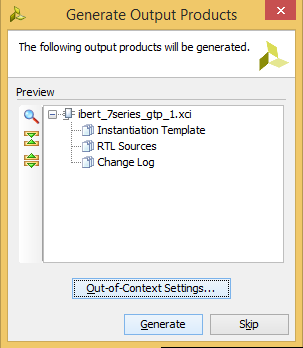

- Generate the Core.

- Open the Example Design.

- Test

References

...

Overview

Content Tools