...

| Scroll Title |

|---|

| anchor | Table_DRH |

|---|

| title | Design Revision History |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Vivado | Project Built | Authors | Description |

|---|

| 2020-04-29 | 2019.2 | TE0725-HyperRAM_noprebuilt-vivado_2019.2-build_10_20200429134457.zip

TE0725-HyperRAM-vivado_2019.2-build_10_20200429134447.zip | John Hartfiel | - add srec application wich loads hello_te0725 from qspi into hyperam

| | 2020-04-17 | 2019.2 | TE0725-HyperRAM-vivado_2019.2-build_10_20200427163950.zip

TE0725-HyperRAM_noprebuilt-vivado_2019.2-build_10_20200427163959.zip | John Hartfiel | | | 2018-08-09 | 2018.2 | TE0725-HyperRAM_noprebuilt-vivado_2018.2-build_02_20180809122634.zip

TE0725-HyperRAM-vivado_2018.2-build_02_20180809122623.zip | John Hartfiel | - 2018.2 update

- new HBMC IP version (v1_3_57)

| | 2018-06-05 | 2017.4 | TE0725-HyperRAM_noprebuilt-vivado_2017.4-build_10_20180605162539.zip

TE0725-HyperRAM-vivado_2017.4-build_10_20180605162425.zip | John Hartfiel | |

|

...

| Scroll Title |

|---|

| anchor | Table_PF |

|---|

| title | Prebuilt files (only on ZIP with prebult content) |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

File | File-Extension | Description |

|---|

| BIT-File | *.bit | FPGA (PL Part) Configuration File | | DebugProbes-File | *.ltx | Definition File for Vivado/Vivado Labtools Debugging Interface | Debian SD-Image | *.img | Debian Image for SD-Card | | Diverse Reports | --- | Report files in different formats | | Hardware-Platform-Specification-Files | *.xsa | Exported Vivado Hardware Specification for Vitis and PetaLinux | | LabTools Project-File | *.lpr | Vivado Labtools Project File | MCS-File | *.mcs | Flash Configuration File with Boot-Image (MicroBlaze or FPGA part only) | MMI-File | *.mmi | File with BRAM-Location to generate MCS or BIT-File with *.elf content (MicroBlaze only) | | Software-Application-File | *.elf | Software Application for Zynq or MicroBlaze Processor Systems | SREC-File | *.srec | Converted Software Application for MicroBlaze Processor Systems |

|

Download

Reference Design is only usable with the specified Vivado/Vitis/PetaLinux version. Do never use different Versions of Xilinx Software for the same Project.

...

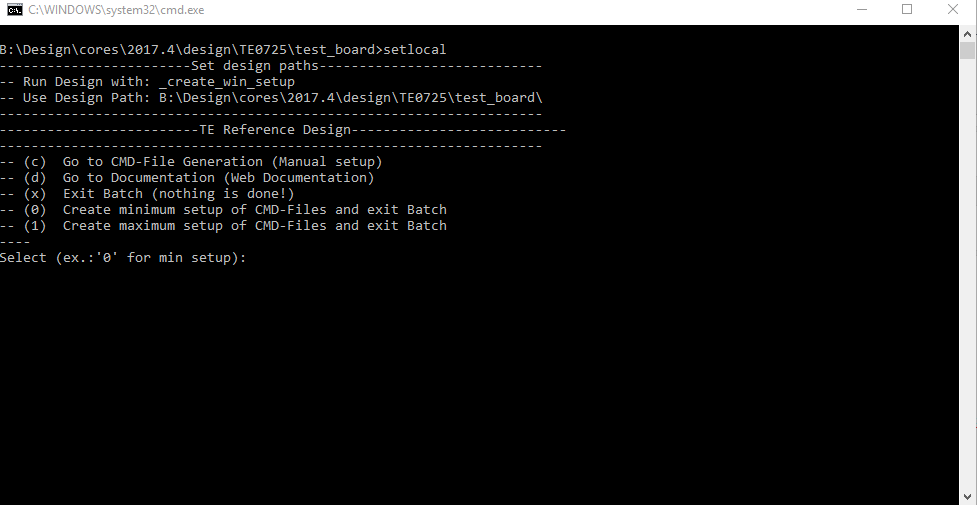

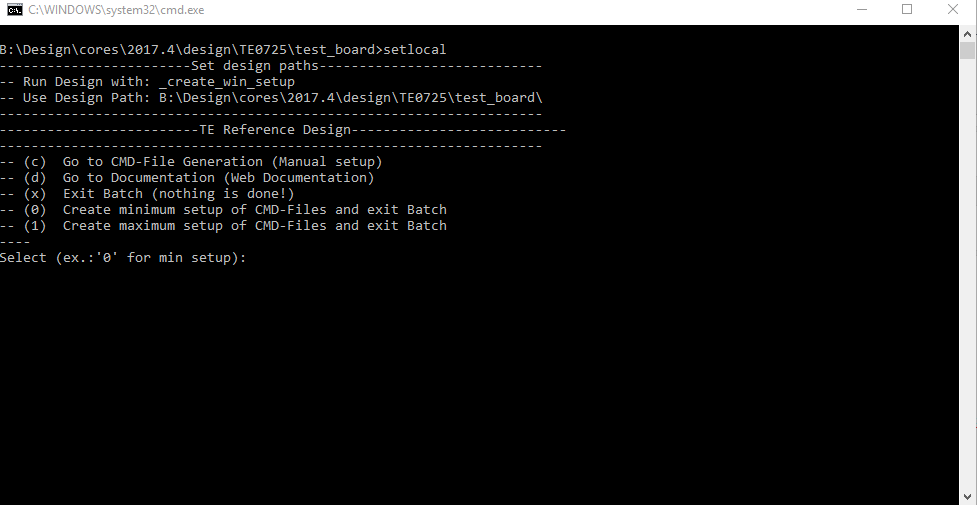

- _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

- Press 0 and enter to start "Module Selection Guide"

- (optional Win OS) Generate Virtual Drive or use short directory for the reference design (for example x:\<design name>)

- Create Project (follow instruction of the product selection guide), settings file will be configured automatically during this process)

- (optional for manual changes) Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

Note: Select correct one, see alsoTE Board Part Files

- Create XSA and export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

- Generate Programming Files with Vitis

- Run on Vivado TCL: TE::sw_run_vitis -all

Note: Scripts generate applications and bootable files, which are defined in "sw_lib\apps_list.csv"

App from Firmware folder will be add into BlockRAM. If you add other app, you must select *.elf manually on Vivado - (alternative) Start SDK with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_vitis

Note: TCL scripts generate also platform project, this must be done manuelly in case GUI is used. See Vitis

- Copy Application (memory_test.elf) into \firmware\microblaze_0\microblaze_0\

- memory_test.elf or srec_spi_bootloader.elf

Note only one elf shouldbe put into this folder

- Regenerate Design:

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: App from Firmware folder will be add into BlockRAM. If you add other app, you must select *.elf manually on Vivado - (alternative) Use SDK or Vivado to update generate Bitfile with new Application and regenerate mcs manually.

...

- Connect JTAG and power on PCB

- (if not done) Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd" or open with "vivado_open_project_guimode.cmd", if generated.

- Open Vivado HW Manager

- Program Bitfile

- Note: Flash musst be configured with correct mcs file, in case srec_spi_bootloader.elf is used as app

Usage

| Info |

|---|

HBMC IP is a 10 minute run-time limited evaluation version of the full-edition |

...

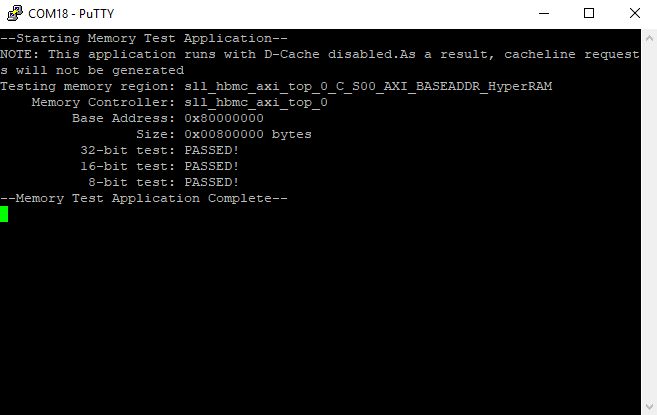

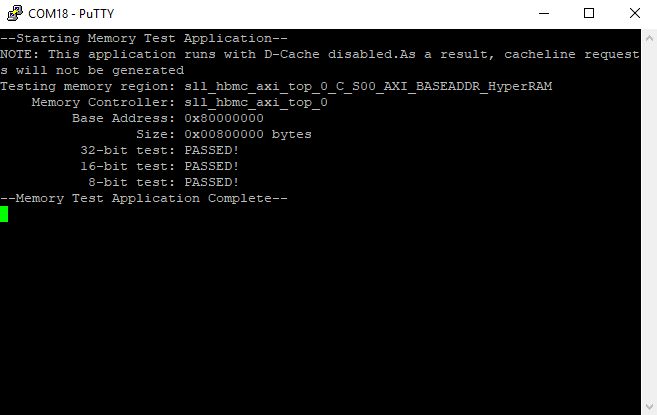

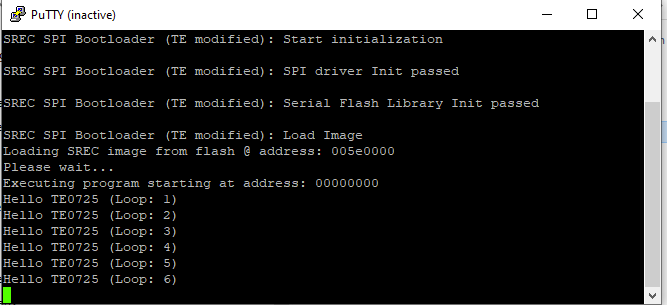

- Open Serial Console (e.g. putty)

- Speed: 9600

- COM Port: Win OS, see device manager, Linux OS see dmesg |grep tty (UART is *USB1)

- Uart Console:

Xilinx Memory test on HyperRAM

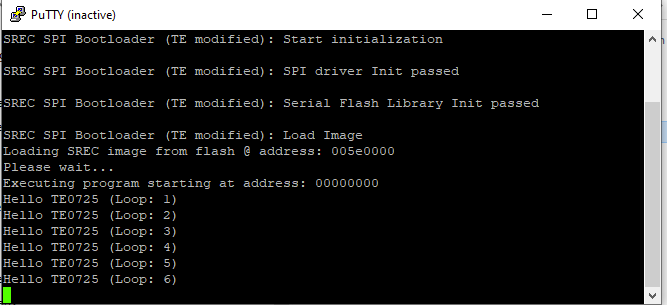

Image RemovedSrec and Hello TE0725: Important, Hello TE0725 is running on Hyperam and Hyperram DEMO-IP has timebomb and stop working after appr. 10 min

Image RemovedSrec and Hello TE0725: Important, Hello TE0725 is running on Hyperam and Hyperram DEMO-IP has timebomb and stop working after appr. 10 min

Image Added

Image Added

System Design - Vivado

...

| Scroll Title |

|---|

| anchor | Table_dch |

|---|

| title | Document change history. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | 2*,*,3*,4* |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Document Revision | Authors | Description |

|---|

| Page info |

|---|

| modified-date |

|---|

| modified-date |

|---|

| dateFormat | yyyy-MM-dd |

|---|

|

| | Page info |

|---|

| current-version |

|---|

| current-version |

|---|

| prefix | v. |

|---|

|

| | Page info |

|---|

| modified-user |

|---|

| modified-user |

|---|

|

| - Design SW update with SREC Bootloader

| | 2020-04-27 | v.5 | John Hartfiel | - 2019.2 update

- Documentation style update

| | 2018-08-09 | v.4 | John Hartfiel | | | v.3 | John Hartfiel |

| | 2018-06-05 | v.2 | John Hartfiel | |

| All | | Page info |

|---|

| modified-users |

|---|

| modified-users |

|---|

|

|

|

|

...