...

| Page properties |

|---|

|

Template Revision 2.6 8 - on construction Design Name always "TE Series Name" + Design name, for example "TE0720 Test Board" |

...

| Page properties |

|---|

|

Notes : - Add basic key futures, which can be tested with the design

|

| Excerpt |

|---|

- Vovadp 2018.3Vitis/Vivado 2019.2

- PetaLinux

- SD

- ETH

- MAC from EEPROM

- USB

- I2C

- RTC

- FMeter

- Modified FSBL (some additional outputs and SI5338 reconfiguration)

- Special FSBL for QSPI Programming

|

...

| Scroll Title |

|---|

| anchor | Table_DRH |

|---|

| title | Design Revision History |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Vivado | Project Built | Authors | Description |

|---|

| 2020-06-10 | 2019.2 | TE0715-test_board-vivado_2019.2-build_12_20200610070857.zip

TE0715-test_board_noprebuilt-vivado_2019.2-build_12_20200610071014.zip | John Hartfiel | - bugfix usb reset

- changes device tree for eeprom mac

- new variants

| | 2019-05-09 | 2018.3 | TE0715-test_board-vivado_2018.3-build_05_20190509094447.zip

TE0715-test_board_noprebuilt-vivado_2018.3-build_05_20190509094505.zip | John Hartfiel | - TE Script update

- rework of the FSBLs

- some additional Linux features

- MAC from EEPROM

| | 2018-10-01 | 2018.2 | TE0715-test_board-vivado_2018.2-build_03_20181001131411.zip

TE0715-test_board_noprebuilt-vivado_2018.2-build_03_20181001131421.zip | John Hartfiel | - Rework Board Part Files (PS)

- small design changes

- SI5338 reconfiguration default activated on FSBL

- update linux startup app

| | 2018-04-26 | 2017.4 | TE0715-test_board-vivado_2017.4-build_07_20180426171530.zip

TE0715-test_board_noprebuilt-vivado_2017.4-build_07_20180426171546.zip | John Hartfiel | | | 2018-03-27 | 2017.4 | te0715-test_board-vivado_2017.4-build_07_20180327223552.zip

te0715-test_board_noprebuilt-vivado_2017.4-build_07_20180327223606.zip | John Hartfiel | - Board Part Bug fix with UART 1

| | 2018-01-05 | 2017.4 | te0715-test_board-vivado_2017.4-build_01_20180105195436.zip

te0715-test_board_noprebuilt-vivado_2017.4-build_01_20180105195452.zip | John Hartfiel | - No Design changes

- Add FSBL for Flash Programming

| | 2017-11-10 | 2017.2 | te0715-test_board-vivado_2017.2-build_05_20171110134232.zip

te0715-test_board_noprebuilt-vivado_2017.2-build_05_20171110134247.zip | John Hartfiel | - New Web Link on Board Part Files

- Add optional FSBL Code to reprogram SI5338

| | 2017-10-19 | 2017.2 | te0715-test_board-vivado_2017.2-build_04_20171019141808.zip

te0715-test_board_noprebuilt-vivado_2017.2-build_04_20171019141825.zip | John Hartfiel | - changed Flash typ on TE0715_board_files.csv

(older one is not supported on Vivado 2017.2)

| | 2017-09-22 | 2017.2 | te0715-test_board-vivado_2017.2-build_02_20170927143412.zip

te0715-test_board_noprebuilt-vivado_2017.2-build_02_20170927143427.zip | John Hartfiel | |

|

...

| Scroll Title |

|---|

| anchor | Table_SW |

|---|

| title | Software |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default | style | widths |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Software | Version | Note |

|---|

| VivadoVitis | 20182019.32 | needed | | SDK | 2018.3 | needed | | , Vivado is included into Vitis installation | | PetaLinux | 2019.2 | PetaLinux | 2018.3 | needed | | SI ClockBuilder Pro | --- | optional |

|

...

| Scroll Title |

|---|

| anchor | Table_HWM |

|---|

| title | Hardware Modules |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Module Model | Board Part Short Name | PCB Revision Support | DDR | QSPI Flash | EMMC | Others | Notes |

|---|

| TE0715-03-15-1C | 03_15_1c_1gb | REV03|REV02|REV01 | 1GB | 32MB | NA | NA | NA | | TE0715-03-15-1I | 03_15_1i_1gb | REV03|REV02|REV01 | 1GB | 32MB | NA | NA | NA | | TE0715-03-15-2I | 03_15_2i_1gb | REV03|REV02|REV01 | 1GB | 32MB | NA | NA | NA | | TE0715-03-30-1C | 03_30_1c_1gb | REV03|REV02|REV01 | 1GB | 32MB | NA | NA | NA | | TE0715-03-30-1I | 03_30_1i_1gb | REV03|REV02|REV01 | 1GB | 32MB | NA | NA | NA | | TE0715-03-30-3E | 03_30_3e_1gb | REV03|REV02|REV01 | 1GB | 32MB | NA | NA | NA | | TE0715-04-15-1C | 04_15_1c_1gb | REV04 | 1GB | 32MB | NA | NA | Low Power DDR | | TE0715-04-15-1I | 04_15_1i_1gb | REV04 | 1GB | 32MB | NA | NA | Low Power DDR | | TE0715-04-15-1I3 | 04_15_1i_1gb | REV04 | 1GB | 32MB | NA | NA | Low Power DDR | | TE0715-04-15-2I | 04_15_2i_1gb | REV04 | 1GB | 32MB | NA | NA | Low Power DDR | | TE0715-04-30-1C | 04_30_1c_1gb | REV04 | 1GB | 32MB | NA | NA | Low Power DDR | | TE0715-04-30-1I | 04_30_1i_1gb | REV04 | 1GB | 32MB | NA | NA | Low Power DDR | | TE0715-04-30-1I3 | 04_30_1i_1gb | REV04 | 1GB | 32MB | NA | NA | Low Power DDR | | TE0715-04-30-3E | 04_30_3e_1gb | REV04 | 1GB | 32MB | NA | NA | Low Power DDR | | TE0715-04-12S-1C | 04_12s_1c_1gb | REV04 | 1GB | 32MB | NA | NA | Low Power DDR | | TE0715-04-30-1IA | 04_30_1i_1gb | REV04 | 1GB | 32MB | NA | NA | Low Power DDR. Micron Flash |

|

Design supports following carriers:

| TE0715-04-30-1I3C1 | 04_30_1i_1gb | REV04 | 1GB | 32MB | NA | NA | Low Power DDR. Low Profile coated with 3M NOVEC EGC-1700 | | TE0715-04-12S-1CC | 04_12s_1c_1gb | REV04 | 1GB | 32MB | NA | NA | Low Power DDR. 3M NOVEC coating | | TE0715-04-15-1IC | 04_15_1i_1gb | REV04 | 1GB | 32MB | NA | NA | Low Power DDR. 3M NOVEC coating |

|

Design supports following carriers:

| Scroll Title |

|---|

| anchor | Table_HWC |

|---|

| title | Hardware Carrier |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

|

|

| Scroll Title |

|---|

| anchor | Table_HWC |

|---|

| title | Hardware Carrier |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | widths | sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Carrier Model | Notes |

|---|

| TE0701 |

| | TE0703 | used as reference carrier | | TE0705 |

| | TE0706 |

| | TEBA0841-02 |

|

|

...

| Scroll Title |

|---|

| anchor | Table_DS |

|---|

| title | Design sources |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Type | Location | Notes |

|---|

| Vivado | <design name>/block_design

<design name>/constraints

<design name>/ip_lib | Vivado Project will be generated by TE Scripts | | SDK/HSIVitis | <design name>/sw_lib | Additional Software Template for SDK/HSI Vitis and apps_list.csv with settings automatically for HSIVitis app generation | | PetaLinux | <design name>/os/petalinux | PetaLinux template with current configuration |

|

...

| Page properties |

|---|

|

Notes : - prebuilt files

- Template Table:

| Scroll Title |

|---|

| anchor | Table_PF |

|---|

| title | Prebuilt files |

|---|

| | Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

File | File-Extension | Description |

|---|

| BIF-File | *.bif | File with description to generate Bin-File | | BIN-File | *.bin | Flash Configuration File with Boot-Image (Zynq-FPGAs) | | BIT-File | *.bit | FPGA (PL Part) Configuration File | | DebugProbes-File | *.ltx | Definition File for Vivado/Vivado Labtools Debugging Interface | Debian SD-Image | *.img | Debian Image for SD-Card | | Diverse Reports | --- | Report files in different formats | | Hardware-Platform-Specification-Files | *.hdfxsa | Exported Vivado Hardware Specification for SDK/HSI Vitis and PetaLinux | | LabTools Project-File | *.lpr | Vivado Labtools Project File | MCS-File | *.mcs | Flash Configuration File with Boot-Image (MicroBlaze or FPGA part only) | MMI-File | *.mmi | File with BRAM-Location to generate MCS or BIT-File with *.elf content (MicroBlaze only) | | OS-Image | *.ub | Image with Linux Kernel (On Petalinux optional with Devicetree and RAM-Disk) | | Software-Application-File | *.elf | Software Application for Zynq or MicroBlaze Processor Systems | SREC-File | *.srec | Converted Software Application for MicroBlaze Processor Systems |

|

|

...

| Scroll Title |

|---|

| anchor | Table_PF |

|---|

| title | Prebuilt files (only on ZIP with prebult content) |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

File | File-Extension | Description |

|---|

| BIF-File | *.bif | File with description to generate Bin-File | | BIN-File | *.bin | Flash Configuration File with Boot-Image (Zynq-FPGAs) | | BIT-File | *.bit | FPGA (PL Part) Configuration File | | DebugProbes-File | *.ltx | Definition File for Vivado/Vivado Labtools Debugging Interface | | Diverse Reports | --- | Report files in different formats | | Hardware-Platform-Specification-Files | *.hdfxsa | Exported Vivado Hardware Specification for SDK/HSI Vitis and PetaLinux | | LabTools Project-File | *.lpr | Vivado Labtools Project File | | OS-Image | *.ub | Image with Linux Kernel (On Petalinux optional with Devicetree and RAM-Disk) | | Software-Application-File | *.elf | Software Application for Zynq or MicroBlaze Processor Systems |

|

...

Reference Design is available on:

Design Flow

...

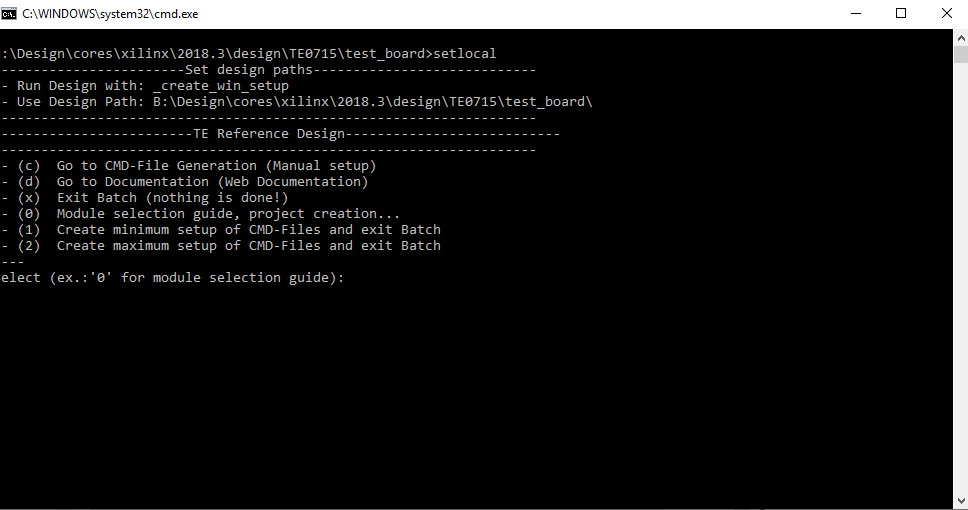

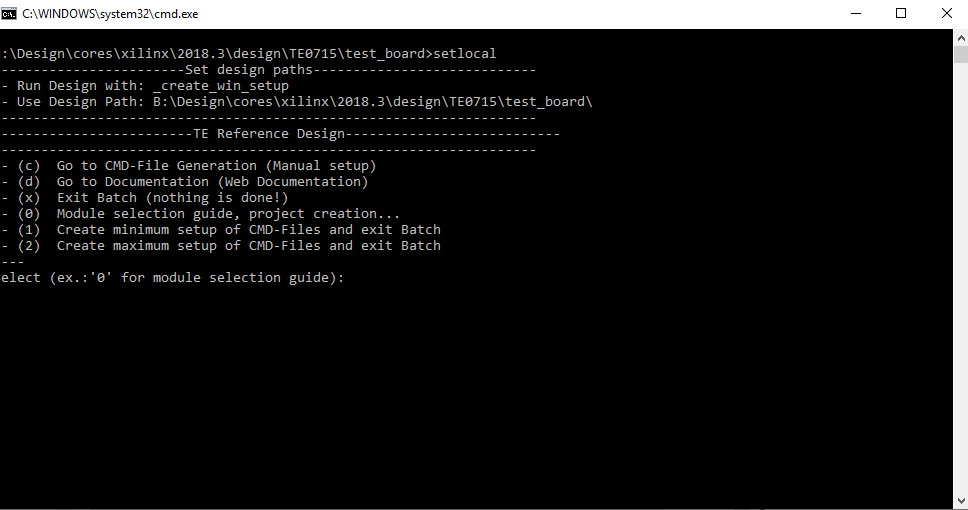

The Trenz Electronic FPGA Reference Designs are TCL-script based project. Command files for execution will be generated with "_create_win_setup.cmd" on Windows OS and "_create_linux_setup.sh" on Linux OS.

...

- Run _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

- Press 0 and enter to start "Module Selection Guide"

- (optional Win OS) Generate Virtual Drive or use short directory for the reference design (for example x:\<design name>)

- Create Project (follow instruction of the product selection guide), settings file will be configured automatically during this process

- (optional for manual changes) Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

- Note: Select correct one, see TE Board Part Files

- Create HDF and XSAand export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

- Create Linux (uboot.elf and image.ub) with exported HDFXSA

- HDF XSA is exported to "prebuilt\hardware\<short name>"

Note: HW Export from Vivado GUI create another path as default workspace. - Create Linux images on VM, see PetaLinux KICKstart

- Use TE Template from /os/petalinuxNote: run init_config.sh before you start petalinux config. This will set correct temporary path variable.

- Add Linux files (uboot.elf and image.ub) to prebuilt folder

- prebuilt\os\petalinux\<ddr size>" or "prebuilt\os\petalinux\<short name>"

- Generate Programming Files with HSI/SDKVitis

- Run on Vivado TCL: TE::sw_run_hsivitis -all

Note: Scripts generate applications and bootable files, which are defined in "sw_lib\apps_list.csv" - (alternative) Start SDK with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_sdkvitis

Note: See SDK Projects TCL scripts generate also platform project, this must be done manuelly in case GUI is used. See Vitis

Launch

| Page properties |

|---|

|

Note:- Programming and Startup procedure

|

...

Xilinx documentation for programming and debugging: Vivado/SDK/SDSoC-Xilinx Software Programming and Debugging

QSPI

Get prebuilt boot binaries

- _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell

- Press 0 and enter to start "Module Selection Guide"

- Select assembly version

- Validate selection

- Select Create and open delivery binary folder

Note: Folder (<project foler>/_binaries_<Artikel Name>) with subfolder (boot_<app name>) for different applications will be generated

QSPI

Optional for Optional for Boot.bin on QSPI Flash and image.ub on SD.

- Connect JTAG and power on carrier with module

- Open Vivado Project with "vivado_open_existing_project_guimode.cmd" or if not created, create with "vivado_create_project_guimode.cmd"

- Type on Vivado TCL Console: TE::pr_program_flash _binfile -swapp u-boot

Note: To program with SDK/Vivado GUI, use special FSBL (zynq_fsbl_flash) on setup

optional "TE::pr_program_flash _binfile -swapp hello_te0715" possible - Copy image.ub on SD-Card

- use files from (<project foler>/_binaries_<Articel Name>)/boot_linux from generated binary folder,see: Get prebuilt boot binaries

- or use prebuilt file location, see <design_name>/prebuilt/readme_file_location.txt

- Set Boot Mode to Set Boot Mode to QSPI-Boot and insered SD.

- Depends on Carrier, see carrier TRM.

...

- Copy image.ub and Boot.bin on SD-Card.

- use files from (<project foler>/_binaries_<Articel Name>)/boot_linux from generated binary folder,see: Get prebuilt boot binaries

- or use For correct prebuilt file location, see <design_name>/prebuilt/readme_file_location.txt

- Set Boot Mode to SD-Boot.

- Depends on Carrier, see carrier TRM.

- Insert SD-Card in SD-Slot.

...

Template location: ./sw_lib/sw_apps/

zynq_fsbl

TE modified 20182019.3 2 FSBL

General:

- Modified Files:main.c, fsbl_hooks.h/.c (search for 'TE Mod' on source code)

Add Files: te_fsbl_hooks.h/.c(for hooks and board)\n\

- General Changes:

- Display FSBL Banner and Device ID

...

zynq_fsbl_flash

TE modified 20182019.3 2 FSBL

General:

- Modified Files: main.c

- General Changes:

- Display FSBL Banner

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

...

U-Boot.elf is generated with PetaLinux. SDK/HSI Vitis is used to generate Boot.bin.

...

Start with petalinux-config -c u-boot

Changes:

- CONFIG_ENV_IS_NOWHERE=y

- # CONFIG_ENV_IS_IN_SPI_FLASH is not set

Change platform-top.h:

- CONFIG_I2C_EEPROM=y

- CONFIG_ZYNQ_GEM_I2C_MAC_OFFSET=0xFA

- CONFIG_SYS_I2C_EEPROM_ADDR=0x50

- CONFIG_SYS_I2C_EEPROM_BUS=0

- CONFIG_SYS_EEPROM_SIZE=256

- CONFIG_SYS_EEPROM_PAGE_WRITE_BITS=0

- CONFIG_SYS_EEPROM_PAGE_WRITE_DELAY_MS=0

- CONFIG_SYS_I2C_EEPROM_ADDR_LEN=1

- CONFIG_SYS_I2C_EEPROM_ADDR_OVERFLOW=0

Change platform-top.h:

| Code Block |

|---|

|

| Code Block |

|---|

|

#include <configs/platform-auto.h>

#define CONFIG_SYS_BOOTM_LEN 0xF000000

#define DFU_ALT_INFO_RAM \

"dfu_ram_info=" \

"setenv dfu_alt_info " \

"image.ub ram $netstart 0x1e00000\0" \

"dfu_ram=run dfu_ram_info && dfu 0 ram 0\0" \

"thor_ram=run dfu_ram_info && thordown 0 ram 0\0"

#define DFU_ALT_INFO_MMC \

"dfu_mmc_info=" \

"set dfu_alt_info " \

"${kernel_image} fat 0 1\\\\;" \

"dfu_mmc=run dfu_mmc_info && dfu 0 mmc 0\0" \

"thor_mmc=run dfu_mmc_info && thordown 0 mmc 0\0"

/*Required for uartless designs */

#ifndef CONFIG_BAUDRATE

#define CONFIG_BAUDRATE 115200

#ifdef CONFIG_DEBUG_UART

#undef CONFIG_DEBUG_UART

#endif

#endif

/*Define CONFIG_ZYNQ_EEPROM here and its necessaries in u-boot menuconfig if you had EEPROM memory. */

//#ifdef CONFIG_ZYNQ_EEPROM

//#define CONFIG_SYS_I2C_EEPROM_ADDR_LEN 1

//#define CONFIG_SYS_I2C_EEPROM_ADDR 0x50

//#define CONFIG_SYS_EEPROM_PAGE_WRITE_BITS 4

//#define CONFIG_SYS_EEPROM_PAGE_WRITE_DELAY_MS 5

//#define CONFIG_SYS_EEPROM_SIZE 1024 /* Bytes */

//#define CONFIG_SYS_I2C_MUX_ADDR 0x74

//#define CONFIG_SYS_I2C_MUX_EEPROM_SEL 0x4

//#endif

#define CONFIG_ZYNQ_EEPROM

#ifdef CONFIG_ZYNQ_EEPROM

#define CONFIG_SYS_I2C_EEPROM_ADDR_LEN 1

#define CONFIG_CMD_EEPROM

#define CONFIG_ZYNQ_EEPROM_BUS 0

#define CONFIG_ZYNQ_GEM_EEPROM_ADDR 0x50

#define CONFIG_ZYNQ_GEM_I2C_MAC_OFFSET 0xFA

#endif |

|

Device Tree

| Code Block |

|---|

|

/include/ "system-conf.dtsi"

/ {

chosen {

xlnx,eeprom = &eeprom;

};/include/ "system-conf.dtsi"

/ {

};

/* default */

/* QSPI PHY */

&qspi {

#address-cells = <1>;

#size-cells = <0>;

status = "okay";

flash0: flash@0 {

compatible = "jedec,spi-nor";

reg = <0x0>;

#address-cells = <1>;

#size-cells = <1>;

};

};

/* ETH PHY */

&gem0 {

status = "okay";

ethernet_phy0: ethernet-phy@0 {

compatible = "marvell,88e1510";

device_type = "ethernet-phy";

reg = <0>;

};

};

/* USB PHY */

/{

usb_phy0: usb_phy@0 {

compatible = "ulpi-phy";

//compatible = "usb-nop-xceiv";

#phy-cells = <0>;

reg = <0xe0002000 0x1000>;

view-port = <0x0170>;

drv-vbus;

};

};

&usb0 {

dr_mode = "host";

//dr_mode = "peripheral";

usb-phy = <&usb_phy0>;

};

/* I2C */

// i2c PLL: 0x70, i2c eeprom: 0x50

&i2c1 {

rtc@6F { // Real Time Clock

compatible = "isl12022";

reg = <0x6F>;

};

//MAC EEPROM

eeprom: eeprom@50 {

compatible = "atmel,24c08";

reg = <0x50>;

};

};

|

Kernel

Start with petalinux-config -c kernel

...

| Scroll Title |

|---|

| anchor | Table_dch |

|---|

| title | Document change history. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | 2*,*,3*,4* |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Document Revision | Authors | Description |

|---|

| Page info |

|---|

| modified-date |

|---|

| modified-date |

|---|

| dateFormat | yyyy-MM-dd |

|---|

|

| | Page info |

|---|

| infoType | Current version |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| prefix | v. |

|---|

| type | Flat |

|---|

|

| | Page info |

|---|

| infoType | Modified by |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| type | Flat |

|---|

|

| | | 2019-05-09 | v.32 | John Hartfiel | - Release 2018.3

- FSBL Rework

- Script rework

- some optional features

| | 2018-10-01 | v.31 | John Hartfiel | - Release 2018.2

- Redesign Board Part Files

- New activate SI5338 example over FSBL

- small Design changes

- Update Documentation Style

| | v.30 | John Hartfiel | | | v.29 | John Hartfiel | | | 2018-02-13 | v.28 | John Hartfiel | | | 2017-11-10 | v.22 | John Hartfiel | - Design Update with new options

- Add Si5338 section

- Update FSBL section

| | 2017-10-19 | v.21 | John Hartfiel | | | 2017-10-19 | v.20 | John Hartfiel | | | 2017-10-06 | v.18 | John Hartfiel | - Text correction

- Update Launch section

- Supported PCBs

| | 2017-10-02 | v.14 | John Hartfiel | - Document update on Prebuilt section

| | 2017-09-28 | v.13 | John Hartfiel | | | -- | all | | Page info |

|---|

| infoType | Modified users |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| type | Flat |

|---|

|

| -- |

|

...