Page History

...

| Scroll Only (inline) |

|---|

Refer to https://wiki.trenz-electronic.de/display/PD/TE0712+TRM for online version of this manual and the rest of available documentation. |

Trenz Electronic TE0712 is an industrial-grade FPGA module integrating a Xilinx Artix-7 FPGA, a 10/100 Mbit Ethernet transceiver, 1 GByte of DDR3 SDRAM, 32 MByte Flash memory for configuration and operation, and powerful switching-mode power supplies for all on-board voltages. Numerous configurable I/Os are provided via rugged high-speed strips. All this on a tiny footprint, smaller than a credit card size at very competitive price. All Trenz Electronic SoMs in 4 x 5 cm form factor are mechanically compatible.

...

| FPGA Bank | B2B Connector | I/O Signal Count | Voltage Level | Notes | |

|---|---|---|---|---|---|

| 13 | JM1 | 10 | VCCIO13 | Supplied by the baseboard. Not available on XC7A35T assembly variant. | |

| 13 | JM3 | 20 | VCCIO13 | Supplied by the baseboard. Not available on XC7A35T assembly variant. | |

| 14 | JM1 | 8 | 3.3V | ||

| 14 | JM2 | 18 | 3.3V | ||

| 14 | JM3 | 4 | 3.3V | ||

| 15 | JM2 | 48 | VCCIO15 | Supplied by the baseboard. | |

| 15 | JM2 | 2 | VCCIO15 | Supplied by the baseboard. | |

| 16 | JM1 | 48 | VCCIO16 | Supplied by the baseboard. |

...

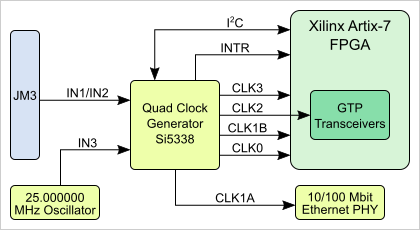

The Si5338 can be programmed to change the output frequency of the FPGA clocks (the Ethernet clock must remain at 50 MHz). An I2C bus is connected between the FPGA (master) and clock generator (slave). Proper logic needs to be created in the FPGA to exercise the I2C bus with the correct data. See the reference design section for more information.

| CLK Output | FPGA Bank | FPGA Pin | IO Standard | Net Name | Default Frequency | Notes | |

|---|---|---|---|---|---|---|---|

| CLK0 | 35 | K4/J4 | DIFF_SSTL15 | CLK0_P/N | -- | NB! Since PCB REV02. | |

| CLK1A | - | - | CLK50M | 50 MHz | PHY chip RMII reference clock. | ||

| CLK1B | 34 | R4 | CLK50M2 | -- | NB! Since PCB REV02. | ||

| CLK2 | 216 | F6/E6 | Auto | MGT_CLK0_P/N | 125 MHz | GTP transceiver clock. | |

| CLK3 | 35 | H4/G4 | DIFF_SSTL15 | PLL_CLK_P/N | 50 MHz |

Certain B2B connector pins are connected to the FPGA pins which are capable of handling clocking signals from the user’s PCB (baseboard). See schematics B2B page for additional information.

...

The 10/100 Mbps Ethernet PHY TLK106 (U5) by Texas Instruments is connected to the FPGA bank 14 using Reduced Media Independent Interface standard (RMII). The RMII standard has reduced set of data lines (two rather than four) and a higher clock frequency (50 MHz rather than 25 MHz) compared to the Media Independent Interface standard (MII). A management interface is also available allowing access to registers in the PHY chip. Transmit and receive signals are connected to the B2B connector JM1. The magnetics and RJ-45 jack must be placed on the user's PCB (baseboard).

FPGA Ethernet Signals

| FPGA Pin | Signal Name | Signal Description |

|---|---|---|

| N17 | ETH-RST | Ethernet reset, active-low. |

| N15 | LINK_LED | Ethernet LED pin indication mode: in mode 1 - LINK, in mode 2 - ACT. |

| R16 | MDC | Ethernet management clock. |

| P17 | MDIO | Ethernet management data. |

| P14 | ETH_TX_D0 | Ethernet transmit data 0. Output to Ethernet PHY. |

| P15 | ETH_TX_D1 | Ethernet transmit data 1. Output to Ethernet PHY. |

| R14 | ETH_TX_EN | Ethernet transmit enable. |

| N13 | ETH_RX_D0 | Ethernet receive data 0. Input from Ethernet PHY. |

| N14 | ETH_RX_D1 | Ethernet receive data 0. Input from Ethernet PHY. |

| P20 | ETH_RX_DV | Ethernet receive data valid. |

All signals are connected to the FPGA bank 14 and correspond to LVCMOS33 standard.

...

See Xilinx datasheet DS181 - "Artix-7 FPGAs Data Sheet: DC and AC Switching Characteristics" for additional information. User should also check related baseboard documentation when choosing baseboard design for TE0712 module.

| Info |

|---|

3.3Vout or 1.8Vout from the module can be used to enable power supply for variable bank power and periphery, see also 4 x 5 SoM Integration Guide#4x5SoMIntegrationGuide-4x5ModuleControllerIOs |

| Page break |

|---|

Power Rails

Power Rail Name | B2B Connector JM1 Pin | B2B Connector JM2 Pin | Direction | Notes |

|---|---|---|---|---|

VIN | 1, 3, 5 | 2, 4, 6, 8 | Input | SoM supply voltage (from the baseboard). |

| 3.3VIN | 13, 15 | - | Input | SoM supply voltage (from the baseboard). |

| 1.5V | - | 19 | Output | Module internal 1.5V level. |

1.8V | 39 | - | Output | Module internal 1.8V level. Maximum 300mA available. |

| 3.3V | - | 10, 12 | Output | Module internal 3.3V level. |

| 3.3V | 14 | Output | Module internal 3.3V level. Not on all 4x5 modules | |

| VCCIO13 | - | 1, 3 | Input | High-Range bank supply voltage (from the baseboard). |

| VCCIO15 | - | 7, 9 | Input | High-Range bank supply voltage (from the baseboard). |

| VCCIO16 | 9, 11 | - | Input | High-Range bank supply voltage (from the baseboard). |

| VREF_JTAG | - | 91 | Output | JTAG reference voltage (3.3V). |

...

| Date | Revision | Notes | PCN | Documentation Link | |

|---|---|---|---|---|---|

| 2016-12-09 | 02 | Second production revision | Click to see PCN | TE0712-02 | |

| 2013-12-02 | 01 | First production revision | TE0712-01 |

Hardware revision number is printed on the PCB board together with the module model number separated by the dash.

...

Date | Revision | Contributors | Description | ||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

|

|

| ||||||||||||||||||||||||||

| 2019-01-10 | v.22 | John Hartfiel |

| ||||||||||||||||||||||||||

| 2017-12-15 | v.18 | John Hartfiel |

| ||||||||||||||||||||||||||

| 2017-12-12 | v.15 | John Hartfiel |

| ||||||||||||||||||||||||||

| 2017-05-29 | v.13 | Jan Kumann |

| ||||||||||||||||||||||||||

| 2017-03-01 | v.7 | John Hartfiel |

| ||||||||||||||||||||||||||

| 2017-01-26 | v.3 | Jan Kumann |

| ||||||||||||||||||||||||||

| 2017-01-20 | v.2 | Jan Kumann |

| ||||||||||||||||||||||||||

| 2013-12-02 | v.1 | Antti Lukats |

| ||||||||||||||||||||||||||

| -- | all |

|

|

...