Page History

...

| Scroll Only (inline) |

|---|

Refer to https://shopwiki.trenz-electronic.de/de/Download/?path=Trenz_Electronicdisplay/PD/TE0820+TRM for downloadableonline version of this manual and additional technical documentation of the product. |

Key Features

- Xilinx Zynq UltraScale+ MPSoC 784-pin package (ZU3EG, option for ZU5EV)

- Dual Cortex-A53 64-bit ARM v8 application processing unit (APU)

- Dual Cortex-R5 32-bit ARM v7 real-time processing unit (RPU)

Four high-speed serial I/O (HSSIO) interfaces supporting following protocols:

- PCI Express® interface version 2.1 compliant

- SATA 3.1 specification compliant interface

DisplayPort source-only interface with video resolution up to 4k x 2k

- USB 3.0 specification compliant interface implementing a 5 Gb/s line rate

- 1 Gb/s serial GMII interface

- 132 x HP PL I/Os (3 banks)

- 14 x PS MIOs (6 of the MIOs intended for SD card interface in default configuration)

- 4 x serial PS GTR transceivers

- 32-Bit DDR4, 4 GByte maximum

- Dual parallel SPI boot Flash, 512 MByte maximum

- 4 GByte eMMC (up to 64 GByte)

- GT reference clock input

- PLL for GT clocks (optional external reference)

- Gigabit Ethernet transceiver PHY (Marvell Alaska 88E1512)

- Hi-speed USB 2.0 ULPI transceiver with full OTG support (Microchip USB3320C)

- Programmable quad clock generator

- Plug-on module with 2 x 100-pin and 1 x 60-pin high-speed hermaphroditic strips

- All power supplies on board

- Size: 50 x 40 mm

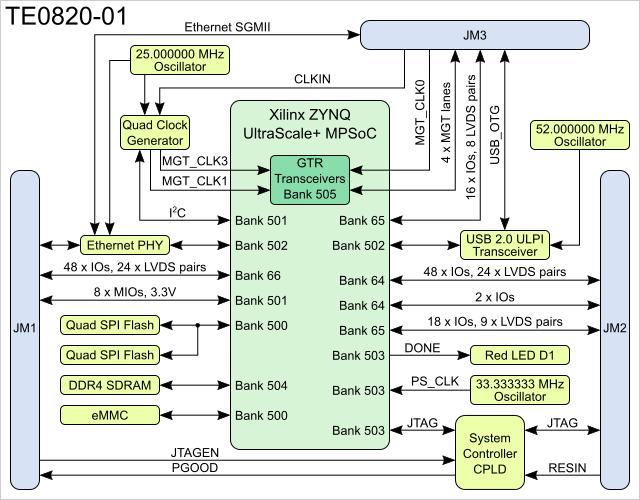

Block Diagram

| Page break |

|---|

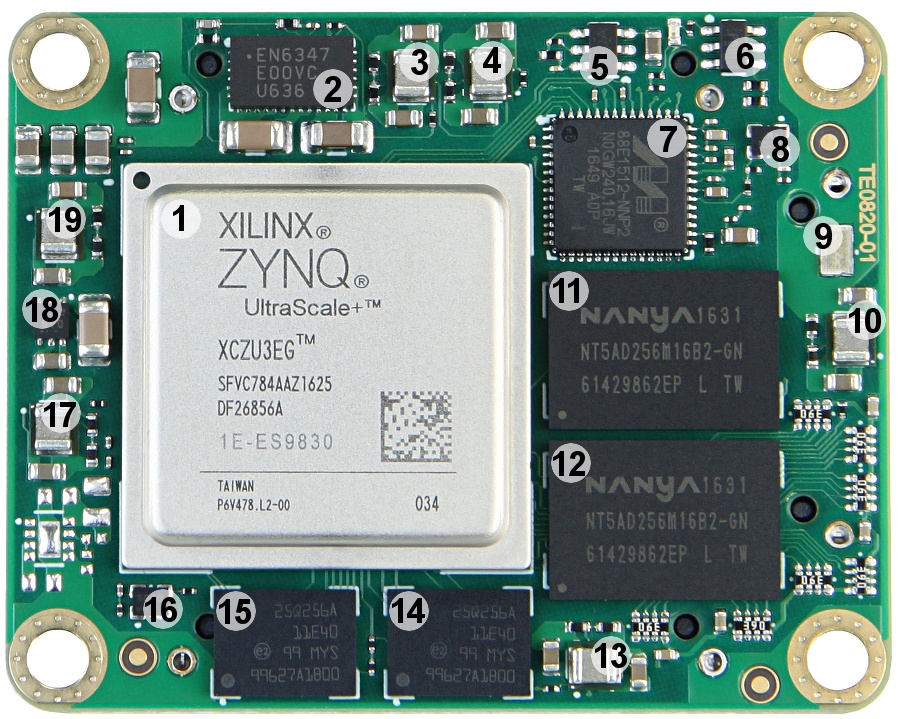

Main Components

- Xilinx Zynq UltraScale+ ZU3EG MPSoC, U1

- 4A power system on a chip ( PowerSoC ) DC-DC converter (PL_VCCINT, 0.85V), U5

- 3A High high-efficiency step-down converter MicroSiP™ with integrated inductor (PS_AVCC, 0.9V), U9

- 3A High high-efficiency step-down converter MicroSiP™ with integrated inductor (PS_AVTT, 1.8V), U13

3A PFET load switch with configurable slew rate, fast transient isolation and hysteresis control (3.3V), Q1

- Ultralow Ultra-low supply-current voltage monitor with optional watchdog, U19

- Marvell Alaska 88E1512 integrated 10/100/1000 Mbps energy efficient ethernet transceiver, U8

- Low-power programmable oscillator @ 12.000000 MHz, U11

- Miniature traceability S/N pad for low-cost, unique product identification

- 3A High high-efficiency step-down converter MicroSiP™ with integrated inductor (DDR_2V5, 2.5V), U4

- 4 Gbit (256 x 16) DDR4 SDRAM, U3

- 4 Gbit (256 x 16) DDR4 SDRAM, U2

- 3A High high-efficiency step-down converter MicroSiP™ with integrated inductor (DDR_1V2, 1.2V), U15

- 1.8V, 256 Mbit multiple I/O serial flash memory, U17

- 1.8V, 256 Mbit multiple I/O serial flash memory, U7

- Low-power programmable oscillator @ 33.333333 MHz, U32

- 3A High high-efficiency step-down converter MicroSiP™ with integrated inductor (PS_VCCINT, 0.85V), U12

- 350 mA, ultra-low VIN, RF low-dropout linear regulator with bias pin (PS_PLL, 1.2V), U23

- 3A High high-efficiency step-down converter MicroSiP™ with integrated inductor (1.8V), U20

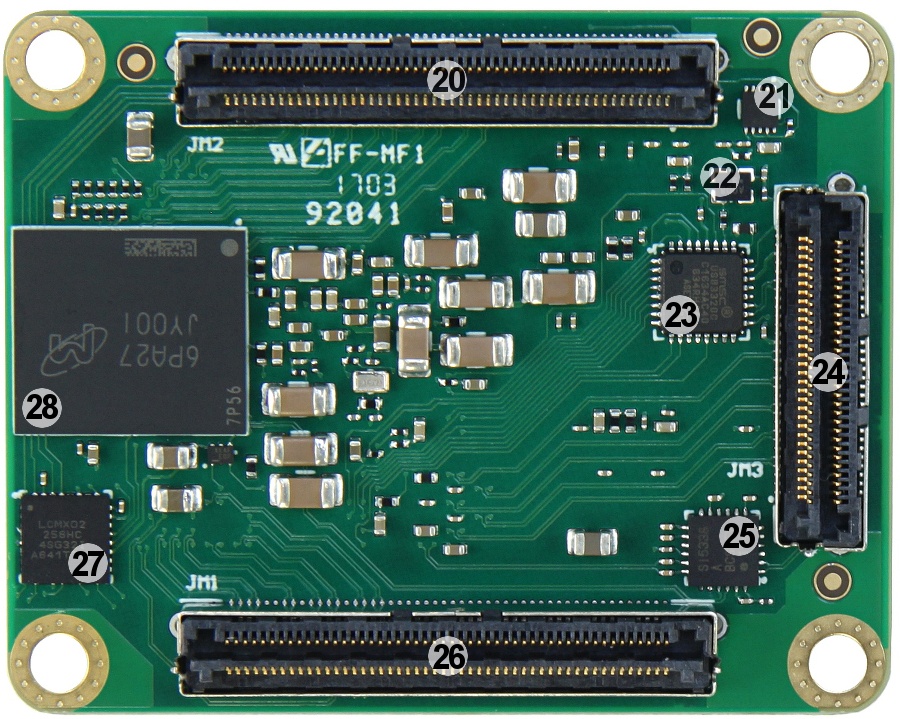

- B2B connector Samtec Razor Beam™ LSHM-150, JM2

- 2A peak sink / source DDR termination regulator with VTTREF buffered reference for DDR2, DDR3, DDR3L, and DDR4, U16

- Low-power programmable oscillator @ 52.000000 MHz, U14

- Highly integrated full featured hi-speed USB 2.0 ULPI transceiver, U18

- B2B connector Samtec Razor Beam™ LSHM-130, JM3

- I2C programmable, any frequency , any output quad clock generator, U10

- B2B connector Samtec Razor Beam™ LSHM-150, JM1

- Lattice Semiconductor MachXO2 System Controller CPLD, U21

- 4 GByte eMMC memory, U6

Key features

- Xilinx Zynq UltraScale+ MPSoC 784 pin package (ZU3EG, option ZU5EV)

- Memory:

- 32-Bit DDR4 - 4 GByte max

- SPI Boot Flash dual parallel - 512 MByte max

- 4 GByte eMMC (up to 64 GByte)

- B2B connectors:

Plug-on module with 2 x 100-pin and 1 x 60-pin high-speed hermaphroditic strips- 14 x MIO, 132 I/O's x HP (3 banks)

- 4 x serial PS GTR transceivers

- GT Reference clock input

- PLL for GT clocks (optional external reference)

- 1 Gbit Ethernet PHY

- USB 2.0 OTG PHY

- Real Time Clock

- Size: 40 x 50 mm

- All power supplies on board.

Initial delivery state

Initial delivery state

| Storage Device Name | Content | Notes |

|---|---|---|

SPI Flash OTP Area | Empty, not programmed | Except serial number programmed by flash vendor. |

SPI Flash Quad Enable bit | Programmed | - |

SPI Flash main array | Demo design | - |

eFUSE USER | Not programmed | - |

eFUSE Security | Not programmed | - |

| Si5338 OTP NVM | Default settings pre-programmed | OTP not re-programmable after delivery from factory |

Signals,

...

Interfaces and Pins

Board to Board (B2B) I/Os

Zynq MPSoC's I/O banks signals connected to the MPSoC's I/O bank and B2B connectorB2B connectors:

| Bank | Type | B2B Connector | I/O Signal Count | Voltage | Notes |

|---|---|---|---|---|---|

64 | HP | JM2 | 48 | User | Max voltage 1.8V. |

64 | HP | JM2 | 2 | User | Max voltage 1.8V. |

| 65 | HP | JM2 | 18 | User | Max voltage 1.8V. |

65 | HP | JM3 | 1216 | User | Max voltage 1.8V. |

66 | HP | JM1 | 48 | User | Max voltage 1.8V. |

501 | MIO | JM1 | 6 | 1.8V | - |

505 | GTR | JM3 | 4 lanes | N/A | - |

505 | GTR CLK | JM3 | 1 differential input | N/A | - |

For detailed information about the pin-out, please refer to the Pin-out Tabletable.

JTAG Interface

JTAG access to the Xilinx Zynq-7000 is provided through B2B connector JM2.

JTAG Signal | B2B Connector Pin |

|---|---|

| TMS | JM2-93 |

| TDI | JM2-95 |

| TDO | JM2-97 |

| TCK | JM2-99 |

Pin 89 JTAGEN of B2B connector JM1 is used to control which device is accessible via JTAG. If set to low or grounded, JTAG is routed to the Xilinx Zynq MPSoC. If pulled high, JTAG is routed to System Controller CPLD.

| Page break |

|---|

System Controller I/O Pins

...

Special purpose pins are connected to System Controller CPLD and have following default configuration:

| Pin Name | Mode | Function | Default Configuration |

|---|---|---|---|

| EN1 | Input | Power Enable | No hard wired function on PCB, when forced low pulls POR_B low to emulate power on reset. |

| PGOOD | Output | Power Good | Active high when all on-module power supplies are working properly. |

| NOSEQ | - | - | No function. |

| RESIN | Input | Reset | Active low reset, gated to POR_B. |

| JTAGEN | Input | JTAG Select | Low for normal operation, high for CPLD JTAG access. |

Default PS MIO Mapping

| PS MIO | Function | B2B Pin | Connected to | PS MIO | Function | B2B Pin | Connected to | |

|---|---|---|---|---|---|---|---|---|

| 0 | SPI0 | - | U7-B2, CLK | 40..45 | - | - | Not connected | |

| 1 | SPI0 | - | U7-D2, DO/IO1 | 46 | SD | JM1-17 | B2B, SD_DAT0 | |

| 2 | SPI0 | - | U7-C4, WP/IO2 | 47 | SD | JM1-19 | B2B, SD_DAT1 | |

| 3 | SPI0 | - | U7-D4, HOLD/IO3 | 48 | SD | JM1-21 | B2B, SD_DAT2 | |

| 4 | SPI0 | - | U7-D3, DI/IO0 | 49 | SD | JM1-23 | B2B, SD_DAT3 | |

| 5 | SPI0 | - | U7-C2, CS | 50 | SD | JM1-25 | B2B, SD_CMD | |

| 6 | N/A | - | Not connected | 51 | SD | JM1-27 | B2B, SD_CLK | |

| 7 | SPI1 | - | U17-C2, CS | 52 | USB_PHY | - | U18-31, OTG-DIR | |

| 8 | SPI1 | - | U17-D3, DI/IO0 | 53 | USB_PHY | - | U18-31, OTG-DIR | |

| 9 | SPI1 | - | U17-D2, DO/IO1 | 54 | USB_PHY | - | U18-5, OTG-DATA2 | |

| 10 | SPI1 | - | U17-C4, WP/IO2 | 55 | USB_PHY | - | U18-2, OTG-NXT | |

| 11 | SPI1 | - | U17-D4, HOLD/IO3 | 56 | USB_PHY | - | U18-3, OTG-DATA0 | |

| 12 | SPI1 | - | U17-B2, CLK | 57 | USB_PHY | - | U18-4, OTG-DATA1 | |

| 13..20 | eMMC | - | U6, MMC-D0..D7 | 58 | USB_PHY | - | U18-29, OTG-STP | |

| 21 | eMMC | - | U6, MMC-CMD | 59 | USB_PHY | - | U18-6, OTG-DATA3 | |

| 22 | eMMC | - | U6, MMC-CLKR | 60 | USB_PHY | - | U18-7, OTG-DATA4 | |

| 23 | eMMC | - | U6, MMC-RST | 61 | USB_PHY | - | U18-9, OTG-DATA5 | |

| 24 | ETH | - | U8, ETH-RST | 62 | USB_PHY | - | U18-10, OTG-DATA6 | |

| 25 | USB_PHY | - | U18, OTG-RST | 63 | USB_PHY | - | U18-13, OTG-DATA7 | |

| 26 | MIO | JM1-95 | B2B | 64 | ETH | - | U8-53, ETH-TXCK | |

| 27 | MIO | JM1-93 | B2B | 65..66 | ETH | - | U8-50..51, ETH-TXD0..1 | |

| 28 | MIO | JM1-99 | B2B | 67..68 | ETH | - | U8-54..55, ETH-TXD2..3 | |

| 29 | MIO | JM1-99 | B2B | 69 | ETH | - | U8-56, ETH-TXCTL | |

| 30 | MIO | JM1-92 | B2B | 70 | ETH | - | U8-46, ETH-RXCK | |

| 31 | MIO | JM1-85 | B2B | 71..72 | ETH | - | U8-44..45, ETH-RXD0..1 | |

| 32 | MIO | JM1-91 | B2B | 73..74 | ETH | - | U8-47..48, ETH-RXD2..3 | |

| 33 | MIO | JM1-87 | B2B | 75 | ETH | - | U8-43, ETH-RXCTL | |

| 34..37 | N/A | - | Not connected | 76 | ETH | - | U8-7, ETH-MDC | |

| 38 | I2C | - | U10-12, SCL | 77 | ETH | - | U8-8, ETH-MDIO | |

| 39 | I2C | - | U10-19, SDA |

Gigabit Ethernet

On-board Gigabit Ethernet PHY is provided with Marvell Alaska 88E1512 chip. The Ethernet PHY RGMII interface is connected to the Zynq Ethernet0 PS GEM0. I/O voltage is fixed at 1.8V for HSTL signaling. SGMII (SFP copper or fiber) can be used directly with the Ethernet PHY, as the SGMII pins are available on the B2B connector JM3. The reference clock input of the PHY is supplied from an on-board 25MHz oscillator (U11), the 125MHz output clock is left unconnected.

Ethernet PHY connection

| PHY Pin | ZYNQ PS | ZYNQ PL | Notes |

|---|---|---|---|

| MDC/MDIO | MIO76, MIO77 | - | - |

| LED0 | - | K8 | Can be routed via PL to any free PL I/O pin in B2B connector. |

| LED1 | - | K8 | CPLD pin 17. ??? |

| LED2 | - | - | Not connected. |

| CONFIG | - | - | 1.8V |

| RESETn | MIO24 | - | - |

| RGMII | MIO64..MIO75 | - | - |

| SGMII | - | - | on B2B JM3. |

| MDI | - | - | on B2B JM3. |

| Page break |

|---|

USB Interface

USB PHY is provided by Microchip USB3320. The ULPI interface is connected to the Zynq PS USB0. I/O voltage is fixed at 1.8V. Reference clock input for the USB PHY is supplied by the on-board 25.000000 MHz oscillator (U15).

USB PHY connection

| PHY Pin | ZYNQ Pin | B2B Name | Notes |

|---|---|---|---|

| ULPI | MIO52..63 | - | Zynq USB0 MIO pins are connected to the USB PHY. |

| REFCLK | - | - | 52.000000 MHz from on-board oscillator (U14). |

| REFSEL[0..2] | - | - | Reference clock frequency select, all set to GND selects 52.000000 MHz. |

| RESETB | MIO25 | - | Active low reset. |

| CLKOUT | MIO52 | - | Connected to 1.8V, selects reference clock operation mode. |

| DP, DM | - | OTG_D_P, OTG_D_N | USB data lines routed to B2B connector JM3 pins 47 and 49. |

| CPEN | - | VBUS_V_EN | External USB power switch active high enable signal, routed to JM3 pin 17. |

| VBUS | - | USB_VBUS | Connect to USB VBUS via a series of resistors, see reference schematics, routed to JM3 pin 55. |

| ID | - | OTG_ID | For an A-device connect to ground, for a B-device left floating. routed from JM3 pin 23. |

I2C Interface

On-board I2C devices are connected to MIO38 (SCL) and MIO39 (SDA) which are configured as I2C1 by default. I2C addresses for on-board devices are listed in the table below:

| I2C Device | I2C Address | Notes |

|---|---|---|

Si5338A PLL | 0x70 | - |

On-board Peripherals

2 x 32 MByte Quad SPI Flash Memory

Two quad SPI compatible serial bus flash N25Q256A memory chips are provided for FPGA configuration file storage. After configuration completes the remaining free memory can be used for application data storage. All four SPI data lines are connected to the FPGA allowing x1, x2 or x4 data bus widths to be used. The maximum data transfer rate depends on the bus width and clock frequency.

Programmable Clock Generator

There is a Silicon Labs I2C programmable clock generator Si5338A (U10) chip on the module. It's output frequencies can be programmed using the I2C bus address 0x70 or 0x71. Default address is 0x70, IN4/I2C_LSB pin must be set high for address 0x71.

A 25.000000 MHz oscillator is connected to the pin IN3 and is used to generate the output clocks. The oscillator has its output enable pin permanently connected to 1.8V power rail, thus making output frequency available as soon as 1.8V is present. Three of the Si5338 clock outputs are connected to the FPGA. One is connected to a logic bank and the other two are connected to the GTR banks. It is possible to use the clocks connected to the GTR bank in the user's logic design. This is achieved by instantiating a IBUFDSGTE buffer in the design.

The default frequency of each clock at start up is detailed in the table 7.

Once running, the frequency and other parameters can be changed by programming the device using the I2C bus connected between the FPGA (master) and clock generator (slave). Logic needs to be generated inside the FPGA to utilize I2C bus correctly.

| Signal | Frequency | Notes |

|---|---|---|

| IN1/IN2 | - | Not used (external clock signal supply). |

IN3 | 25.000000 MHz | Fixed input clock signal from reference clock generator SiT8008BI-73-18S-25.000000E (U11). |

| IN4 | - | LSB of the default I2C address, wired to ground mean address is 0x70. |

IN5 | - | Not connected. |

IN6 | - | Wired to ground. |

| CLK0 A/B | - | Bank 65 clock input, pins K9 and J9. |

CLK1 A/B | - | MGT reference clock 3 to FPGA Bank 505 MGT. |

CLK2 A/B | - | MGT reference clock 1 to FPGA Bank 505 MGT. |

| CLK3 A/B | - | Not connected. |

Clocking

| Clock Signal | Frequency | Source | Destination | Notes |

|---|---|---|---|---|

| PS_CLK | 33.333333 MHz | U32 | FPGA bank 503, pin R16 | PS_REF_CLK |

| CLKIN_P | User selectable | JM3-32 | U10, IN1, pin 1 | |

| CLKIN_N | User selectable | JM3-34 | U10, IN2, pin 2 | |

| CLK0_P | U10, CLK0A | FPGA bank 65, pin J9 | ||

CLK0_N | U10, CLK0B | FPGA bank 65, pin K9 | ||

| CLK_25M | 25.000000 MHz | U11, CLK | U10, IN3, pin 3 U8, XTAL_IN, pin 34 |

ETH_CLK |

| B505_CLK0_P | User selectable | JM3-31 | FPGA bank 505, pin F23 | |

| B505_CLK0_N | User selectable | JM3-33 | FPGA bank 505, pin F24 | |

| B505_CLK1_P | U10, CLK2A | FPGA bank 505, pin E21 | ||

| B505_CLK1_N | U10, CLK2B | FPGA bank 505, pin E22 | ||

| B505_CLK3_P | U10, CLK1A | FPGA bank 505, pin A21 | ||

| B505_CLK3_N | U10, CLK1B | FPGA bank 505, pin A22 | ||

| OTG-RCLK | 52.000000 MHz | U14, CLK | U18, pin 26 | REFCLK |

GTR Transceivers

The Xilinx Zynq UltraScale+ device used on the TE0820 module has 4 GTR transceivers. All 4 are wired directly to B2B connector JM3. There are also 3 clock sources for the transceivers. B505_CLK0 is connected directly to B2B connector JM3, so the clock can be provided by the carrier board. Other two clocks B505_CLK1 and B505_CLK3 are provided by the on-board clock generator (U10). As there are no capacitive coupling of the data and clock lines that are connected to the connectors, these may be required on the user’s PCB depending on the application.

On-board LEDs

There is one on-board red LED D1 wired to the PS DONE signal.

Power and Power-on Sequence

Power Supply

Power supply with minimum current capability of 3A for system startup is recommended.

Power Consumption

| Power Input | Typical Current |

|---|---|

| VIN | TBD* |

| 3.3VIN | TBD* |

*TBD - To be determined.

Power-on Sequence

For highest efficiency of on-board DC-DC regulators, it is recommended to use same 3.3V power source for both VIN and 3.3VIN power rails. Although VIN and 3.3VIN can be powered up in any order, it is recommended to power them up simultaneously.

It is important that all carrier board I/Os are 3-stated at power-on until System Controller CPLD sets PGOOD signal high (B2B connector JM1, pin 30), or 3.3V is present on B2B connector JM2 pins 10 and 12, meaning that all on-module voltages have become stable and module is properly powered up.

See Xilinx datasheet DS925 for additional information. User should also check related carrier board documentation when choosing carrier board design for TE0715 module.

Power Rails

| Power Rail Name on B2B Connector | JM1 Pins | JM2 Pins | Direction | Notes |

|---|---|---|---|---|

| VIN | 1, 3, 5 | 2, 4, 6, 8 | Input | Supply voltage from the carrier board. |

| 3.3V | - | 10, 12 | Output | Internal 3.3V voltage level. |

| 3.3VIN | 13, 15, 91 | - | Input | Supply voltage from the carrier board. |

| VCCO_64 | - | 7, 9 | Input | High performance I/O bank voltage. |

| VCCO_65 | - | 5 | Input | High performance I/O bank voltage. |

| VCCO_66 | 9, 11 | - | Input | High performance I/O bank voltage. |

Bank Voltages

| Bank | Name on Schematic | Voltage | Range |

|---|---|---|---|

| 64 HP | VCCO_64 | User | HP: 1.0V to 1.8V |

| 65 HP | VCCO_65 | User | HP: 1.0V to 1.8V |

| 66 HP | VCCO_66 | User | HP: 1.0V to 1.8V |

| 500 PSMIO | VCCO_PSIO0_500 | 1.8V | - |

| 501 PSMIO | VCCO_PSIO1_501 | 3.3V | - |

| 502 PSMIO | VCCO_PSIO2_502 | 1.8V | - |

| 503 PSCONFIG | VCCO_PSIO3_503 | 1.8V | - |

| 504 PSDDR | VCCO_PSDDR_504 | 1.2V | - |

See Xilinx Zynq UltraScale+ datasheet DS925 for the voltage ranges allowed.

Board to Board Connectors

| Include Page | ||||

|---|---|---|---|---|

|

Variants Currently In Production

Module Variant | SoC | RAM | SPI Flash | Temperature Range |

|---|---|---|---|---|

| TE0820-01-02CG-1E | XCZU2CG-1SFVC784E | 1 GByte DDR4 | 64 MByte | Extended |

| TE0820-01-03CG-1E | XCZU3CG-1SFVC784E | 1 GByte DDR4 | 64 MByte | Extended |

| TE0820-01-04CG-1E | XCZU4CG-1SFVC784E | 1 GByte DDR4 | 64 MByte | Extended |

| TE0820-01-02EG-1E | XCZU2EG-1SFVC784E | 1 GByte DDR4 | 64 MByte | Extended |

| TE0820-01-03EG-1E | XCZU3EG-1SFVC784E | 1 GByte DDR4 | 64 MByte | Extended |

| TE0820-01-04EV-1E | XCZU4EV-1SFVC784E | 1 GByte DDR4 | 64 MByte | Extended |

On-board LEDs

Default MIO Mapping

Gigabit Ethernet

USB Interface

I2C Interface

Boot Modes

On-board Peripherals

Processing System (PS) Peripherals

Clocking

Power and Power-on sequence

Power Supply

Power-on sequence

Power Rails

Bank Voltages

Board to Board Connectors

Technical Specifications

Absolute Maximum Ratings

Parameter | Min | Max | Units | Notes |

|---|

VIN supply voltage | -0.3 | 7.0 | V | See EN6347QI and TPS82085SIL datasheets. |

| 3.3VIN |

| supply voltage | -0.1 | 3. |

| 75 | V |

| See LCMXO2-256HC and TPS27082L datasheet. |

| PS I/O |

| supply voltage, VCCO_PSIO | -0.5 | 3. |

| 630 | V |

| Xilinx document |

| DS925 |

| PS I/O input voltage |

| -0. |

| 5 | VCCO_ |

| PSIO + 0.55 | V |

| Xilinx document |

| DS925 | |

| HP I/O bank supply voltage, VCCO | -0.5 |

| 2. |

| 0 | V |

| Xilinx document DS925 | |||

| HP I/O bank input voltage | -0.55 | VCCO + 0.55 | V |

| Xilinx document |

| DS925 | ||||

Voltage on module JTAG pins | -0.4 | VCCO_0 + 0.55 | V | VCCO_0 is 1.8V or 3.3V nominal |

| . Xilinx document |

| DS925 | |||

Storage temperature | -40 | +85 | °C |

| See eMMC datasheet. |

Recommended Operating Conditions

| Parameter | Min | Max | Units | Notes |

|---|

| VIN supply voltage | 2.5 | 6.6 | V | See TPS82085S datasheet |

| 3 |

| .3VIN supply voltage | 2.375 | 3. |

| 6 | V |

| See LCMXO2-256HC datasheet | ||||

| PS I/O supply voltage, VCCO_PSIO | 1.710 | 3.465 | V | Xilinx document DS925 |

| PS I/O input voltage | –0.20 | VCCO_PSIO + 0.20 | V | Xilinx document DS925 |

| HP I/O banks supply voltage, VCCO | 1.14 | 3.465 | V |

| Xilinx document |

| DS925 |

| HP I/O banks input voltage |

| -0.20 | VCCO + 0.20 | V |

| Xilinx document |

| DS925 | ||||

| Voltage on module JTAG pins | 3.135 | 3.465 | V | For a module variant with |

| 3.3V CONFIG |

| bank option |

| Note |

|---|

| Please check See Xilinx datasheet DS181 for complete list of DS925 for more information about absolute maximum and recommended operating ratings for the Artix-7Zynq UltraScale+ chips. |

Operating Temperature Ranges

Extended grade: -40°C to +85°C.

Module operating temperature range depends also on customer design and cooling solution. Please contact us for options.

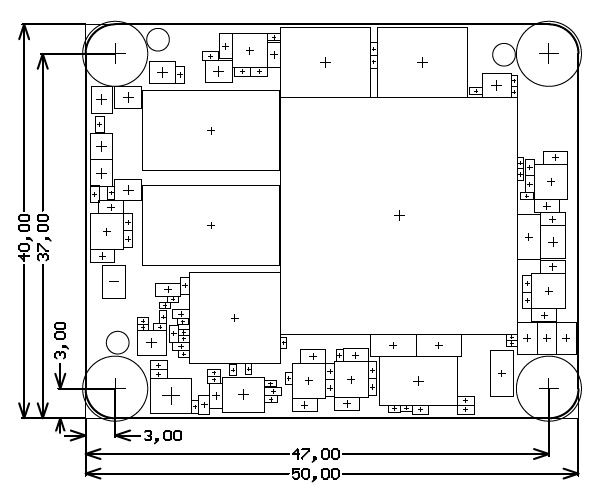

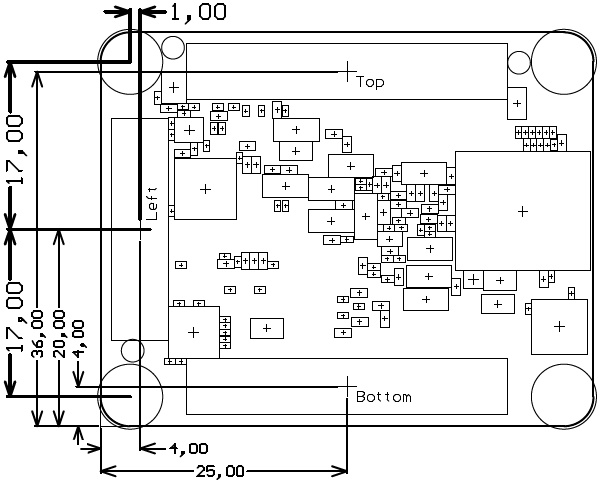

Physical Dimensions

Module size: 50 mm × 40 mm. Please download the assembly diagram for exact numbers.

Mating height with standard connectors: 8 mm

PCB thickness: 1.6 mm

Highest part on PCB: approximately 5 mm. Please download the step model for exact numbers.

All dimensions are shown in mmmillimeters. Additional sketches, drawings and schematics can be found here.

Weight

...

...

| Variant | Weight in g | Note |

|---|---|---|

| - | - | Plain Module |

Boot Process

By default the TE-0820 supports SPI and SD Card boot modes which is controlled by MODE input signal from the B2B JM1 connector pin 32.

MODE Signal State | Boot Mode |

|---|---|

High or open | SPI Flash |

Low or ground | SD Card |

Operating Temperature Ranges

Commercial grade modules

All parts are at least commercial temperature range of 0 °C to +70 °C. The module operating temperature range depends on customer design and cooling solution. Please contact us for options.

Industrial grade modules

All parts are at least industrial temperature range of -40 °C to +85 °C. The module operating temperature range depends on customer design and cooling solution. Please contact us for options.

Weight

...

Revision History

Hardware Revision History

...

Hardware revision number is printed written on the PCB board next to the module model number separated by the dash.

...

Date | Revision | Authors | Description |

|---|---|---|---|

| 2017-06-05-10 | Jan Kumann | Initial version. |

...