Page History

...

Additional Sources

| Type | Location | Notes | |||

|---|---|---|---|---|---|

| init.sh | <design name>/misc/init_script | Additional Initialization Script for Linux |

Prebuilt

| HTML |

|---|

<!-- <table width="100%"> <tr> <th>File </th> <th>File-Extension</th> <th>Description </th> </tr> <tr> <td>BIF-File </td> <td>*.bif </td> <td>File with description to generate Bin-File </td> </tr> <tr> <td>BIN-File </td> <td>*.bin </td> <td>Flash Configuration File with Boot-Image (Zynq-FPGAs) </td> </tr> <tr> <td>BIT-File </td> <td>*.bit </td> <td>FPGA Configuration File </td> </tr> <tr> <td>DebugProbes-File </td> <td>*.ltx </td> <td>Definition File for Vivado/Vivado Labtools Debugging Interface </td> </tr> <tr> <td>Debian SD-Image </td> <td>*.img </td> <td>Debian Image for SD-Card </td> </tr> <tr> <td>Diverse Reports </td> <td> --- </td> <td>Report files in different formats </td> </tr> <tr> <td>Hardware-Platform-Specification-Files</td> <td>*.hdf </td> <td>Exported Vivado Hardware Specification for SDK/HSI </td> </tr> <tr> <td>LabTools Project-File </td> <td>*.lpr </td> <td>Vivado Labtools Project File </td> </tr> <tr> <td>MCS-File </td> <td>*.mcs </td> <td>Flash Configuration File with Boot-Image (MicroBlaze or FPGA part only) </td> </tr> <tr> <td>MMI-File </td> <td>*.mmi </td> <td>File with BRAM-Location to generate MCS or BIT-File with *.elf content (MicroBlaze only) </td> </tr> <tr> <td>OS-Image </td> <td>*.ub </td> <td>Image with Linux Kernel (On Petalinux optional with Devicetree and RAM-Disk) </td> </tr> <tr> <td>Software-Application-File </td> <td>*.elf </td> <td>Software Application for Zynq or MicroBlaze Processor Systems </td> </tr> <tr> <td>SREC-File </td> <td>*.srec </td> <td>Converted Software Application for MicroBlaze Processor Systems </td> </tr> </table> --> |

...

Trenz Electronic provides a tcl based built environment based on Xilinx Design Flow.

See also:Vivado/SDK/SDSoC

...

- Open Serial Console (e.g. putty)

- Speed: 115200

- COM Port: Win OS, see device manager, Linux OS see dmesg |grep tty (UART is *USB1)

- Linux Console:

Note: Wait until Linux boot finished For Linux Login use:- User Name: root

- Password: root

- You can use Linux shell now.

- I2C 0 Bus type: i2cdetect -y -r 0

- ETH0 works with UDHCPC udhcpc

- ETH1 must be configured manually

- ifconfig eth1 up

- ifconfig eth1 <ip>

Note for Ping test disable ETH0

- RTC check: dmesg | grep rtc

...

| HTML |

|---|

<!-- Description of Block Design, Constrains... BD Pictures from Export... --> |

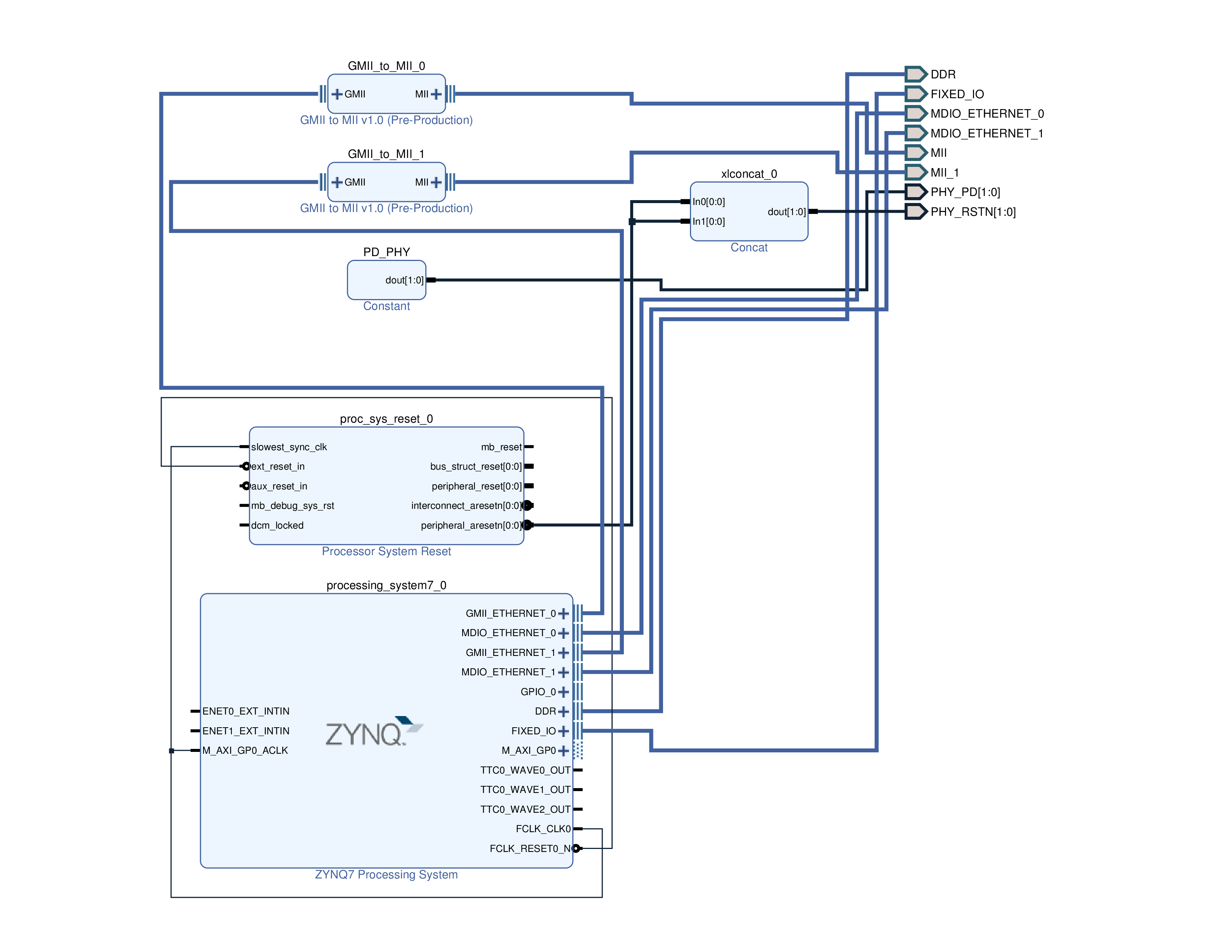

Block Design

PS Interfaces

| Type | Note |

|---|---|

| DDR | --- |

| QSPI | MIO |

| CAN1 | MIO |

| ETH0 | EMIO |

| ETH1 | EMIO |

| SD0 | MIO |

| UART1 | MIO |

| I2C0 | MIO |

| SPI1 | MIO |

| GPIO | MIO/EMIO |

| TIMER0 | EMIO |

Constrains

Basic module constrains

| Code Block | ||||

|---|---|---|---|---|

| ||||

set_# # Common bitgen related settings # set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design] set_property CONFIG_VOLTAGE 3.3 [current_design] set_property CFGBVS VCCO [current_design] set_property BITSTREAM.CONFIG.USR_ACCESS TIMESTAMP [current_design] |

...

| Code Block | ||||||||

|---|---|---|---|---|---|---|---|---|

| ||||||||

############# #ETH0/ETH1 ##### #pwr_down set_property PACKAGE_PIN K2L21 [get_ports {fclkPHY_PD[0]}] set_property IOSTANDARDPACKAGE_PIN LVCMOS18R20 [get_ports {fclkPHY_PD[01]}] #rst_n set_property CLOCKPACKAGE_DEDICATED_ROUTEPIN FALSEM15 [get_netsports fclk{PHY_IBUFRSTN[0]] |

Software Design - SDK/HSI

| HTML |

|---|

<!--

optional chapter

separate sections for different apps

--> |

For SDK project creation, follow instructions from:

Application

FSBL

Xilinx default FSBL

U-Boot

U-Boot.elf is generated with PetaLinux. SDK/HSI is used to generate Boot.bin.

Software Design - PetaLinux

| HTML |

|---|

<!--

optional chapter

--> |

Description currently not available.

Config

U-Boot

Device Tree

| Code Block | ||

|---|---|---|

| ||

/include/ "system-conf.dtsi"

/ {

};

|

Kernel

...

}]

set_property PACKAGE_PIN R16 [get_ports {PHY_RSTN[1]}]

#io standard

set_property IOSTANDARD LVCMOS33 [get_ports {PHY*}]

set_property IOSTANDARD LVCMOS33 [get_ports mdio_*]

set_property IOSTANDARD LVCMOS33 [get_ports MDIO_*]

set_property IOSTANDARD LVCMOS33 [get_ports {MII_*}]

#pullup/down for PHY address 1

set_property PULLUP true [get_ports MII_col]

set_property PULLDOWN true [get_ports {MII_rxd[0]}]

set_property PULLDOWN true [get_ports {MII_rxd[1]}]

set_property PULLDOWN true [get_ports {MII_rxd[2]}]

set_property PULLDOWN true [get_ports {MII_rxd[3]}]

#pullup/down for PHY address 2

set_property PULLDOWN true [get_ports MII_1_col]

set_property PULLUP true [get_ports {MII_1_rxd[0]}]

set_property PULLDOWN true [get_ports {MII_1_rxd[1]}]

set_property PULLDOWN true [get_ports {MII_1_rxd[2]}]

set_property PULLDOWN true [get_ports {MII_1_rxd[3]}]

#############

#ETH0

#####

set_property PACKAGE_PIN M16 [get_ports mdio_ethernet_0_mdio_io]

set_property PACKAGE_PIN P16 [get_ports MDIO_ETHERNET_0_mdc]

set_property PACKAGE_PIN M22 [get_ports {MII_txd[3]}]

set_property PACKAGE_PIN K21 [get_ports {MII_txd[2]}]

set_property PACKAGE_PIN M17 [get_ports {MII_txd[1]}]

set_property PACKAGE_PIN J22 [get_ports {MII_txd[0]}]

set_property PACKAGE_PIN J20 [get_ports {MII_rxd[3]}]

set_property PACKAGE_PIN J18 [get_ports {MII_rxd[2]}]

set_property PACKAGE_PIN K18 [get_ports {MII_rxd[1]}]

set_property PACKAGE_PIN L17 [get_ports {MII_rxd[0]}]

set_property PACKAGE_PIN L16 [get_ports MII_col]

set_property PACKAGE_PIN N15 [get_ports MII_crs]

set_property PACKAGE_PIN L18 [get_ports MII_rx_clk]

set_property PACKAGE_PIN P15 [get_ports MII_rx_dv]

set_property PACKAGE_PIN P17 [get_ports MII_rx_er]

set_property PACKAGE_PIN K19 [get_ports MII_tx_clk]

set_property PACKAGE_PIN J21 [get_ports MII_tx_en]

#############

#ETH1

#####

set_property PACKAGE_PIN T16 [get_ports mdio_ethernet_1_mdio_io]

set_property PACKAGE_PIN T17 [get_ports MDIO_ETHERNET_1_mdc]

set_property PACKAGE_PIN R21 [get_ports {MII_1_txd[3]}]

set_property PACKAGE_PIN P22 [get_ports {MII_1_txd[2]}]

set_property PACKAGE_PIN P21 [get_ports {MII_1_txd[1]}]

set_property PACKAGE_PIN N22 [get_ports {MII_1_txd[0]}]

set_property PACKAGE_PIN T19 [get_ports {MII_1_rxd[3]}]

set_property PACKAGE_PIN T18 [get_ports {MII_1_rxd[2]}]

set_property PACKAGE_PIN R19 [get_ports {MII_1_rxd[1]}]

set_property PACKAGE_PIN R18 [get_ports {MII_1_rxd[0]}]

set_property PACKAGE_PIN P20 [get_ports MII_1_col]

set_property PACKAGE_PIN N18 [get_ports MII_1_crs]

set_property PACKAGE_PIN M19 [get_ports MII_1_rx_clk]

set_property PACKAGE_PIN N17 [get_ports MII_1_rx_dv]

set_property PACKAGE_PIN P18 [get_ports MII_1_rx_er]

set_property PACKAGE_PIN N19 [get_ports MII_1_tx_clk]

set_property PACKAGE_PIN M21 [get_ports MII_1_tx_en]

|

Software Design - SDK/HSI

| HTML |

|---|

<!--

optional chapter

separate sections for different apps

--> |

For SDK project creation, follow instructions from:

Application

FSBL

Xilinx default FSBL

U-Boot

U-Boot.elf is generated with PetaLinux. SDK/HSI is used to generate Boot.bin.

Software Design - PetaLinux

| HTML |

|---|

<!--

optional chapter

--> |

Description currently not available.

Config

No changes.

U-Boot

No changes.

Device Tree

| Code Block | ||

|---|---|---|

| ||

/include/ "system-conf.dtsi"

/ {

};

/* ETH PHY */

&gem0 {

phy-mode = "mii";

status = "okay";

ethernet_phy0: ethernet-phy@0 {

// compatible = "marvell,88e1510";

device_type = "ethernet-phy";

reg = <1>;

};

};

&gem1 {

phy-mode = "mii";

status = "okay";

local-mac-address = [00 0a 35 00 1e 01];

ethernet_phy1: ethernet-phy@1 {

// compatible = "marvell,88e1510";

device_type = "ethernet-phy";

reg = <2>;

};

};

/* RTC */

&i2c0 {

rtc@56 { // Real Time Clock

compatible = "rv3029c2";

reg = <0x56>;

};

};

|

Kernel

Activate:

- RTC_DRV_RV3029C2

Rootfs

Activate:

- I2C-tools

Applications

startup

Script App to load init.sh from SD Card if available.

...

Overview

Content Tools