Page History

Achtung beim Schritt HDL generate

Optionen im Plattformdesigner, die sinnvoll wären eingestellt zu werden:

...

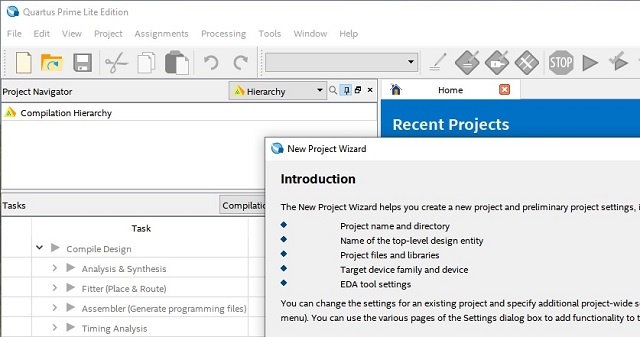

Quartus places the folder db, two files HPSexample.qpf and HPSexample.qsf into the project folder

and the setup is accomplished.

Plattform Designer

This programm creates inside the project folder the following

HPSexample.sopinfo -

PlattformEditorHPS.qip

files and

(hps_isw_)handoff folder.

The contains paths for all of the files for an IP core, the

- Use the Plattform Designer to configure the resources needed to boot the HPS

(program generates the files needed to connect and configures the HPS so that it gets connected to the physical board resources.

The basic storage resources the HPS needs are System Memory and SD card access)- Connect , to communicate the basic interfaces (are Uart and i²c) of the HPS to the board resources.

These files are:

- HPSexample.sopinfo - describes all of the components and connections in your system and

parameterization of each component in the system

- PlattformEditorHPS.qip - The contains paths for all of the files for an IP core

- - Compile the project to get the required files and folders for the next steps

HPSexample.sopinfo / PlattformEditorHPS.qip file and (hps_isw_)handoff folder - Folder containing general and SoC / board specific source files for generating the bootloaders

The Plattform Designer can be opened via Tools → Plattform Designer and later on, the output must be added into

project. Instead, both steps can be performed through adding a Qsys System File to the project.

...

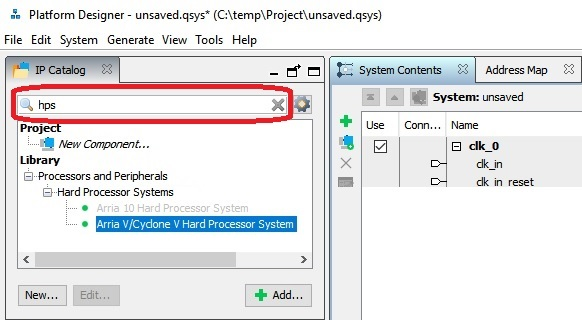

To configure the resources and interfaces of the HPS, it needs first to be added into the system,

Type into the search field in the upper left column hps.

Select Arria V/Cyclone V Hard Processor System via double click from the tree:

Library - Processors and Peripherals - Hard Processor Systems - Arria V/Cyclone V Hard Processor System

The window - Arria V/Cyclone V Hard Processor System - hps_0 - opens. To setup the peripheral of the HPS ,

transfer everything of the following list into the tabs mentioned. Everything not mentioned must be left untouched.

...

The HPS is nearly configures, at last apply some auto functions:

System → Assign Base Addresses

System → Assign Interrupt Numbers

System → Assign Custom Instruction Opcodes

System → Create Global Reset Network

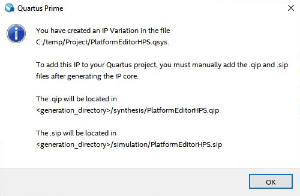

Achtung beim Schritt HDL generate

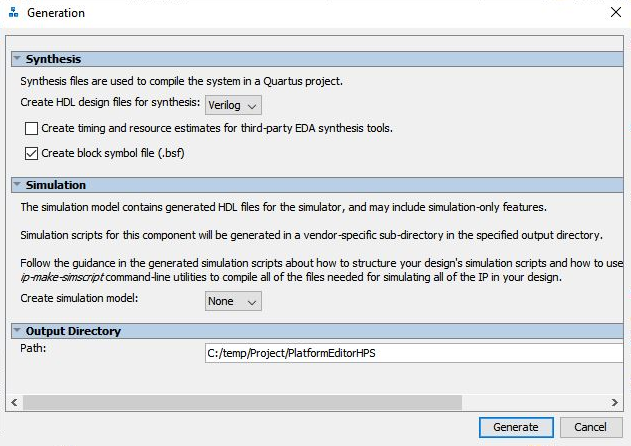

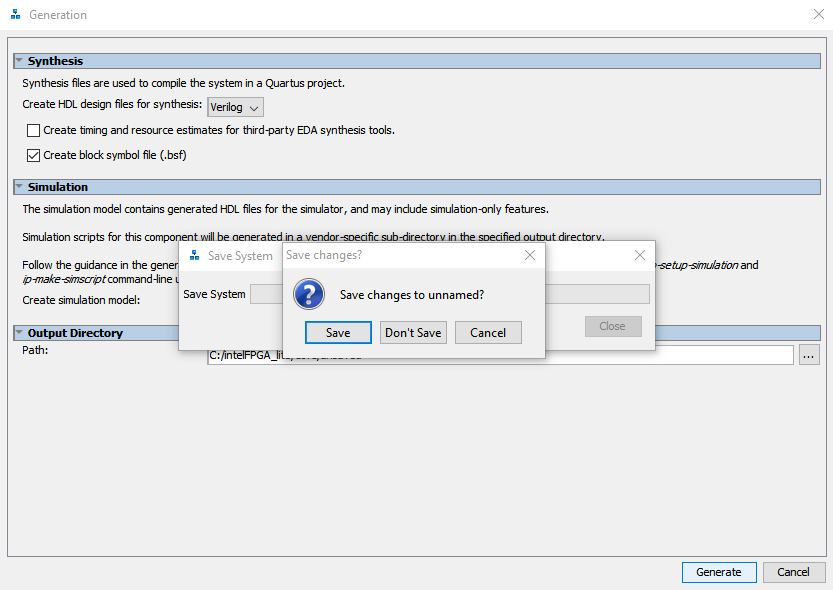

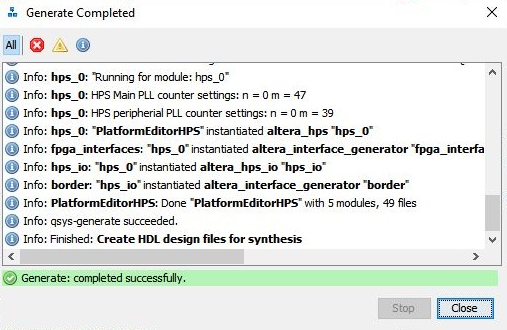

The Hardware Description language file is obtained by pressing Generate HDL in the bottom right corner of the

window.

A new window opens, - Generation. In this window, under Synthesis, select via Dropdown Menu in which

Hardware Language your HDL will be created, Verilog or VHDL, check Create block symbole file (.bsf) and

uncheck Create timing and resource estimate... .

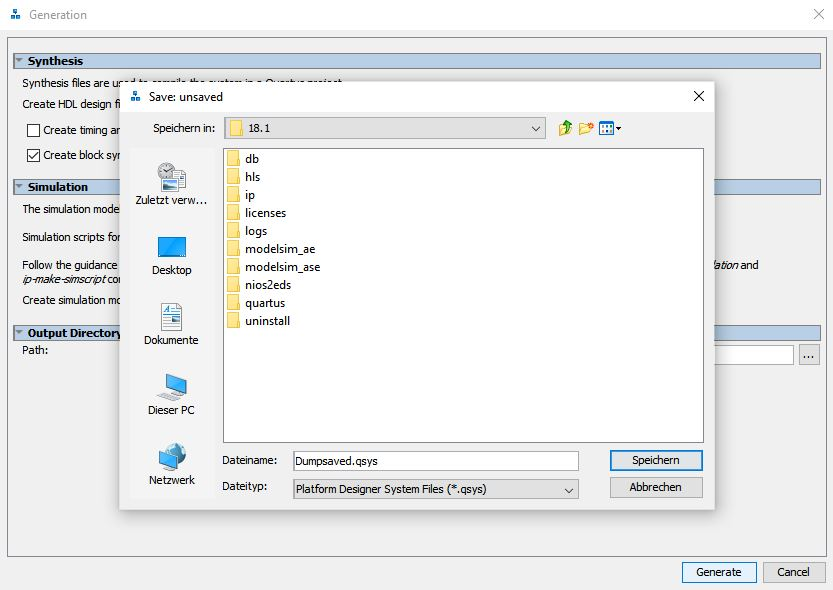

Press in the bottom left Generate and the a saving dialogue opens, reminding to save the design. Name the file, this

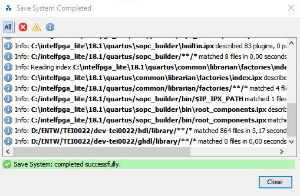

guide designates the file PlatformEditorHPS.qsys , press Save and wait until the design is saved. The window shows

the message - Save System: Completed successfully.

...

Close the Plattform Designer by pressing Finish. A notification appears, reminding to add files into the project,

press OK.

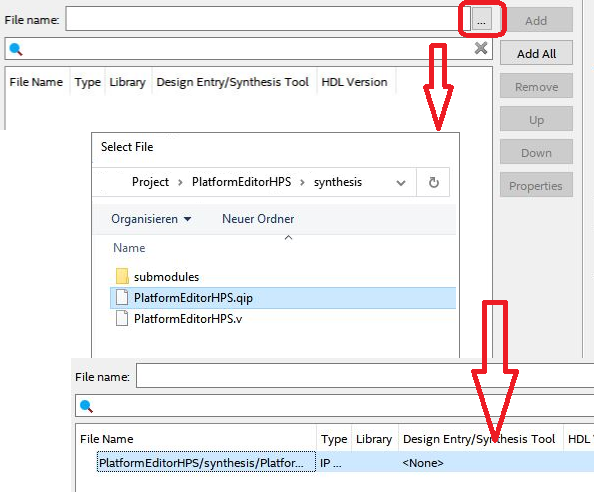

To add the file(s), open a new dialogue window via Project → Add/Remove Files in Project ... . The following

Add File PlattformEditorHPS.qip into Quartus via Project → Add/Remove Files in Project ...

window Settings - HPSexample opens

Hit Rectangle ... and select path:

C:\temp\Project\PlatformEditorHPS\synthesis click open

In window Settings - HPSexample click OK

window opens, in it, click onto to button with 3 dots / inside the red rectangle.

The - Select File - window opens, point along the path project > PlatformEditorHPS > synthesis to the file PlatformEditorHPS.qsys,

double click onto it to select it, the window closes, close the - Settings - HPSexample - window by clicking the button OK in the

bottom left.

In Project Navigator, upper left column in Quartus, In Project Navigator use the Drop-down Menu for changing from Hierarchy to Files. and right click onto the file to set it on top

...