Page History

...

Only the SD card build requires low level access to the SD card and can therefore only be performed in native Linux environment.

////

...

Intel Quartus Project generation

The first step within the HPS booting procedure is using the tool "Intel Quartus". Within this tool it is necessary to create a new project. After that, it is mandatory to configure the resources (system memory and SD card access) withing the Plattform Designer. After that, connect the basis interfaces (UART, I2C) of the HPS to the board resources and compile the project to create the ".sopinfo", the ".qip" files, and the "handoff" folder. Refer to "Intel Quartus project" for more detailed information.

...

- Compile the project to get the required files and folders for the next steps

HPSexample.sopinfo / PlattformEditorHPS.qip file and (hps_isw_)handoff folder

////

...

Preloader/Bootloader generation

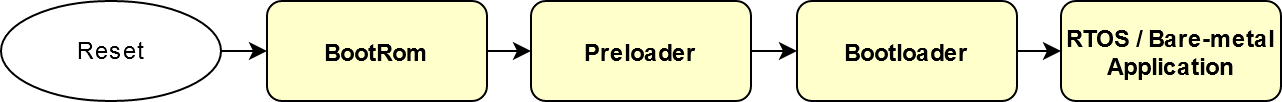

After the generation of the Intel Quartus project generation, it is necessary to handle the System on Chip (SoC) booting. The boot process, according to the next figure, consists of several steps:

- BootROM:

The BootROM is hard coded into the chip. After reset the BootROM code can detect the selected boot source and perform a minimal HPS setup. After that the preloader can be loaded into the On Chip RAM (OCRM) and can be executed.

- Preloader:

While executing the preloader, a further HPS and SDRAM initialization can be done. After that, the bootloader can be loaded and executed.

- Bootloader:

The bootloader loads the linux operating system (OS) or a bare metal application into the RAM and starts them. If a linux OS is loaded, the kernel is loaded which loads the linux root file system.

To generate the preloader and the bootloader, the handoff folder, generated in the first step is used. Refer to "Preloader/Bootloader generation" for more detailed information.

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

- BootROM:

The BootROM is hard coded into the chip. Its purpose is to detect the selected boot source and to perform a minimal HPS setup. After that the preloader can be loaded into the On Chip RAM (OCRM) and can be executed.

- Preloader:

While executing the preloader, a further HPS and SDRAM initialization can be done. After that, the bootloader can be loaded and executed.

- Bootloader:

...

In the second step, the in the first step generated handoff folder is used to generate the preloader and the main bootloader. Refer to "Preloader/Bootloader generation" for more detailed information.////

[preloader-mkpimage.bin u-boot.img]

////

...

Device Tree Blob

...

generation

In the third step, the device tree blob is generated with the ".sopfile" file as input from the Plattform Designer in step 1. Refer to "Device Tree Blob Generation" for more detailed information.

...

SD card setup

In the final step, the SD card setup is created to prepare the boot medium to bring-up the HPS within Intel Cyclone V HPS. Refer to "SD card setup" for more detailed information.

...