Page History

...

...

...

Table of contents

...

...

| outline | true |

|---|

...

...

...

...

...

...

...

...

...

...

...

- script update

...

...

...

...

...

...

- add missing linux Boot.bin

- small update for SI configuration (FSBL)

...

...

...

...

...

...

- 2019.2 update

- Vitis support

- FSBL SI programming procedure update

- petalinux device tree and u-boot update

...

...

...

...

...

...

...

...

...

...

...

...

- TE Script update

- rework of the FSBLs

- some additional Linux features

- MAC from EEPROM

- new assembly variants

- remove special compiler flags, which was needed in 2018.2

- ES2 prebuilt files are not included

...

...

...

...

...

...

...

...

- new assembly variant

...

...

- small petalinux changes

- IO renaming

- PL Design changes

- additional notes for FSBL generated with Win SDK

- changed *.bif

...

...

...

...

...

...

- solved Linux Flash issue

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

- solved JTAG/Linux issue

...

...

...

...

...

...

- initial release

Release Notes and Know Issues

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

...

| anchor | Table_KI |

|---|---|

| title | Known Issues |

...

...

...

...

...

...

...

Note: Design contains also Board Part Files for TE0807 only configuration, this boart part files are not used for this reference design.

Design supports following carriers:

...

| anchor | Table_HWC |

|---|---|

| title | Hardware Carrier |

...

Additional HW Requirements:

...

| anchor | Table_AHW |

|---|---|

| title | Additional Hardware |

...

Optional HW

Not all monitors are supported, also Adapter to other Standard can make drouble.

Design was testet with DELL U2412M

...

Content

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

For general structure and of the reference design, see Project Delivery - Xilinx devices

Design Sources

...

| anchor | Table_DS |

|---|---|

| title | Design sources |

...

Additional Sources

...

| anchor | Table_ADS |

|---|---|

| title | Additional design sources |

...

Prebuilt

...

| hidden | true |

|---|---|

| id | Comments |

Notes :

...

...

...

...

File

...

File-Extension

...

Description

...

Debian SD-Image

...

*.img

...

Debian Image for SD-Card

...

MCS-File

...

*.mcs

...

Flash Configuration File with Boot-Image (MicroBlaze or FPGA part only)

...

MMI-File

...

*.mmi

...

File with BRAM-Location to generate MCS or BIT-File with *.elf content (MicroBlaze only)

...

...

SREC-File

...

*.srec

...

...

...

...

...

...

...

Download

...

...

- Important set new Vivado version link on every Design update of new vivado version!

- Set Link to download folder (Remove ../de/.. ../en/.. from url) for example: https://shop.trenz-electronic.de/Download/?path=Trenz_Electronic/Modules_and_Module_Carriers/4x5/TE0712/Reference_Design/2018.2/test_board

Reference Design is available on:

Design Flow

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

| Note |

|---|

Reference Design is available with and without prebuilt files. It's recommended to use TE prebuilt files for first lunch. |

Trenz Electronic provides a tcl based built environment based on Xilinx Design Flow.

See also:

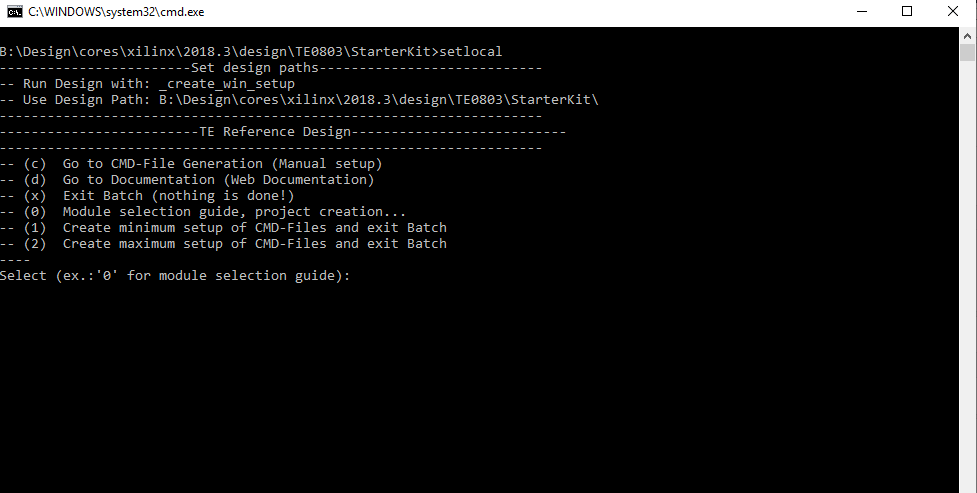

The Trenz Electronic FPGA Reference Designs are TCL-script based project. Command files for execution will be generated with "_create_win_setup.cmd" on Windows OS and "_create_linux_setup.sh" on Linux OS.

TE Scripts are only needed to generate the vivado project, all other additional steps are optional and can also executed by Xilinx Vivado/SDK GUI. For currently Scripts limitations on Win and Linux OS see: Project Delivery Currently limitations of functionality

- _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

- Press 0 and enter to start "Module Selection Guide"

- (optional Win OS) Generate Virtual Drive or use short directory for the reference design (for example x:\<design name>)

- Create Project (follow instruction of the product selection guide), settings file will be configured automatically during this process

- (optional for manual changes) Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

Note: Select correct one, see TE Board Part Files

Important: Use Board Part Files, which ends with *_tebf0808

- (optional for manual changes) Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

- Create XSA and export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

- Create Linux (bl31.elf, uboot.elf and image.ub) with exported XSA

- HDF is exported to "prebuilt\hardware\<short name>"

Note: HW Export from Vivado GUI create another path as default workspace. - Create Linux images on VM, see PetaLinux KICKstart

- Use TE Template from /os/petalinux

- HDF is exported to "prebuilt\hardware\<short name>"

- Add Linux files (bl31.elf, uboot.elf and image.ub) to prebuilt folder

- prebuilt\os\petalinux\<ddr size>" or "prebuilt\os\petalinux\<short name>"

- Generate Programming Files with Vitis

- Run on Vivado TCL: TE::sw_run_vitis -all

Note: Scripts generate applications and bootable files, which are defined in "sw_lib\apps_list.csv" - (alternative) Start SDK with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_vitis

Note: TCL scripts generate also platform project, this must be done manuelly in case GUI is used. See Vitis

- Run on Vivado TCL: TE::sw_run_vitis -all

Launch

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

For basic board setup, LEDs... see: TEBF0808 Getting Started

Programming

| Note |

|---|

Check Module and Carrier TRMs for proper HW configuration before you try any design. |

Xilinx documentation for programming and debugging: Vivado/SDK/SDSoC-Xilinx Software Programming and Debugging

Get prebuilt boot binaries

- _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell

- Press 0 and enter to start "Module Selection Guide"

- Select assembly version

- Validate selection

- Select Create and open delivery binary folder

Note: Folder (<project foler>/_binaries_<Artikel Name>) with subfolder (boot_<app name>) for different applications will be generated

QSPI

Optional for Boot.bin on QSPI Flash and image.ub on SD.

- Connect JTAG and power on carrier with module

- Open Vivado Project with "vivado_open_existing_project_guimode.cmd" or if not created, create with "vivado_create_project_guimode.cmd"

- Type on Vivado TCL Console: TE::pr_program_flash_binfile -swapp u-boot

Note: To program with SDK/Vivado GUI, use special FSBL (zynqmp_fsbl_flash) on setup

optional "TE::pr_program_flash_binfile -swapp hello_te0803" possible - Copy image.ub on SD-Card

- use files from (<project foler>/_binaries_<Articel Name>)/boot_linux from generated binary folder,see: Get prebuilt boot binaries

- or use prebuilt file location, see <design_name>/prebuilt/readme_file_location.txt

- Set Boot Mode to QSPI-Boot and insered SD.

- Depends on Carrier, see carrier TRM.

- TEBF0808 change automatically the Boot Mode to SD, if SD is insered, optional CPLD Firmware without Boot Mode changing for mircoSD Slot is available on the download area

SD

- Copy image.ub and Boot.bin on SD-Card.

- use files from (<project foler>/_binaries_<Articel Name>)/boot_linux from generated binary folder,see: Get prebuilt boot binaries

- or use prebuilt file location, see <design_name>/prebuilt/readme_file_location.txt

- Set Boot Mode to SD-Boot.

- Depends on Carrier, see carrier TRM.

- Insert SD-Card in SD-Slot.

JTAG

Not used on this Example.

Usage

- Prepare HW like described on section 70156402

- Connect UART USB (JTAG XMOD)

- Select SD Card as Boot Mode (or QSPI - depending on step 1)

Note: See TRM of the Carrier, which is used. - (Optional) Insert PCIe Card (detection depends on Linux driver. Only some basic drivers are installed)

- (Optional) Connect Sata Disc

- (Optional) Connect DisplayPort Monitor (List of usable Monitors: https://www.xilinx.com/support/answers/68671.html)

- (Optional) Connect Network Cable

- Power On PCB

Note: 1. ZynqMP Boot ROM loads PMU Firmware and FSBL from SD into OCM, 2. FSBL loads ATF(bl31.elf) and U-boot from SD/QSPI into DDR, 3. U-boot load Linux from SD into DDR.

Linux

- Open Serial Console (e.g. putty)

- Speed: 115200

- COM Port: Win OS, see device manager, Linux OS see dmesg |grep tty (UART is *USB1)

- Linux Console:

Note: Wait until Linux boot finished For Linux Login use:- User Name: root

- Password: root

- You can use Linux shell now.

- I2C 0 Bus type: i2cdetect -y -r 0

- ETH0 works with udhcpc

- USB type "lsusb" or connect USB device

- PCIe type "lspci"

- Option Features

- Webserver to get access to Zynq

- insert IP on web browser to start web interface

- init.sh scripts

- add init.sh script on SD, content will be load automatically on startup (template included in ./misc/SD)

- Webserver to get access to Zynq

Vivado Hardware Manager

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

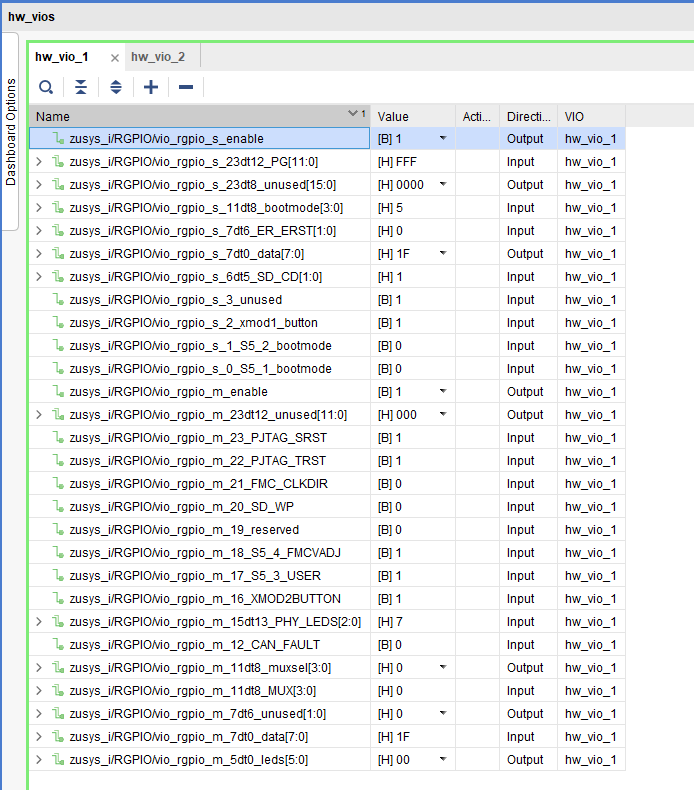

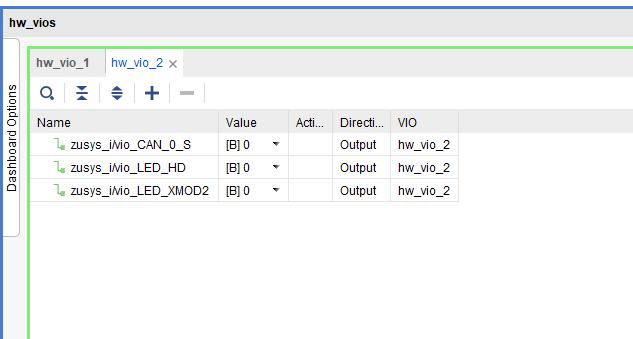

Open Vivado HW-Manager and add VIO signal to dashboard (*.ltx located on prebuilt folder).

RGPIO Interface (Important: CPLD Firmware REV07 or newer is needed) for Control and Monitoring:

- Set Enable to send Write date over RGPIO interface.

- Important use CPLD Firmware REV07 or newer: https://wiki.trenz-electronic.de/display/PD/TEBF0808+CPLD

- Buttons, LEDs, Status...

- Important use CPLD Firmware REV07 or newer: https://wiki.trenz-electronic.de/display/PD/TEBF0808+CPLD

- Set Enable to send Write date over RGPIO interface.

...

| anchor | Figure_VHM |

|---|---|

| title | Vivado Hardware Manager |

...

...

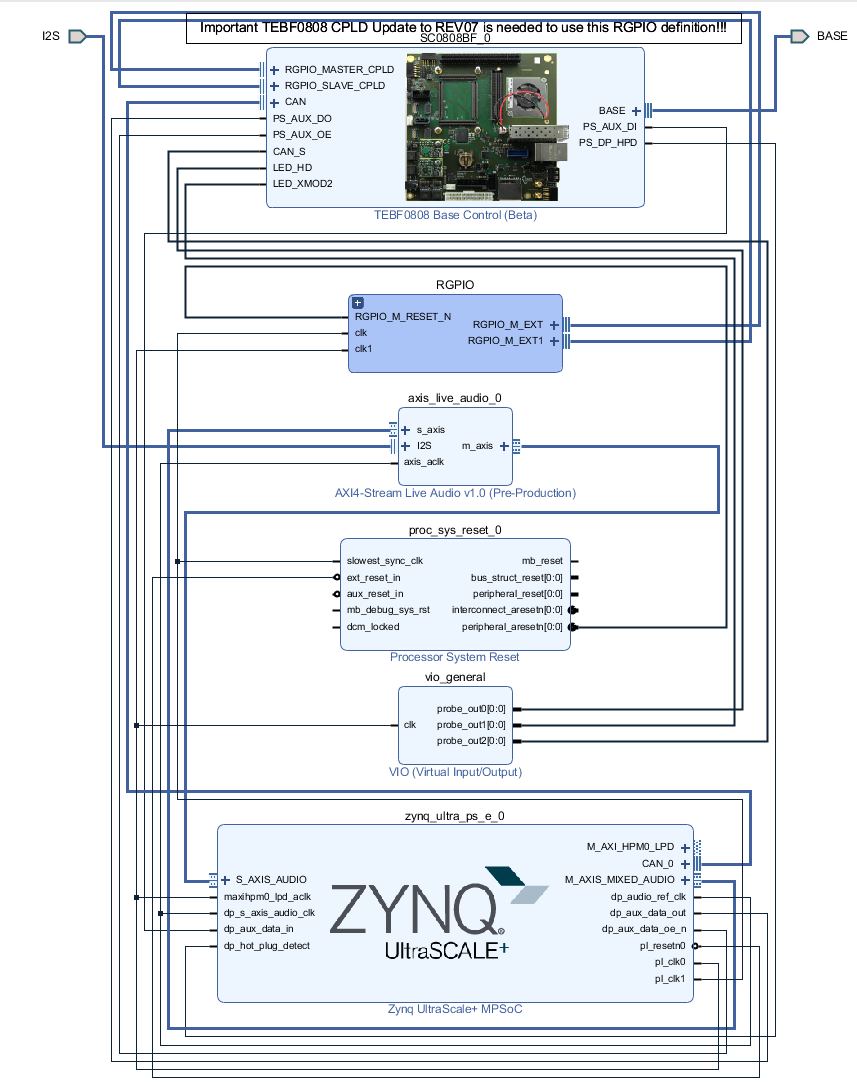

System Design - Vivado

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

Block Design

| Scroll Title | ||||

|---|---|---|---|---|

| ||||

PS Interfaces

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

Activated interfaces:

...

| anchor | Table_PSI |

|---|---|

| title | PS Interfaces |

...

Constrains

Basic module constrains

| Code Block | ||||

|---|---|---|---|---|

| ||||

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property BITSTREAM.CONFIG.UNUSEDPIN PULLNONE [current_design] |

Design specific constrain

...

| language | ruby |

|---|---|

| title | _i_io.xdc |

...

...

...

...

...

...

...

...

...

...

Changes:

...

CONFIG_ENV_IS_NOWHERE=y

...

...

...

Kernel

Start with petalinux-config -c kernel

Changes:

...

CONFIG_CPU_IDLE is not set (only needed to fix JTAG Debug issue)

...

...

...

...

...

...

...

...

...