Page History

| Warning |

|---|

PCN is not ready and TRM style on this page must be checked (style and content) |

...

...

...

...

...

- ...

...

- ...

...

- ...

...

- ...

...

- ...

...

- Industrial-grade Microsemi Polarfire SoC MPFS250T-1FCVG484I

...

...

...

...

...

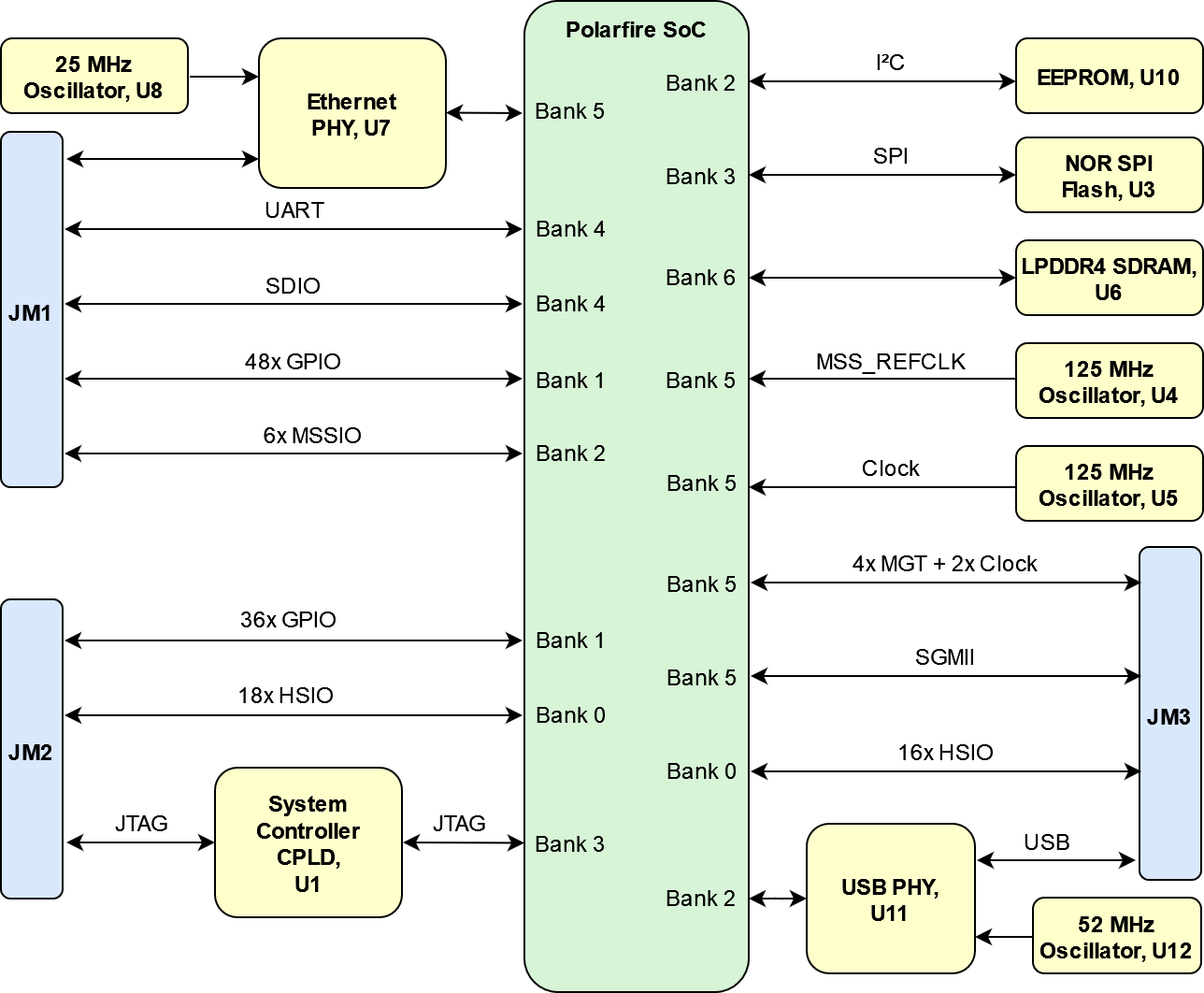

Block Diagram

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

| hidden | true |

|---|---|

| id | Comments |

you must fill the table below with group of Test Point which are indicated as TP in a schematic. If there is no Test Point remarked in the schematic, delete the Test Point section.

Example:

...

1) Direction:

- IN: Input from the point of view of this board.

- OUT: Output from the point of view of this board.

...

| anchor | Table_SIP_TPs |

|---|---|

| title-alignment | center |

| title | Test Points Information |

...

1) Direction:

- IN: Input from the point of view of this board.

- OUT: Output from the point of view of this board.

On-board Peripherals

...

| hidden | true |

|---|---|

| id | Comments |

Notes :

In the on-board peripheral table "chip/Interface" must be linked to the corresponding chapter or subsection by assigning advance link using: #NameOfTheSection

Example:

...

- B2B connector J1

- SoC MIO

...

| anchor | Table_OBP |

|---|---|

| title-alignment | center |

| title | On board peripherals |

...

| Page properties | ||||

|---|---|---|---|---|

| ||||

For example subsections see: <Series Name> TRM Template section examples#%3CSeriesName%3ETRMTemplatesectionexamples-On-boardPeripherals |

Configuration and System Control Signals

| Page properties | ||||

|---|---|---|---|---|

| ||||

|

...

| anchor | Table_OV_CNTRL |

|---|---|

| title-alignment | center |

| title | Controller signal. |

...

Signal Name

...

1) Direction:

- IN: Input from the point of view of this board.

- OUT: Output from the point of view of this board.

...

...

Enter the default value for power supply and startup of the module here.

- Order of power provided Voltages and Reset/Enable signals

Link to Schematics, for power images or more details

Power Rails

...

| hidden | true |

|---|---|

| id | Comments |

List of all power rails which are accessible by the customer

- Main Power Rails and Variable Bank Power

...

...

ED: TODO → Following needs to be updated to new TRM style.

Board to Board (B2B) I/Os

FPGA bank number and number of I/O signals connected to the B2B connector:

...

| anchor | Table_SIP_B2B |

|---|---|

| title | General SoC I/O to B2B connectors information |

...

...

1) Direction:

- IN: Input from the point of view of this board.

- OUT: Output from the point of view of this board.

Recommended Power up Sequencing

| Page properties | ||||

|---|---|---|---|---|

| ||||

List baseboard design hints for final baseboard development. |

...

| anchor | Table_BB_DH |

|---|---|

| title-alignment | center |

| title | Baseboard Design Hints |

...

...

...

...

JTAG Interface

JTAG access to the TEM0007 SoM through B2B connector JM2.

...

...

...

...

JTAG Signal

...

B2B Connector

...

JM2-99

...

Pulled Low: Microsemi Polarfire SoC

Pulled High: Lattice MachXO CPLD

UART Interface

The UART interface is connected from the Polarfire SoC to the B2B connector. If this interface is not necessary, these pins can be used for other functionality.

...

| anchor | Table_OBP_UART |

|---|---|

| title | UART interface description |

...

SDIO Interface

The SDIO interface is connected from the Polarfire SoC to the B2B connector. If this interface is not necessary, these pins can be used for other functionality.

...

...

...

...

...

...

...

...

SGMII Interface

The Polarfire Soc provides two SGMII interfaces whereby one interface is connected to the B2B connector.

...

| anchor | Table_OBP_SGMII |

|---|---|

| title | SGMII interface description |

...

...

MSSIO Interface

The MSSIO interface is connected from the Polarfire SoC to the B2B connector.

...

| anchor | Table_OBP_MSSIO |

|---|---|

| title | MSSIO interface description |

...

...

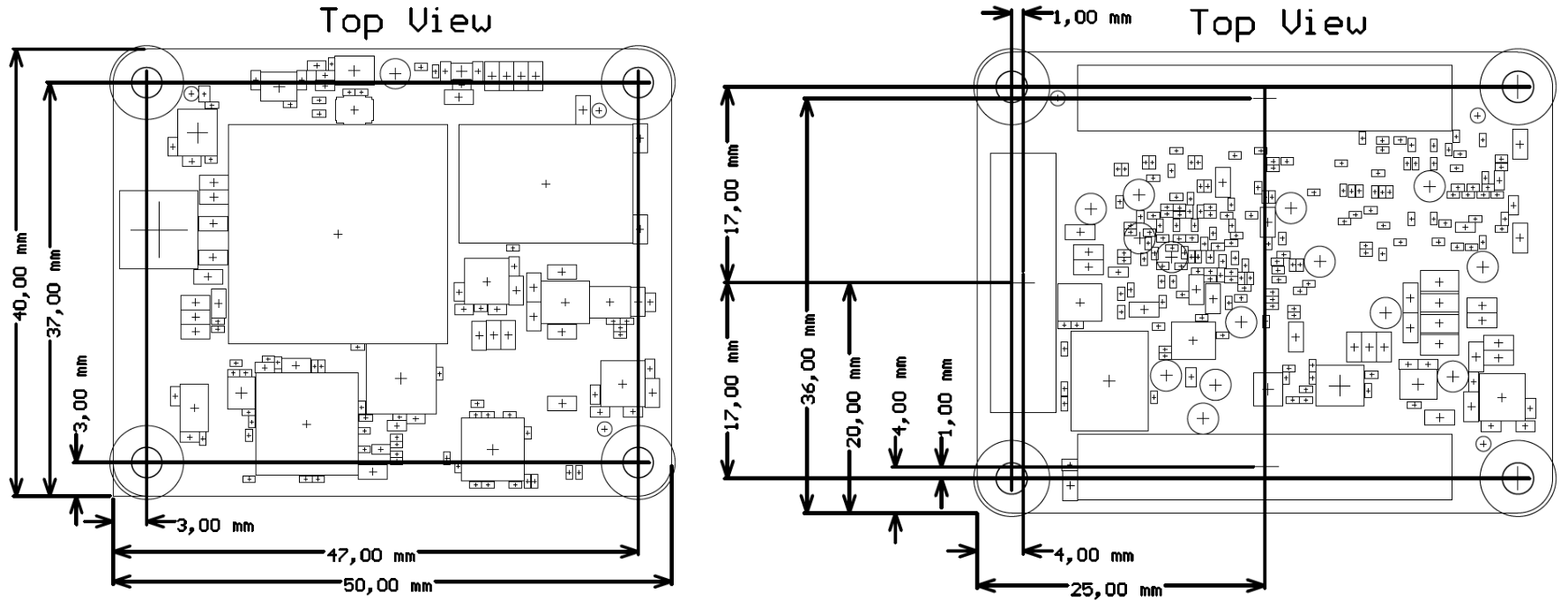

| anchor | Figure_TS_PD |

|---|---|

| title | Physical Dimension |

...

| Scroll Only | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||

Currently Offered Variants

...

MGT Lanes

There are four MGT (Multi Gigabit Transceiver) lanes and two clocks connected between the B2B connector JM3 and the Polarfire SoC bank 5. Each MGT lane consists of one transmit and one receive (TX/RX) differential pairs, four signals total per one MGT lane. Following table lists lane number, signal schematic name, and board-to-board pin connection:

...

| anchor | Table_SIP_MGT |

|---|---|

| title | MGT Lanes Connection |

...

Lane

...

Schematic

...

Gigabit Ethernet

On-board Gigabit Ethernet PHY (U7) is provided with Marvell Alaska 88E1512 IC. The Ethernet PHY SGMII interface is connected to the Polarfire SoC.

...

| anchor | Table_OBP_ETH |

|---|---|

| title | Gigabit Ethernet pin description |

...

System Controller CPLD I/O Pins

The System Controller CPLD (U1) is provided by Lattice Semiconductor LCMXO2-256HC (MachXO2 product family). It is the central system management unit with module specific firmware installed to monitor and control various signals of the FPGA, on-board peripherals, I/O interfaces and module as a whole.

...

| hidden | true |

|---|---|

| id | Comments |

you must fill the table below with group of MIOs which are connected to a specific components or peripherals, you do not have to specify pins in B2B, Just mention which B2B is connected to MIOs. The rest is clear in the Schematic.

Example:

...

SPI_CS , SPI_DQ0... SPI_DQ3

SPI_SCK

...

| anchor | Table_OBP_SC |

|---|---|

| title | System Controller CPLD special purpose pin description |

...

- 11

...

USB Interface

USB PHY is provided by Microchip USB3320. The ULPI interface is connected to the Polarfire SoC. I/O voltage is fixed at 3.3 V. Reference clock input for the USB PHY is supplied by the on-board 52.00 MHz oscillator (U12).

...

| anchor | Table_OBP_USB |

|---|---|

| title | General Overview of the USB PHY Signals |

...

DP - 18,

...

OTG-D_P

...

Test Points

...

| anchor | Table_OBP_TestPoints |

|---|---|

| title | Test Points Information |

...

On-board Peripherals

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes : In the on-board peripheral table "chip/Interface" must be linked to the corresponding chapter or subsection |

...

| anchor | Table_OBP |

|---|---|

| title | On board peripherals |

...

System Controller CPLD

The System Controller CPLD (U1) is provided by Lattice Semiconductor LCMXO2-256HC (MachXO2 product family). It is the central system management unit with module specific firmware installed to monitor and control various signals of the FPGA, on-board peripherals, I/O interfaces and module as a whole.

Gigabit Ethernet

On-board Gigabit Ethernet PHY (U7) is provided with Marvell Alaska 88E1512 IC (U7). The Ethernet PHY SGMII interface is connected to the Polarfire SoC. The reference clock input of the PHY is supplied from an on-board 25.00 MHz oscillator (U8).

...

| anchor | Table_OBP_ETH |

|---|---|

| title | Ethernet PHY to Polarfire SoC connections |

...

Bank 5 - N6

...

SGMII0_IN_P

...

U7 - 1

...

Bank 5 - L5

...

SGMII0_OUT_P

...

U7 - 4

...

USB PHY

Hi-speed USB ULPI PHY (U11) is provided with USB3320 from Microchip. The ULPI interface is connected to the Polarfire SoC via MSSIO14...25 bank 2. The I/O voltage is fixed at 3.3 V and PHY reference clock input is supplied from the on-board 52.00 MHz oscillator (U12).

...

| anchor | Table_OBP_USB |

|---|---|

| title | USB PHY to Polarfire SoC connections |

...

U2 - G4

...

OTG-STP

...

U11 - 29

...

U2 - F1

...

OTG-DIR

...

U11 - 31

...

OTG_DATA0

...

LPDDR4 SDRAM

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes : Minimum and Maximum density of DDR3 SDRAM must be mentioned for other assembly options. (pay attention to supported address length for DDR3) |

The TEM0007 SoM has a one GByte volatile LPDDR4 SDRAM IC for storing user application code and data.

- Part number: IS43LQ32256A-062BLI

- Supply voltage: +1.8 V / +1.1 V

- Speed: 1600 MHz

- Temperature: Industrial (-40°C to +85°C)

EEPROM

There is a 2 Kbit EEPROM provided on the module TEM0007 with a pre-programmed globally unique MAC.

...

| anchor | Table_OBP_EEP |

|---|---|

| title | I2C EEPROM interface MSSIOs and pins |

...

| anchor | Table_OBP_I2C_EEPROM |

|---|---|

| title | I2C address for EEPROM |

...

SPI Flash Memory

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes : Minimum and Maximum density of quad SPI flash must be mentioned for other assembly options. |

The TEM0007 is equipped with a MT25QU512ABB8E12-0SIT flash memory chip, U3, which provided storage for FPGA configuration files. After configuration, the remaining free memory can be used for application data storage.

...

| anchor | Table_OBP_SPI |

|---|---|

| title | SPI Flash interface pins |

...

Oscillators

...

| anchor | Table_OBP_CLK |

|---|---|

| title | Osillators |

...

Power and Power-On Sequence

...

| hidden | true |

|---|---|

| id | Comments |

In 'Power and Power-on Sequence' section there are three important digrams which must be drawn:

- Power on-sequence

- Power distribution

- Voltage monitoring circuit

| Note |

|---|

For more information regarding how to draw diagram, Please refer to "Diagram Drawing Guidline" . |

Power Supply

Power supply with minimum current capability of 3 A for system startup is recommended.

Power Consumption

...

| anchor | Table_PWR_PC |

|---|---|

| title | Power Consumption |

...

* TBD - To Be Determined

Power Distribution Dependencies

...

| anchor | Figure_PWR_PD |

|---|---|

| title | Power Distribution |

...

| Scroll Only |

|---|

Power-On Sequence

The power sequence is the recommended one. The final sequence depends on the system controller.

...

| anchor | Figure_PWR_PS |

|---|---|

| title | Power Sequency |

...

| Scroll Only |

|---|

Voltage Monitor Circuit

The TEM0007 delivers two voltage monitor circuits. The first circuit is responsible for the selection of voltage "VDDAUX1". This voltage is selected on the basis of the voltage of "VCCIOB". If "VCCIOB" is higher than 2.9 V, "VDDAUX1" should be +3.3 V. If it is smaller, "VDDAX1" should be +2.5 V. The second circuit monitors the +1.0 V power rail. According to this rail, the reset is set/unset to realize a brown-out detection. Furthermore, a possibility for a manual reset is available.

...

| anchor | Figure_PWR_VMC |

|---|---|

| title | Voltage Monitor Circuit |

...

| Scroll Only |

|---|

Power Rails

...

| anchor | Table_PWR_PR |

|---|---|

| title | Module power rails. |

...

B2B Connector

JM1 Pin

...

B2B Connector

JM2 Pin

...

VCCIOB

...

Bank Voltages

...

| anchor | Table_PWR_BV |

|---|---|

| title | Polarfire SoC bank voltages. |

...

Bank

...

Voltage

...

VCCIOB

...

| hidden | true |

|---|---|

| id | Comments |

...

use "include page" macro and link to the general B2B connector page of the module series,

...

Technical Specifications

Absolute Maximum Ratings

...

| anchor | Table_TS_AMR |

|---|---|

| title | Absolute maximum ratings |

...

VCCIOB

...

Recommended Operating Conditions

Operating temperature range depends also on customer design and cooling solution. Please contact us for options.

...

| anchor | Table_TS_ROC |

|---|---|

| title | Recommended operating conditions. |

...

VCCIOB

...

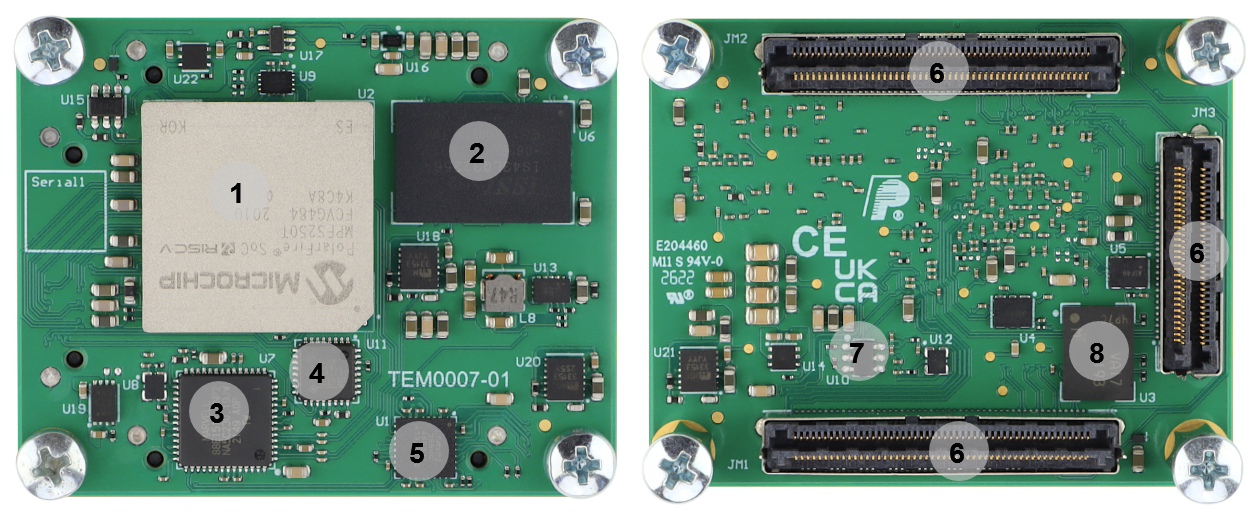

Physical Dimensions

Module size: 40 mm × 50 mm. Please download the assembly diagram for exact numbers.

Mating height with standard connectors: 8 mm.

PCB thickness: 1.74 mm.

...

| hidden | true |

|---|---|

| id | Comments |

In 'Physical Dimension' section, top and bottom view of module must be inserted, information regarding physical dimensions can be obtained through webpage for product in Shop.Trenz, (Download> Documents> Assembly part) for every SoM.

For Example: for Module TE0728, Physical Dimension information can be captured by snipping tools from the link below:

| Note |

|---|

For more information regarding how to draw diagram, Please refer to "Diagram Drawing Guidline" . |

...

...

Example for TE0728:

ENG Page: https://shop.trenz-electronic.de/en/Products/Trenz-Electronic/TE07XX-Zynq-SoC/TE0728-Zynq-SoC/

...

For Baseboards or modules, where no overview page is available (and revision number is coded in the direct link) use shop search link, e.g. TE0706:

ENG Page: https://shop.trenz-electronic.de/en/search?sSearch=TE0706

...

...

...

...

...

Revision History

Hardware Revision History

...

| hidden | true |

|---|---|

| id | Comments |

Set correct links to download arrier, e.g. TE0706 REV02:

TE0706-02 -> https://shop.trenz-electronic.de/Download/?path=Trenz_Electronic/Modules_and_Module_Carriers/4x5/4x5_Carriers/TE0706/REV02/Documents

Note:

...

...

...

| anchor | Figure_RV_HRN |

|---|---|

| title | Board hardware revision number. |

...