TEM0703 with TEM0007Modification to use TEM0007 with Standard 4x5 TE0703 carrier. Carrier without modifications will be TEB2000 in the future

TEM0007 module is a Microchip Polarfire SoC module.

For more information about this module refer to TEM0007 TRM

Serial NOR Flash, U3| Scroll Title |

|---|

| title-alignment | center |

|---|

| title | TEM0007 ModuleHardware overview |

|---|

|

| draw.io Diagram |

|---|

| border | true |

|---|

| |

|---|

| diagramName | TEM0007_Hardware_ModuleOverview |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | top |

|---|

| lbox | true |

|---|

| diagramWidth | 9941280 |

|---|

| revision | 2 |

|---|

|

|

Microchip Polarfire SoC MPFS250T, U21 GByte LPDDR4 SDRAM, U6Integrated 10/100/1000 Mbps Energy Efficient Ethernet Transceiver, U7Highly Integrated Full Featured Hi-Speed USB 2.0 ULPI Transceiver, U11Lattice Semiconductor MachXO2 System Controller CPLD, U1B2B Connector Samtec Razor Beam, JM1...3EEPROM, U10| Hardware | Quantity | Note |

|---|

| TEM0007 | 1 | Microchip Polarfire SoC Module |

| TEM0703Modified TE0703 | 1 | Carrier board Modified TE0703: - FTDI Firmware

- Added second uart (uart0)

- Additional Reset push button

|

| TE0790 | 1 | Universal USB2.0 to JTAG/UART |

| Mini USB Cable | 2 |

|

| RJ45 Ethernet Cable | 1 |

|

| USB Stick | 1 |

|

| Heatsink | 1 | Optional | Heatsink | 1 |

|

It is necessary to modify the TE0703 carrier board for using TEM0007 module. In the following will be in detail discussed the modification of TE0703 carrier board.

| Expand |

|---|

|

| draw.io Diagram |

|---|

| border | true |

|---|

| diagramName | TE0703_MOdification_For_TEM0007 |

|---|

| simpleViewer | false |

|---|

| links | auto |

|---|

| tbstyle | top |

|---|

| lbox | true |

|---|

| diagramWidth | 1044 |

|---|

| revision | 3 |

|---|

|

|

Jumper J11 must be set to 3.3V.

| Scroll Title |

|---|

| title-alignment | center |

|---|

| title | Set SD card voltage |

|---|

|

Image Added Image Added

|

It is recommended to use second UARD interface to see the HSS console. The UART pins mus be connected to XMOD module ( TE0790 ). The TE0790 is a universal USB2.0 to JTAG/UART converter.For more infomation about this module refer to TE0790 TRM

For this purpose see the following table:| TE0703 Pin | Schematic label | TE0790 Pin | Schematic label | Description |

|---|

J2A-Pin A31 (TXD) | X17 | J2-Pin 3 (RXD) | A |

|

J2A-Pin A30 (RXD) | X16 | J2-Pin 5 (TXD) | B | This connection does not need to be connected if no data has to be entered in HSS console. |

| J2A-Pin A32 (GND) | --- | J2-Pin 1 | --- |

|

Dip switch of TE0790 module must be set according to the following table:

| TE0790 (XMOD) | S2-1 | S2-2 | S2-3 | S2-4 |

|---|

| S2 Dip Switch Status | ON | OFF | ON | ON |

|---|

Driver of FTDI chip must be reprogrammed. It must be mached with microchip FPGAs.

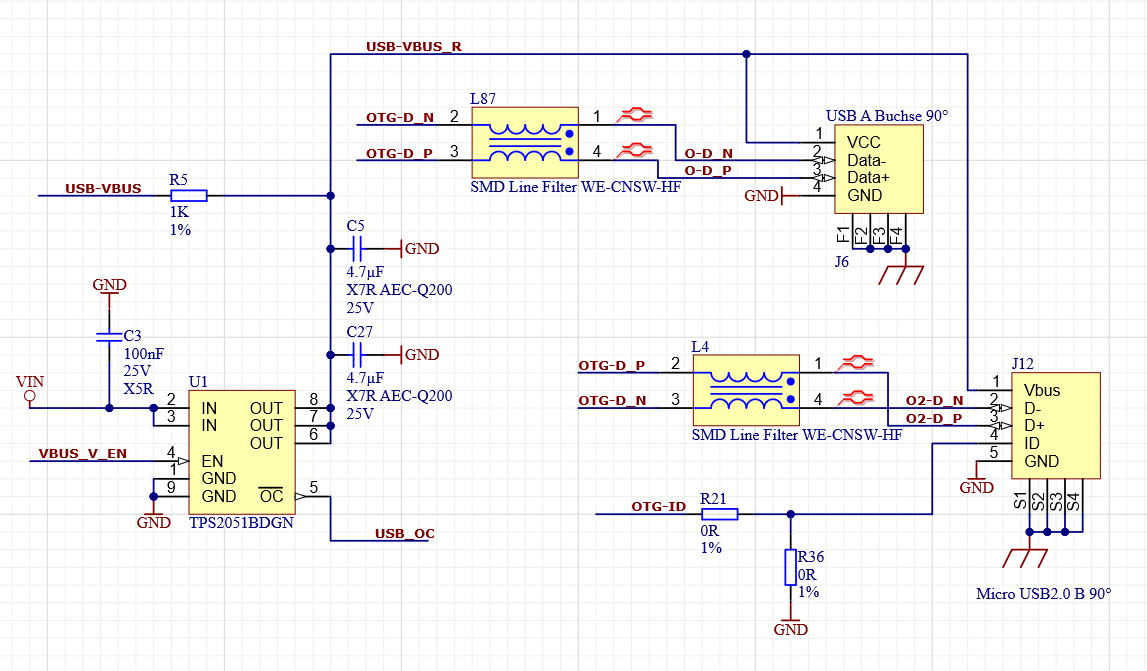

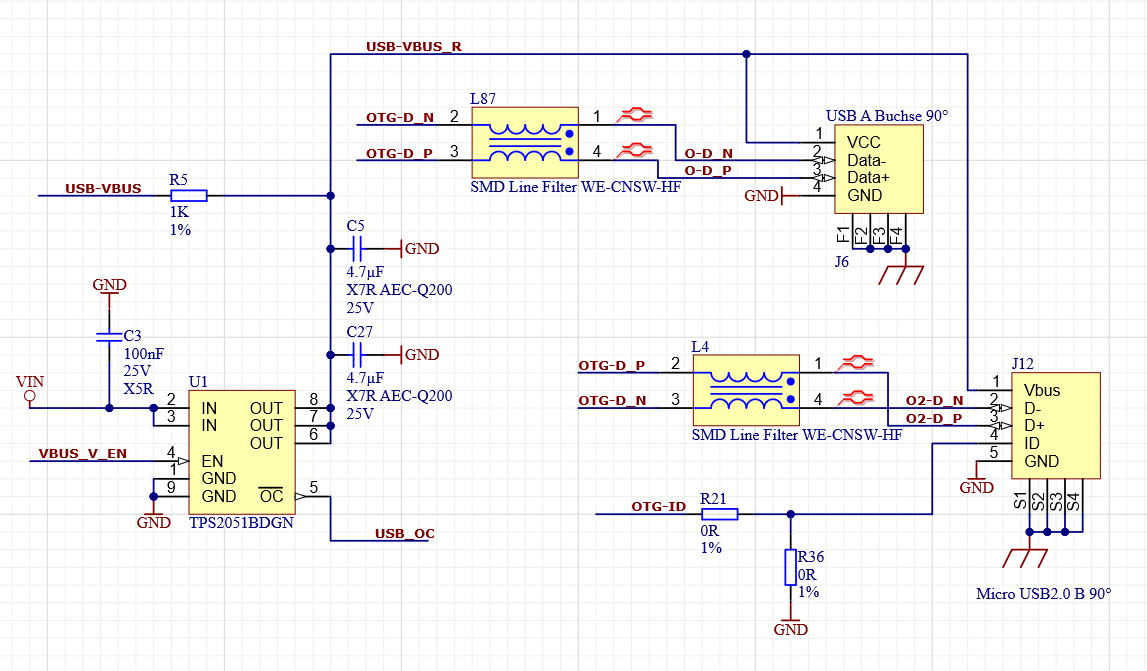

The following components of the TE0703 must be changed , if these don't exist on the board or other component is soldered :

| Component | Artikel Nummer | Value | Designator (Desoldering) | Designator (Soldering) | Description |

|---|

USB connector | 27235 | --- | J6 | J12 | Micro USB2 B 90° |

| Choke | 24514 | --- | L87 | L4 | SMD Line Filter WE-CNSW-HF |

| Resistor | 22752 | 1k 1% | R5 | R5 |

|

| Capacitor | 26238 | 4.7uf 25V | C5 | C5 | X7R AEC-Q200 |

| Capacitor | 26238 | 4.7uf 25V | C27 | C27 | X7R AEC-Q200 |

| Scroll Title |

|---|

| title-alignment | center |

|---|

| title | USB schematic |

|---|

|

Image Added Image Added

|

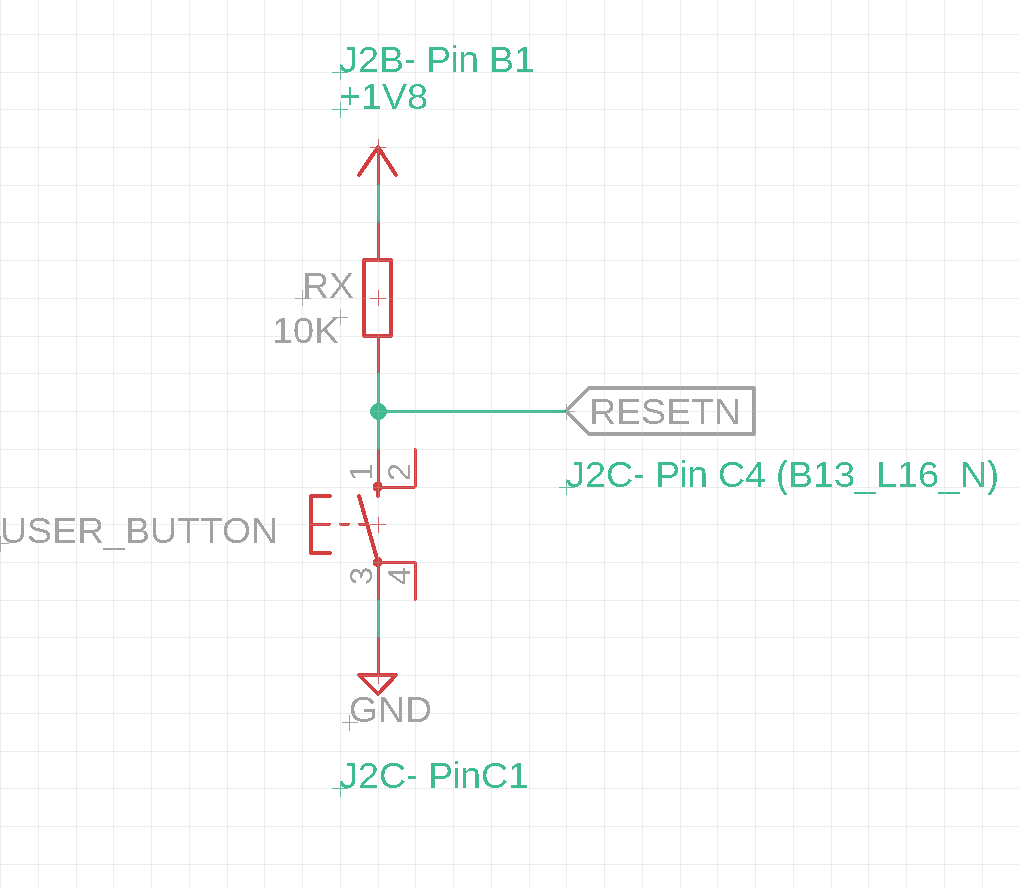

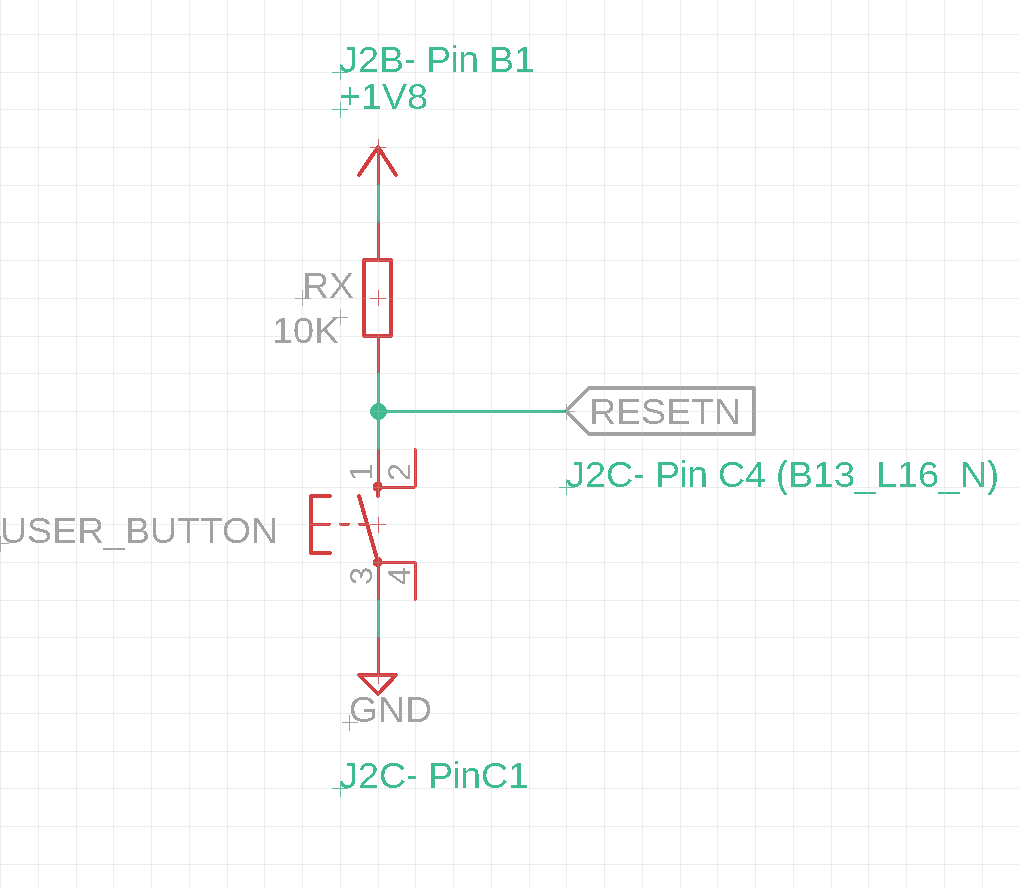

It is installed a power reset button. But it is recommended to have a soft reset button optional. The recommended schematic consists of a push button with a pulled up resistor as shown:

| Scroll Title |

|---|

| title-alignment | center |

|---|

| title | Reset Schematic |

|---|

|

Image Added Image Added

|

| Scroll Title |

|---|

| title-alignment | center |

|---|

| title | Hardware overviewAssembled Reset push button |

|---|

|

| draw.io Diagram |

|---|

| border | true |

|---|

| diagramName | TEM0007Assembled_Reset_HardwarePush_OverviewButton |

|---|

| simpleViewer | false |

|---|

| width | links | auto |

|---|

| tbstyle | top |

|---|

| lbox | true |

|---|

| diagramWidth | 743 | revision | 2761 |

|---|

| revision | 3 |

|---|

|

|

| Pin | TE0703 Schematic label | Description |

|---|

| 3.3V | J2B- Pin B1 | VG96 female header vertical |

| GND | J2C-Pin C1 | VG96 female header vertical |

| RESETN | J2C-Pin C4 | VG96 female header vertical |

| Supply voltage | Current | Designator | Description |

|---|

| 5V | 2A* | J13 on the carrier board |

|

*Current is dependent on design and the used heatsink. This value is recommend value.

SwitchesIn this case S2 dip switches switch of the carrier board TE0703 can be use used for JTAG adjustment setting only and it will not be used to select boot mode, because TEM0007 supports only SD card boot mode.

| S2-1 | S2-2 | S2-3 | S2-4 | Description |

|---|

| CM1 | CM0 | JTAGEN | MIO0 |

|

| S2-2 | S2-3 | CM0 | JTAGEN | Description |

|---|

| OFF | OFF | 1 | 1 | Access to TE0703 CPLD |

| OFF | ON | 1 | 0 | Access to CPLD of B2B ModuleTEM0007 |

| ON | OFF | 0 | 1 | Access to TE0703 CPLD |

| ON | ON | 0 | 0 | Access to FPGA of B2B Module |

| Jumper | related net | Allowed to set on | Description |

|---|

| J7 | VBAT | --- | Unnecessary |

| J11 | VCCA pin of voltage level shifter chip ( TXS02612RTWR ) | 3.3V | If this jumper set to 1.8V , SD card will not work. |

J5 | VCCIOA | --- | Unnecessary |

J8 | VCCIOB | 1.8V / 3.3V | This jumper can be set to 1.8V or 3.3V. |

J9 | VCCIOC | --- | Unnecessary |

| J10 | VCCIOD | Only 1.8V | Set to 1.8V |

There are one reset push button on the board. Second reset button can be added on the board as optional reset.

| Signal | Push button | FPGA Pin | Schematic label | New design label | Connected to | Access on the carrier board via | Description |

|---|

| RESET (RESIN) | S1 | H7 | DEVRST_N | --- | TPS3106K33DBV chip RSTVDD Pin / CPLD of TEM0007 via B2B connector (SC_RESET / MR_n) | S1 | This bush button is soldered already on the carrier board. This reset signal does not exist in Libero design. This reset signal resets FPGA via CPLD Firmware of TEM0007 module. By pushing S1 (RESIN) push button will set DEVRST_N to low. |

| RESETN | User button | H13 | B1_GPIO185_N | RESETN | JM2-Pin 73 | JB2-pin 74 / J2C-C4 | User button does not exist on the carrier board. User button should be soldered by the user himself. (Optional) This button should be pulled up via a 10k resistor. |

This module supports only supports SD card boot mode. Therefore there There is no dip switch to select boot mode. The selection between SD card or other boot mode . But there is a jumper on the TEM0703 carrier board to select SD card voltage correctly. For this purpose set jumper J11 of the carrier board for 3.3V voltage.

| Scroll Title |

|---|

| title-alignment | center |

|---|

| title | Set SD card voltage |

|---|

|

Image Removed Image Removed

|

JTAG signals

will be done in HSS. TEM0007 module supports SD card boot mode and JTAG boot mode.

This boot mode does not exist in the reference design. In the future this boot mode can be used in the reference design.

TEM0007 does not support eMMC boot mode.

FTDI chip is used in the TEM0007 module for conversion USB to UART/JTAG interfaces. This chip needs driver to put this chip in operation. User does not need additional programmer more.

| USB Connector | Designator | Connected to | Description |

|---|

| USB2.0 mini usb | J12 | FT2232H FTDI Chip | This interface is used to access to UART1 or JTAG interface. |

| USB2.0 mini usb | J6 | USB3320C-EZK USB PHY Chip on the TEM0007 module | It is used to connect external USB device same as USB Stick. |

| Signal | FPGA Pin | Schematic label | New design label | Connected to | Access on the carrier board via | Description |

|---|

| MAC_0_MDIO | J3 | ETH_MDIO | MAC_0_MDIO | Ethernet Phy Chip (Marvell 88E1512-A0-NNP2I000) Pin 8 | No Access | MAC_0_MDO | H6 | ETH_MDO | MAC_0_MDO | Ethernet Phy Chip (Marvell 88E1512-A0-NNP2I000) Pin 7 | No Access |

There is two UART interfaces.

| UART | Design label | FPGA Pin | Schematic | labelNew design label | Connected to | Access on the carrier board via | Interface for | Baud rate | Description |

|---|

| UART0 | MMUART_0_TXD | C2 (TXD) | UART_CON_TXMMUART_0_TXD | JM1-Pin 99 | JB1-Pin 100 / J2A-Pin 31 (TXD) | HSS (Hardware System Service) | 115200 | There is no connector on the TEM0703 TE0703 carrier board PCB REV06. In this case user should connect these pins to USB to JTAG/UART converter same as TE0790. (Crosstalk)

|

| MMUART_0_RXD | D3 (RXD) | UART_CON_RXMMUART_0_RXD | JM1-Pin 97 | JB1-Pin 98 / J2A-Pin 30 (RXD) |

| UART1 | MMUART_1_TXD | H5 (TXD) | UART_TXMMUART_1_TXD | JM1-Pin 85 | JB1-Pin 86 /

J4 Mini USB connector | Linux console / Bare metal interface | 115200 |

|

| MMUART_1_RXD | H2 (RXD) | UART_RXMMUART_1_RXD | JM1-Pin 92 | JB1-Pin 91 /

J4 Mini USB connector |

| UART2 | MMUART_2_TXD_M2F | B22 (TXD) | B1_GPIO22_N | JM2-Pin 36 | JB2-Pin 35 | Optional for customer | ---- | This UART interface is an optional UART interface for customer. It is necessary to provide other required features same as design in linux to put this interface in application. |

| MMUART_2_RXD_F2M | C22 (RXD) | B1_GPIO23_P | JM2-Pin 44 | JB2-Pin 43 |

| UART3 | MMUART_3_TXD_M2F | D21 (TXD) | B1_GPIO22_P | JM2-Pin 52 | JB2-Pin 51 | Optional for customer | ---- | This UART interface is an optional UART interface for customer. It is necessary to provide other required features same as design in linux to put this interface in application. |

| MMUART_3_RXD_F2M | B21 (RXD) | B1_GPIO21_P | JM2-Pin 38 | JB2-Pin 37 |

| COREUARTapb | COREUART_TX | A7 (TXD) | B1_GPIO173_P | COREUARTapb | A7 (TXD) | B1_GPIO173_P | COREUART_TX | JM1-Pin 65 | JB1-Pin 66 | Additional UART interface | Depends on system clock frequency.

Baud_rate = clk/(Baudval+1)*16 and Baudval = (clk/(1+Baudrate)) - 1 | This UART interface works via COREUARTapb in Libero. This UART interface is an optional UART interface for customer. It is necessary to provide other required features same as design in linux to put this interface in application. |

| COREUART_RX | H15 (RXD) | B1_GPIO7_N | COREUART_RX | JM2-Pin 66 | JB2-Pin 65 |

| UART4mBUS | USER_UART4_ | UARTTX | B20 (TXD) | B1_GPIO19_PUSER_UART_TX | JM2-Pin 46 | JB2-Pin 45 | Additional UART interface | 115200 | Old names mBUS_UART_TX, mBUS_UART_RX and mBUS_INT---- | This UART interface is an optional UART interface for customer. It is necessary to provide other required features same as design in linux to put this interface in application. |

| USER_UART4_RX | A21 (RXD) | B1_GPIO20_NUSER_UART_RX | JM2-Pin 32 | JB2-Pin 31 |

| USER_UART4_INT | A20 (INT) | B1_GPIO20_PUSER_UART_INT | JM2-Pin 34 | JB2-Pin 33 |

| I2C | FPGA Pin | Schematic label | New design label | Connected to | Access on the carrier board via | Description |

|---|

| I2C0 | A3 (SCL) | I2C_CON_SCL | I2C_0_SCL | JM1-Pin 95 | JB1-Pin 96 (SCL) | In the reference design is connected no device on the module or carrier. Therefore in linux cosole exists this interface but by typing i2cdetect command no device will be find. |

| E3 (SDA) | I2C_CON_SDA | I2C_0_SDA | JM1-Pin 93 | JB1-Pin 94 (SDA) |

| I2C1 | C1 (SCL) | I2C_SCL | I2C_1_SCL | EEPROM chip U10 SCL pin | No Access | In the reference design is used this i2c to access EEPROM on the TEM0007 module. ( Address 0x50) |

| B1 (SDA) | I2C_SDA | I2C_1_SDA | EEPROM chip U10 SDA pin | No Access |

| COREUSER_I2CI2C0 | B8 (SCL) | B1_GPIO175_N | USER_I2C0_SCL | JM1-Pin 62 | JB1-Pin 61 | This additional i2c interface in generated via COREI2C. (Old names CORE_I2C_C0_INT , COREI2C_C0_SCL and COREI2C_C0_SDA)This I2C interface is an optional i2c interface for customer. It is necessary to provide other required features same as design in linux to put this interface in application. |

| A8 (SDA) | B1_GPIO175_P | USER_I2C0_SDA | JM1-Pin 60 | JB1-Pin 59 |

| RPIUSER_I2CI2C1 | F10 (SCL) | B1_GPIO180_N | USER_I2C1_SCL | JM2-Pin 85 | JB2-Pin 86 | This additional i2c interface in generated via COREI2C. (Old names RPi_ID_I2C_IRQ, RPi_ID_SC and RPi_ID_SD)This I2C interface is an optional i2c interface for customer. It is necessary to provide other required features same as design in linux to put this interface in application. |

| B9 (SDA) | B1_GPIO179_N | USER_I2C1_SDA | JM1-Pin 68 | JB1-Pin 67 |

GPIO| Signal | FPGA Pin | Schematic label | New design label | Connected to | Access on the carrier board via | Description |

|---|

GPIO116E5RSTETHPHYRESETETH_RST | No Access | Phy chip reset pin | MDIO | Ethernet Phy Chip (Marvell 88E1512-A0-NNP2I000) Pin 8 | No Access |

|

| MAC_0_MDO | H6 | ETH_MDO | MAC_0_MDO | Ethernet Phy Chip (Marvell 88E1512-A0-NNP2I000) Pin 7 | No Access |

|

| GPIO | FPGA Pin | Schematic label | Connected to | Access on the carrier board via | Description |

|---|

| GPIO_1_16 ( ETH_PHY_RESET ) | E5 | ETH_RST | Marvell 88E1512-A0-NNP2I000 ethernet phy chip reset pin ( Pin 16 RESETn) |

. Necessary for reset pin of ethernet phy chip| GPIO_1_17 | E4 | OTG-RST | USB_PHY_RESET | OTG-RST | No Access | USB phy chip reset pin (Microchip USB3320-EZK). Necessary for reset pin of usb phy chip |

GPIO_1_18 | B2 | --- | Not used | ---19| 17 ( USB_PHY_RESET ) | E4 | OTG-RST | Microchip USB3320C-EZK USB phy chip reset pin (Pin 27 RESETB) |

A2 | --- | Not used | --- | No Access |

|

| GPIO_1_20 | B3 | GPIO1 |

GPIO_1_20 | B2B JM1-Pin 91 | B2B JB1-Pin 92 |

|

| GPIO_1_23 | D4 | GPIO0 |

GPIO_1_23 | B2B JM1-Pin 87 | B2B JB1-Pin 88 |

GPIO_2_0 | U12 | B0_HSIO94_P | Not used | ---No Access | _1T13 | B0_HSIO95_N | Not used | --- | No Access | GPIO_6R12 | B0_HSIO95_P | Not used | --- | No AccessRPi_GPIO12 | GPIO_2_2RPiGPIO13GPIO_2_3RPiGPIO16GPIO_2_4RPiGPIO17GPIO_2_5RPiGPIO19GPIO_2_7RPiGPIO20GPIO_2_8RPiGPIO21GPIO_2_9RPiGPIO22GPIO_2_10RPiGPIO23GPIO_2_11RPiGPIO24GPIO_2_12RPiGPIO25GPIO_2_13RPiGPIO26GPIO_2_14RPiGPIO27GPIO_2_15

| Input | FPGA Pin | Schematic label | New design label | Connected to | Access on the carrier board via | Description |

|---|

| SW1USER_IN0 | V19 | B0_HSIO72_N | USER_IN0 | JM3-Pin 42 | JB3-Pin 41 | SW2 | U18 | B0_HSIO74_N | --- | --- | No Access | SW3 | W19 | B0_HSIO79_P | --- | --- | No Access | SW4 | H13 | B1_GPIO185_N | RESETN | JM2-Pin 73 | JB2-Pin 74 | Used as RESETN Pin |

|

| Output | FPGA Pin | Schematic label | New design label | Connected to | Access on the carrier board via | Description |

|---|

| LED0 | V14 | B0_HSIO90_P | --- | --- | No Access | LED1 | U13 | B0_HSIO93_N | --- | --- | No Access | LED2 | T12 | B0_HSIO94_N | --- | --- | No Access | LED3USER_OUT0 | AB19 | B0_HSIO70_P | USER_OUT0 | JM3-Pin 60 | JB3-Pin 59 |

|

| Signal | FPGA Pin | Schematic label | New design label | Connected to | Access on the carrier board via | Description |

|---|

| PWM | E11 | B1_GPIO183_N | USER_PWM0 | JM1-Pin 82 | JB1-Pin 81 / J1C-Pin C4 | This PWM generator is an optional feature for customer. It is necessary to provide other required features same as design in linux to put PWM generator in application. |

Unfortunately on the TEM0007 module exists no LED. But the LEDs on the TE0703 can be used for various purposes. For the no edited CPLD Firmware code of TE0703 the LEDs have the following functions as shown in this table:

| LED | Prio. 0: Power | Prio. 1: Module CPLD access* | Prio. 2 | Description |

|---|

| LED1 (D1-red) | Blink, if Power Good is low | ON | FTDI UART RX |

|

| LED2 (D2-green) | Blink, if Power Good is low | ON | FTDI UART TX |

|

| LED3 (D3-red) | OFF | ON | User defined with B2B Pin JB2-99 |

|

| LED4 (D4-green) | OFF | ON | User defined with B2B Pin JB2-90 |

|

| PHY LEDs (green/orange) | Blink orange, if Power Good is low | Blink Green and orange | ----- |

|

*Attention: LED1,2,3,4 are on, if S2-2 is set to OFF. If S2-3 is OFF, TE0703 is in chain!