Versions Compared

Key

- This line was added.

- This line was removed.

- Formatting was changed.

| Page properties | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

Design Name always "TE Series Name" + Design name, for example "TEI0006 TEM0007 Test Board"

|

| Custom_table_size_100 |

|---|

|

| Custom_table_size_100 |

|---|

| Page properties | ||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||

| Page properties | ||||||||||||||||||||||||||||||||||||||||

| ||||||||||||||||||||||||||||||||||||||||

Important General Note:

|

Overview

| Scroll Ignore | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

Refer to http://trenz.org/tem0007-info for the current online version of this manual and other available documentation.

Key Features

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

| Excerpt |

|---|

|

Revision History

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

| Scroll Title | |||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||

|

|

Release Notes and Know Issues

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

| ||||

| Page properties | ||||

| ||||

Notes :

|

| Scroll Title | ||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||

|

Requirements

Software

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

| Scroll Title | ||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||

|

Additional software requirement

| Scroll Title | |||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||

|

Hardware

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

Complete List is available on <project folder>/board_files/*_board_files.csv

Design supports following modules:

| Scroll Title | |||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||||||||||||||

*used as reference |

Design supports following carriers:

| anchor | Table_HWC |

|---|---|

| title-alignment | center |

| title | Hardware Carrier |

*used as reference |

The Design requires one of the following carriers

*used as reference

Additional HW Requirements:

| Scroll Title | |||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||

*used as reference |

Additional hardware requirements:

| Scroll Title | |||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||||||||

*used as reference |

Content

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

For general structure further insight into the structure of a Trenz Reference Design Download and usage of the reference design, see its content in general , please follow the link Project Delivery - Microchip devices

Design Sources

| Scroll Title | |||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||

|

Prebuilt

|

Prebuilt

| Page properties | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Page properties | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Notes :

|

| Scroll Title | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Download

Reference Design is only usable with the specified Libero version. Do never use different versions of Libero software for the same project.

| Page properties | ||||

|---|---|---|---|---|

| ||||

|

Reference design is available on:

Design Flow

| Scroll Ignore | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

Trenz Electronic provides a TCL project generation based on Microchip's Design Flow where possible.

See also:

Libero SoC

| Note |

|---|

Reference Design is |

| Note |

Reference Design is available with and without prebuilt files. It's recommended to use TE prebuilt files for first launch. |

Trenz Electronic provides a tcl based built environment based on Libero Design Flow.

See also:

The most Trenz Electronic FPGA Reference Designs are TCL-script based projects.

The "normal" Libero project will be generated in the subfolder "/Libero/" and the additional software part will be generated in the subfolder "/software/" after executing scripts.

To create project do the following steps:

ExecuteThe Libero SoC Hardware Design Project for this board is delivered as a TCL script which utilizes the Libero SoC Command API .

The script Libero SoC Project will be generated into the folder "<project folder> / libero_<Variant short name>".

- Run the script "Generate_TEM0007_Hardware-Design_in_Libero_SoC_v2023.1.cmd"

- Press 0 , if the path of installed libero software is : C:/Microchip/Libero_SoC_v2023.1/Designer/bin/libero.exe

- Press 1, if it will be entered the path Microchip or Libero SoC installations folder. The script selects automatically the Libero exe.

- Press 2, if it will be entered the full path to the Libero SoC exe.

- Press 3 to exit the script.

- Option 0 : VHDL

- Option 1 : VERILOG

- Option 2 : To exit th script

| Scroll Title | ||||

|---|---|---|---|---|

| ||||

|

| Expand | ||

|---|---|---|

| ||

|

| Expand | ||

|---|---|---|

| ||

|

| Expand | ||

|---|---|---|

| ||

|

| Expand | ||

|---|---|---|

| ||

|

| Expand | ||

|---|---|---|

| ||

|

Launch

Hardware Setup

see Modified TE0703 for Microchip Getting Started

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

Programming

| Note |

|---|

Check Module and Carrier TRMs for proper HW configuration before you try any design. |

Programming eNVM

The eNVM is a user non-volatile flash memory that can be programmed independently. There is two methods to program eNVM:

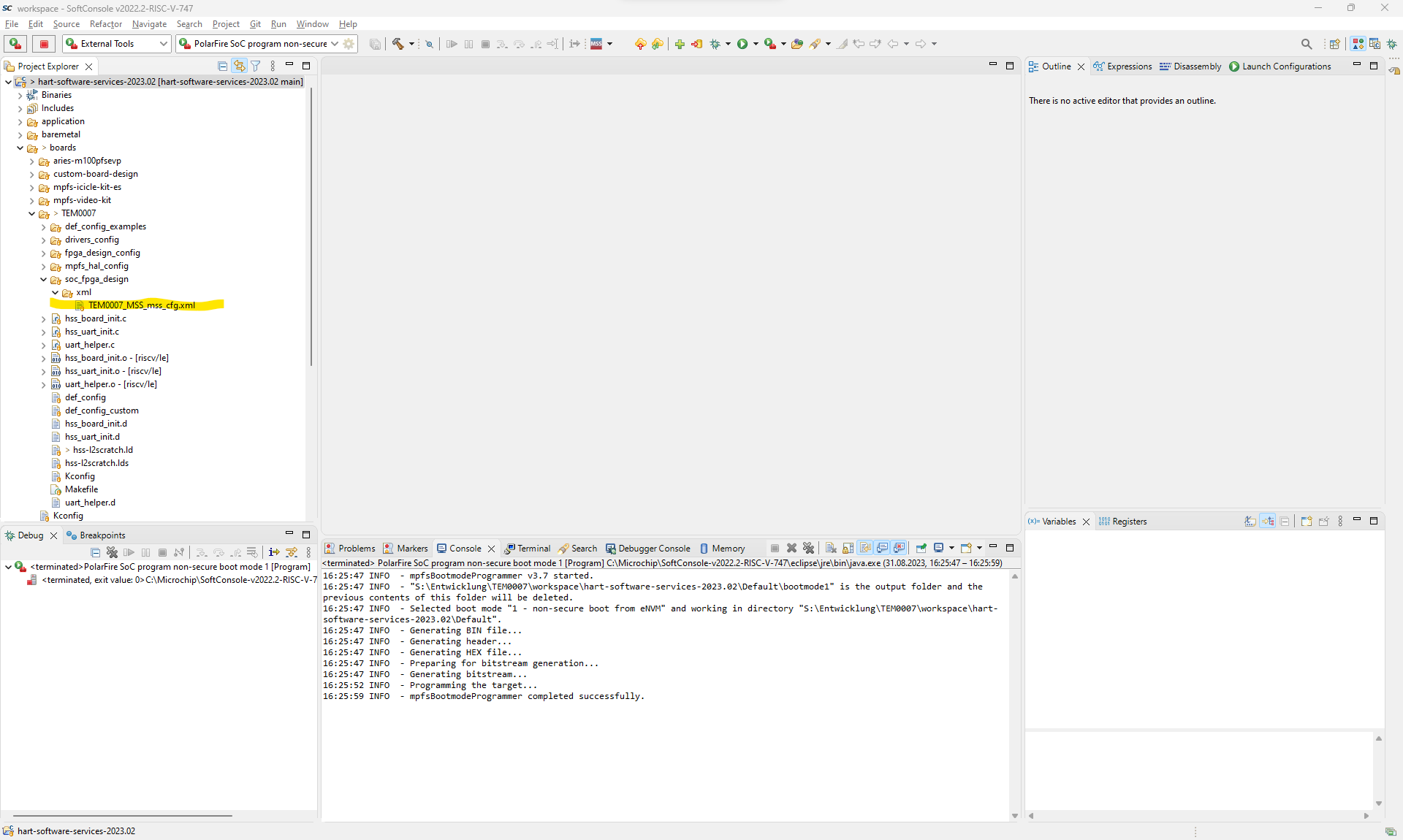

Programming eNVM in SoftConsole

To program HSS *.elf file on FPGA:

- Prepare the hardware see Hardware Setup

- Open SoftConsole software as administrator, if it is not done yet.

- Select correct directory as workspace directory.

- Build the hart-software-services-master , if it is not done yet.

- Click on Run > External Tools > Polarfire SoC program non-secure boot-mode 1

Programming eNVM in Flashpro Express

The HSS generated hex file can be attached to bitstream file. For more information see Design Flow

To program the eNVM in Flashpro Express see #Using FlashPro Express

Programming Bitstream

There is two ways to program bitstream file on FPGA:

Using Libero SoC

- Connect the TEM0703 board via its Mini-USB connector. (J4)

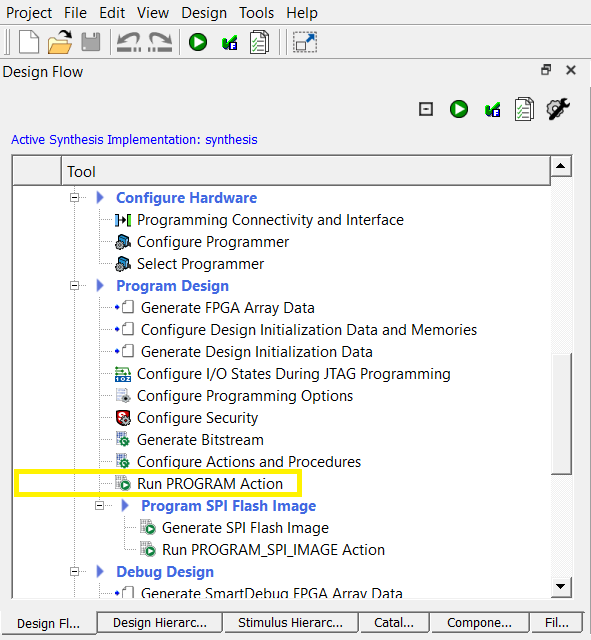

- After generating bitstream in Libero click on Run PROGRAM Action to program bitstream file on FPGA.

Expand title Programming FPGA using Libero SoC  Image Removed

Image Removed

Using FPExpress software

| Expand | ||

|---|---|---|

| ||

|

| title | Open FPExpress software |

|---|

Image Removed

Image Removed

Get prebuilt boot binaries

| Note |

|---|

Reference Design is also available with prebuilt files. It's recommended to use TE prebuilt files for first launch. |

Run create_project_win.cmd/create_project_linux.shSelect Module in 'Board selection'Click on 'Export prebuilt files' buttonFolder <project folder>/_binaries_<Article Name> with subfolder boot_linux will be generated and opened

SD-Boot mode

This module supports SD card boot mode. There is no dip switch to select boot mode. The selection between SD card or other boot mode will be done in HSS. TEM0007 module supports SD card boot mode and JTAG boot mode.

Prepare SD card as follows for SD card boot mode:

- Extract SD_Card.zip file

- Now there is a image file (SD_Card.img)

- Alternative SD card can be written via Win32DiskImager or balenaEtcher softwares in Windows OS.

- In the case of writing image file in linux there are two commands to write image file on the SD card after mounting SD card in the host linux same as WSL:

| Expand | |||||||

|---|---|---|---|---|---|---|---|

| |||||||

|

- After mounting the SD card in linux the name of SD card recognized via lsblk command. For example SD card name can be sda or sdb.

| Expand | |||||||

|---|---|---|---|---|---|---|---|

| |||||||

|

- After mounting the SD card in linux the name of SD card recognized via lsblk command. For example SD card name can be sda or sdb.

JTAG

Not used on this example.

Usage

- Prepare HW like described on section Hardware Setup

- Connect UART USB (most cases same as JTAG)

- Connect your board to the network

- Power on PCB

UART

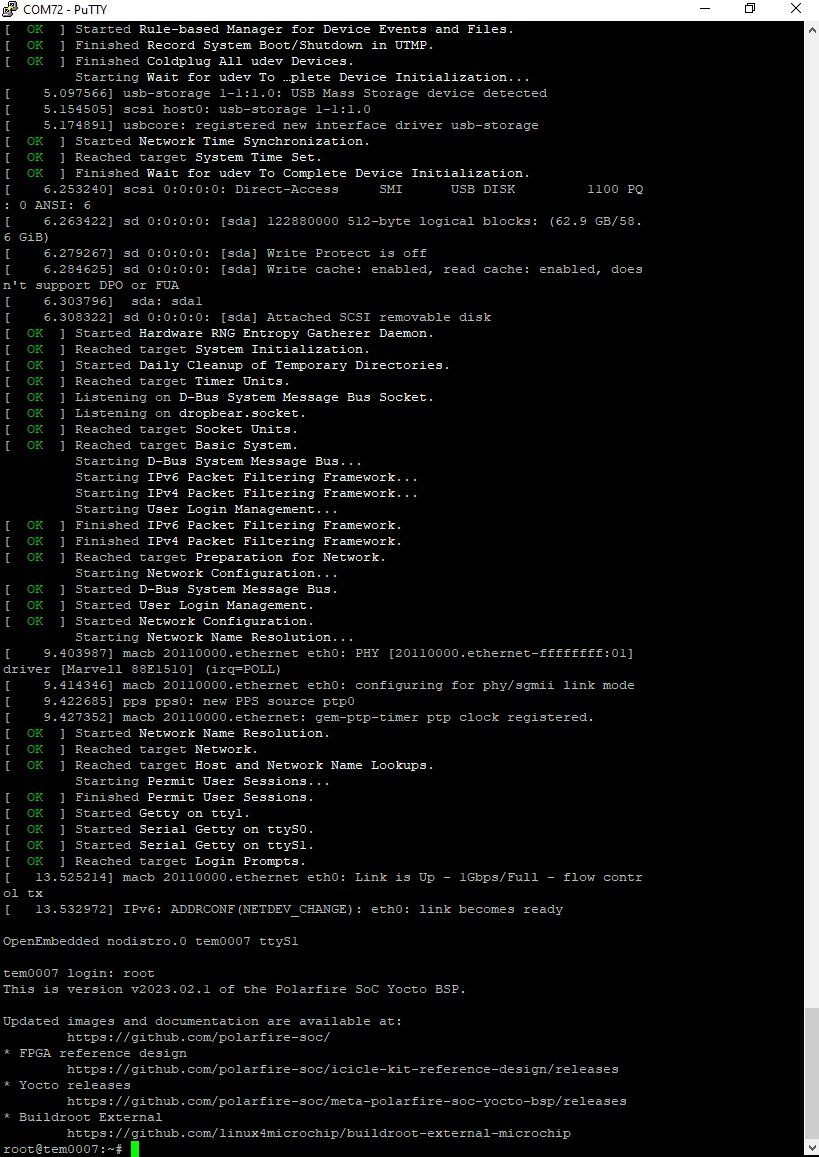

Open two serial console for HSS and Linux console (e.g. PuTTY)Select COM Port of linux console (UART1)

| Info |

|---|

Win OS: see device manager Linux OS: see dmesg | grep tty (UART is *USB1) |

Login data:

| Info |

|---|

Note: Wait until Linux boot finished |

| Code Block | ||||

|---|---|---|---|---|

| ||||

tem0007 login: root

|

You can use Linux shell now.

| Code Block | ||||

|---|---|---|---|---|

| ||||

i2cdetect -l (check I2C Bus)

ifconfig -a (ETH0 check)

lsusb (USB check) |

| Expand | ||

|---|---|---|

| ||

|

| Expand | ||

|---|---|---|

| ||

|

System Design - Libero

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

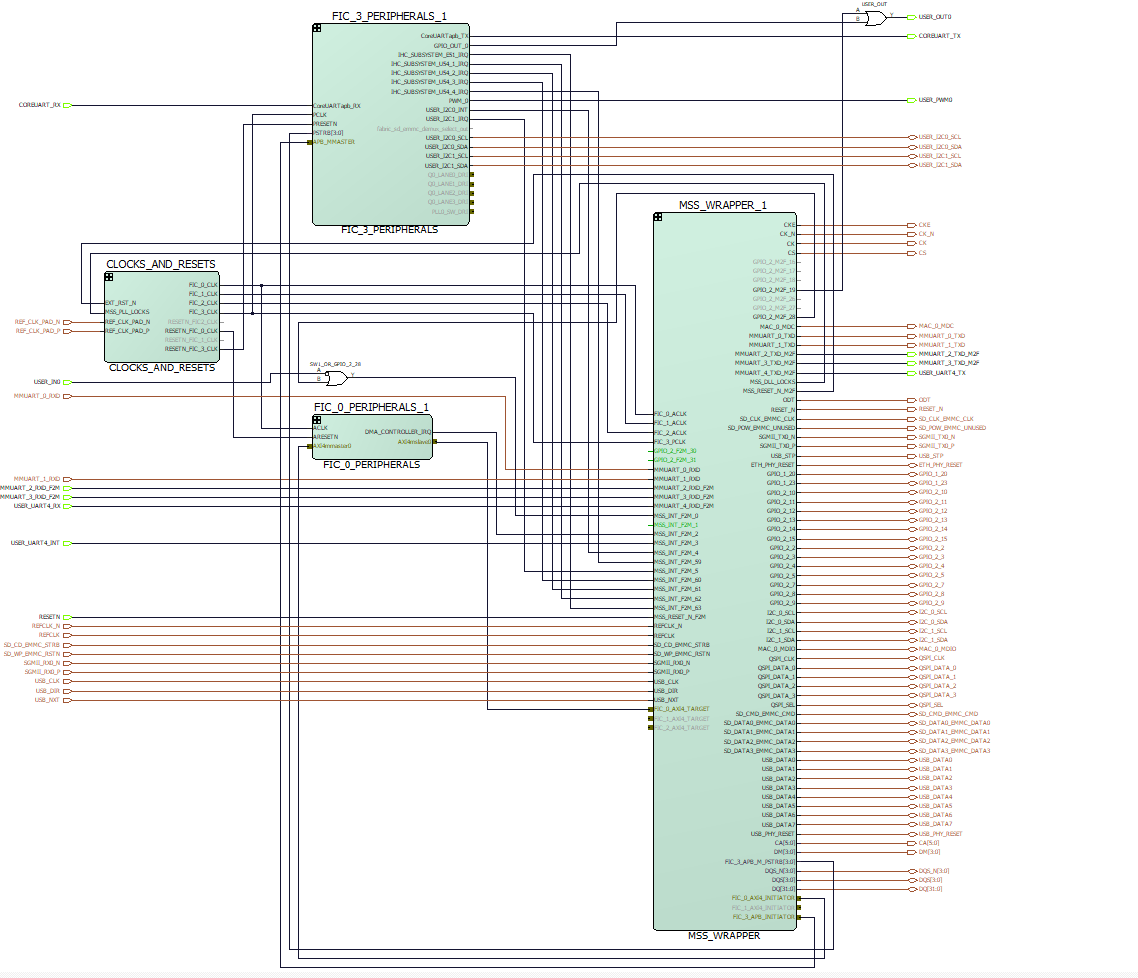

Block Design

The block designs may differ depending on the assembly variant.

| Scroll Title | ||||

|---|---|---|---|---|

| ||||

|

HPS Interfaces

Activated interfaces:

Software Design - SoftConsole

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

Application

| Page properties | ||||

|---|---|---|---|---|

| ||||

---------------------------------------------------------- General Example: hello_tei0006Hello TEI0006 is a Hello World example as endless loop instead of one console output. |

Template location: <project folder>/softconsole_source/

HSS (Hart Software Service)

This is Hart Software Services (HSS) code.On PolarFire SoC, this is comprised of two portions:

A superloop monitor running on the E51 minion processor, which receives requests from the individual U54 application processors to perform certain services on their behalf;

A Machine-Mode software interrupt trap handler, which allows the E51 to send messages to the U54s, and request them to perform certain functions for it related to rebooting a U54.

The HSS performs boot and system monitoring functions for PolarFire SoC. The HSS is compressed (DEFLATE) and stored in eNVM. On power-up, a small decompressor wrapper inflates the HSS from eNVM flash to L2-Scratchpad memory and starts the HSS.

Creating HSS workspace in SoftConsole

| Expand | ||

|---|---|---|

| ||

|

- hart-software-serevices-2023.02

- board

- TEM0007

- drivers_config

- fpga_ip

- miv_ihc

- Copy miv_ihc_add_mapping.h and miv_ihc_config.h files from original folder of icicle kit board ( mpfs-icicle-kit-es ) and paste in this folder.

- miv_ihc

- fpga_ip

- fpga_design_config

- This folder should be left empty. After compiling the neccessary header files for ddr, clock, IOs and other properties of desired module and hardware design will be generated and saved in this folder by mpfs_configuration_generator.py python script. The python script is saved already in the tools/polarfire-soc-configuration-generator folder.

- This folder should be left empty. After compiling the neccessary header files for ddr, clock, IOs and other properties of desired module and hardware design will be generated and saved in this folder by mpfs_configuration_generator.py python script. The python script is saved already in the tools/polarfire-soc-configuration-generator folder.

- mpfs_hal_config

- Copy mss_sw_config.h file from original folder of icicle kit board ( mpfs-icicle-kit-es ) and paste

- Copy mss_sw_config.h file from original folder of icicle kit board ( mpfs-icicle-kit-es ) and paste

- soc_fpga_design

- xml

- Copy the generated xml with PolarFireSoC MSS Configurator software here. For example TEM0007_MSS_mss_cfg.xml

- Copy the generated xml with PolarFireSoC MSS Configurator software here. For example TEM0007_MSS_mss_cfg.xml

- xml

- Copy the following files from original folder of icicle kit board ( mpfs-icicle-kit-es ) and paste in this folder (TEM0007 folder) :

- hss_board_init.c

- hss_usrt_init.c

- usrt_helper.c

- hss_I2Scratch.lds

- Kconfig

- Edit Kconfig for example for TEM0007 module as shown:

Expand title Kconfig Code Block title Kconfig menu "TEM0007 Design Configuration Options" config SOC_FPGA_DESIGN_XML string "Enter path to Libero XML file" default "boards/$(BOARD)/soc_fpga_design/xml/TEM0007_MSS_mss_cfg.xml" help This option specifies the design XML file to use. endmenu

- Edit Kconfig for example for TEM0007 module as shown:

- drivers_config

- TEM0007

- board

- Makefile

- Edit Makefile for example for TEM0007 module as shown:

Expand title Makefile of TEM0007 folder Scroll Title title-alignment center title Makefile of TEM0007 folder  Image Removed

Image Removed

- Edit Makefile for example for TEM0007 module as shown:

- Makefile

| Expand | |||||||

|---|---|---|---|---|---|---|---|

| |||||||

|

| title | .config File |

|---|

# Board/Design Configuration Options

#

#

# TEM0007 Trenz electronic GmbH polarfire SoC module Design Configuration Options

#

CONFIG_SOC_FPGA_DESIGN_XML="boards/TEM0007/soc_fpga_design/xml/TEM0007_MSS_mss_cfg.xml"

# end of TEM0007 Design Configuration Options

# end of Board/Design Configuration Options

#

# Services

#

CONFIG_SERVICE_BEU=y

CONFIG_SERVICE_BOOT=y

#

# Boot Service

#

# CONFIG_SERVICE_BOOT_USE_PAYLOAD is not set

# CONFIG_SERVICE_BOOT_CUSTOM_FLOW is not set

CONFIG_SERVICE_BOOT_DDR_TARGET_ADDR=0x8e000000

CONFIG_SERVICE_BOOT_MMC_USE_GPT=y

# end of Boot Service

CONFIG_SERVICE_DDR=y

CONFIG_SERVICE_GOTO=y

CONFIG_SERVICE_IPI_POLL=y

CONFIG_SERVICE_MMC=y

#

# MMC

#

#

# MMC Mode

#

# CONFIG_SERVICE_MMC_MODE_EMMC is not set

CONFIG_SERVICE_MMC_MODE_SDCARD=y

# end of MMC Mode

#

# MMC Voltage

#

# CONFIG_SERVICE_MMC_BUS_VOLTAGE_1V8 is not set

# end of MMC Voltage

#

# SDIO Control

#

CONFIG_SERVICE_MMC_FABRIC_SD_EMMC_DEMUX_SELECT_PRESENT=y

CONFIG_SERVICE_MMC_FABRIC_SD_EMMC_DEMUX_SELECT_ADDRESS=0x4fffff00

# end of SDIO Control

CONFIG_SERVICE_MMC_SPIN_TIMEOUT=y

# CONFIG_SERVICE_MMC_SPIN_TIMEOUT_ASSERT is not set

CONFIG_SERVICE_MMC_SPIN_TIMEOUT_MAX_SPINS=1000000

# end of MMC

CONFIG_SERVICE_OPENSBI=y

CONFIG_SERVICE_OPENSBI_IHC=y

CONFIG_SERVICE_OPENSBI_RPROC=y

# CONFIG_SERVICE_POWERMODE is not set

# CONFIG_SERVICE_QSPI is not set

CONFIG_SERVICE_SCRUB=y

#

# RAM Scrubbing Service

#

CONFIG_SERVICE_SCRUB_MAX_SIZE_PER_LOOP_ITER=4096

CONFIG_SERVICE_SCRUB_RUN_EVERY_X_SUPERLOOPS=256

# CONFIG_SERVICE_SCRUB_CACHED_DDR is not set

# end of RAM Scrubbing Service

CONFIG_SERVICE_SGDMA=y

# CONFIG_SERVICE_SPI is not set

CONFIG_SERVICE_TINYCLI=y

#

# Tiny Command Line Interface

#

CONFIG_SERVICE_TINYCLI_TIMEOUT=1

CONFIG_SERVICE_TINYCLI_REGISTER=y

# CONFIG_SERVICE_TINYCLI_MONITOR is not set

# CONFIG_SERVICE_TINYCLI_ENABLE_PREBOOT_TIMEOUT is not set

# end of Tiny Command Line Interface

# CONFIG_SERVICE_UART is not set

CONFIG_SERVICE_USBDMSC=y

#

# USB Device Mass Storage Class

#

CONFIG_SERVICE_USBDMSC_REGISTER=y

# CONFIG_SERVICE_USBDMSC_ENABLE_MAX_SESSION_TIMEOUT is not set

# end of USB Device Mass Storage Class

CONFIG_SERVICE_WDOG=y

#

# Watchdog Service

#

# CONFIG_SERVICE_WDOG_DEBUG is not set

CONFIG_SERVICE_WDOG_DEBUG_TIMEOUT_SEC=240

CONFIG_SERVICE_WDOG_ENABLE_E51=y

# end of Watchdog Service

# CONFIG_SERVICE_YMODEM is not set

# end of Services

#

# General Configuration Options

#

#

# Miscellaneous

#

#CONFIG_USE_PCIE=y

CONFIG_USE_PCIE=n

CONFIG_OPENSBI=y

CONFIG_USE_IHC=y

#

# Tamper

#

# CONFIG_USE_TAMPER is not set

# end of Tamper

CONFIG_ALLOW_COLDREBOOT=y

#

# Cold Reboot

#

CONFIG_ALLOW_COLDREBOOT_ALWAYS=y

# CONFIG_ALLOW_COLDREBOOT_ON_OPENSBI_FAULT is not set

# end of Cold Reboot

# end of Miscellaneous

#

# OpenSBI

#

# CONFIG_PROVIDE_DTB is not set

# end of OpenSBI

#

# Memory Options

#

# CONFIG_SKIP_DDR is not set

# CONFIG_MEMTEST is not set

# CONFIG_USE_PDMA is not set

# CONFIG_INITIALIZE_MEMORIES is not set

# end of Memory Options

# end of General Configuration Options

#

# Build Options

#

CONFIG_COLOR_OUTPUT=y

CONFIG_USE_LOGO=y

#

# Logo

#

CONFIG_LOGO_INVERT_COLORS=y

# end of Logo

# CONFIG_CC_STACKPROTECTOR_STRONG is not set

# CONFIG_CC_DUMP_STACKSIZE is not set

# CONFIG_LD_RELAX is not set

CONFIG_CC_USE_MAKEDEP=y

CONFIG_CC_USE_GNU_BUILD_ID=y

CONFIG_CC_HAS_INTTYPES=y

CONFIG_DISPLAY_TOOL_VERSIONS=y

# CONFIG_LOG_FUNCTION_NAMES is not set

# end of Build Options

#

# Compression

#

CONFIG_COMPRESSION=y

CONFIG_COMPRESSION_MINIZ=y

# end of Compression

#

# Crypto

#

# CONFIG_CRYPTO_SIGNING is not set

# end of Crypto

#

# Debug Options

#

CONFIG_DEBUG_LOG_STATE_TRANSITIONS=y

CONFIG_DEBUG_LOOP_TIMES=y

CONFIG_DEBUG_LOOP_TIMES_THRESHOLD=2500000

# CONFIG_DEBUG_IPI_STATS is not set

# CONFIG_DEBUG_CHUNK_DOWNLOADS is not set

# CONFIG_DEBUG_MSCGEN_IPI is not set

# CONFIG_DEBUG_PROFILING_SUPPORT is not set

CONFIG_DEBUG_PERF_CTRS=y

CONFIG_DEBUG_PERF_CTRS_NUM=16

# CONFIG_DEBUG_RESET_REASON is not set

# end of Debug Options

#

# SSMB Options

#

# CONFIG_HSS_USE_IHC is not set

CONFIG_IPI_MAX_NUM_QUEUE_MESSAGES=8

# CONFIG_IPI_FIXED_BASE is not set

# end of SSMB Options

- and follow instructions on the console :

- The script searches for a suitable Libero SoC installation at the beginning and lists them plus some other option to manually guide the script to the Libero SoC installation of your liking .

- Further will the script offer options to chose from :

- Upgrade all Libero SoC General Soft Cores

- Select your Trenz Board Subversion / Assembly Variant from a list

- Select the set of Soft Cores to be used during project generation. The set of soft cores versions used during development or the newest available versions and if possible this selection is possible , download them or use a copy from the Trenz Download

- When necessary , to resolve a Folder Overwrite Conflict

- Chose your prefered Hardware Description Language (VHDL / Verilog)

- After the project generation , the script continues with the following options :

- Compile the bitstream of the project and obtain the Programming Files

- Open the project for use

Code Block language xml theme Midnight title Project generation script console messages linenumbers true collapse true E:\Microchip_svn\23.1\designs\TEM0007\test_board\scripts\ Generate_TEM0007_Hardware-Design_in_Libero_SoC_v2023.1 --------------- Start : design_subversion_setup.tcl --------------- ### Autostart via System Path Variable "acttclsh" ### - Probing for acttclsh.exe "where acttclsh" INFORMATION: Es konnten keine Dateien mit dem angegebenen Muster gefunden werden. ### Autostart via System Path Variable "tclsh" ### - Probing for tclsh.exe "where tclsh" INFORMATION: Es konnten keine Dateien mit dem angegebenen Muster gefunden werden. ### Autostart searching for default Libero SoC installation ### - Searching for acttclsh.exe List of Libero_SoC installations in c:\Microchip\ and their TCL Shell(s) : Libero_SoC_v2023.1 c:\Microchip\Libero_SoC_v2023.1\Designer\bin\acttclsh.exe # Autostart via Libero_SoC TCL Shell # - Executing script Using TCL Shell c:\Microchip\Libero_SoC_v2023.1\Designer\bin\acttclsh.exe Processing script parameters : Setting dict key:windowWidth value:118 pair Console window has width : 118 Parameter path not an argument to this script : key "path" not known in dictionary -------------------- TEM0007 test_design -------------------- TCL Version : 8.6 This script generates the Hardware Design for the Trenz Electronic module series TEM0007. The Hardware Design itself is a Microchip Libero SoC Design Suite project. This script requires a Libero SoC installation equal or later than : Libero SoC Version 2023.1 [When the built stops with the error message : Error: Cannot find Spirit core configuration file for vendor:.. library:.. name:.. version:... Error: The command 'create_and_configure_core' failed. Upgrading the Libero SoC Soft Core Catalog can help . To do so , use the script option to upgrade the cores later in this script . Manually this is done via : Open Libero and go to the Soft Core Catalog via "View > Windows > Catalog" and press the button "Download them now!" .] Found Libero SoC installations in default folder : C:/Microchip/Libero_SoC_v2023.1 C:/Microsemi/Libero_SoC_v2021.2 C:/Microsemi/Libero_SoC_v12.4 ### Select from the following options which Libero SoC version should be used to build the design : Option 0 : C:/Microchip/Libero_SoC_v2023.1/Designer/bin/libero.exe Option 1 : Enter path to your Microchip or Libero SoC installations folder The script selects automatically the Libero exe Option 2 : Enter the full path to your Libero SoC exe Option 3 : Exit the script Selection : (0 to 3) 0 Using Libero SoC @ : C:/Microchip/Libero_SoC_v2023.1/Designer/bin/libero.exe ### Do you wish to update the Libero SoC Soft Cores ? (Yes = y/t/1 or No = n/f/0) : 1 Updating soft cores started Console Mode = Downloading Microchip:SolutionCore:YCbCrtoRGB:4.6.0... OK Info: Core 'Microchip:SolutionCore:YCbCrtoRGB:4.6.0' was successfully downloaded. Downloading Microsemi:MiV:MIV_RV32:3.1.200... OK ### Hardware Designs are available for these variants : ID : PRODID FAMILY DEVICE PACKAGE SPEED TEMP SHORTNAME FLASH_SIZE DDR_SIZE PCB_REV NOTES 1 : TEM0007-01-S002 "PolarfireSoC" MPFS250T_ES FCVG484 STD EXT 25_1E0_ES_1GB NA 1GB REV01 "produced prototyp" 2 : TEM0007-01-CHE11-A "PolarfireSoC" MPFS250T FCVG484 STD EXT 250_1E_1GB NA 1GB REV01 "produced" 3 : TEM0007-01-CAA11-A "PolarfireSoC" MPFS025T FCVG484 STD EXT 025_1E_1GB NA 1GB REV01 "currently factory order 5555" 4 : TEM0007-01-CAD11-A "PolarfireSoC" MPFS025T FCVG484 -1 IND 025_1I_1GB NA 1GB REV01 "currently ERP only" 5 : TEM0007-01-CBD11-A "PolarfireSoC" MPFS095T FCVG484 -1 IND 095_1I_1GB NA 1GB REV01 "currently factory order 5555" 6 : Exit script Enter ID number of your board (1 to 6) : 1 ### Which Soft Core Versions should be used to generate the Hardware Design ? (The design can be generated with local sources , when a Libero SoC version with the same major version is used) Option 0 : Download the newest soft core versions Option 1 : Download the soft cores versions , for which the Hardware Design was verified Option 2 : Use a local copy of the soft cores sources , which the Hardware Design was verified for Option 3 : Exit script Selection : (0 to 3) 1 ### Folder overwrite protection . Checking for existing Libero SoC project folder named "libero_25_1E0_ES_1GB" : Found existing Libero SoC project folder "libero_25_1E0_ES_1GB" Select how to proceed : Option 0 : Overwrite this Libero SoC project folder Option 1 : Enter new Libero SoC project folder name Option 2 : Exit script Selection : (0 to 2) 0 ### Which Hardware Description Language do you prefer : VHDL or Verilog ? Option 0 : VHDL Option 1 : Verilog Option 2 : Exit script Selection : (0 to 2) 0 ### Determine expected Libero SoC Project path lengths : Expected maximum Libero SoC Project path length : root + project name + relatvive path = path length 48 + 21 + 135 = 204 The root path length is well below the Libero SoC Path Length Limit of 250 chars . The Hardware Designs Build / Synthesis or Bitstream generation should succeeded . ### Building the hardware design started at 17:17:38 , this will take some minutes . [In rare cases, this console may not advance from here on . Visible through a not blinking cursor. Wait some minutes , focus the console and press space, the script will continue .] ### Checking the results via log evaluation : Hardware design generation was successfull The projects path is : E:/Microchip_svn/23.1/designs/TEM0007/test_board/libero_25_1E0_ES_1GB The build log "libero_25_1E0_ES_1GB_build_2024.02.19_171738.log" was saved to : E:/Microchip_svn/23.1/designs/TEM0007/test_board/log ### Hardware Design Compilation and Bitstream Generation : Do you want the these files to be build and exported ? Selection (Yes = y/t/1 or No = n/f/0) : 1 Generating folders for prebuilt files Folder bitstream already exists and will be overwritten Folder flashpro already exists and will be overwritten ### Executing the prebuilt started at 17:22:24 , this will take some minutes . ### Checking the results via log evaluation : Generation and export of Prebuilt Files was successfull The files have been exported to the subfolders bitstream and flashpro inside : E:/Microchip_svn/23.1/designs/TEM0007/test_board/prebuilt/hardware/25_1E0_ES_1GB The prebuilt log "libero_25_1E0_ES_1GB_prebuilt_2024.02.19_171738.log" was saved to : E:/Microchip_svn/23.1/designs/TEM0007/test_board/log ### Open the generated Libero Soc TEM0007 test_design ? Selection (Yes = y/t/1 or No = n/f/0) : 1 Please press any key . . .

- Now the generated and exported files existing in prebuilt folder are without HSS generated hex/elf file. If the hex file is attached to job file it will not be necessary to program HSS generated hex file on eNVM memory. To attach the hex file to job file execute the following instructions (optional).

Note In test board reference zip file the job files in prebuilt folder consist of HSS generated hex file. The following instruction are only to know , how the final job file is prepared and regenerated.

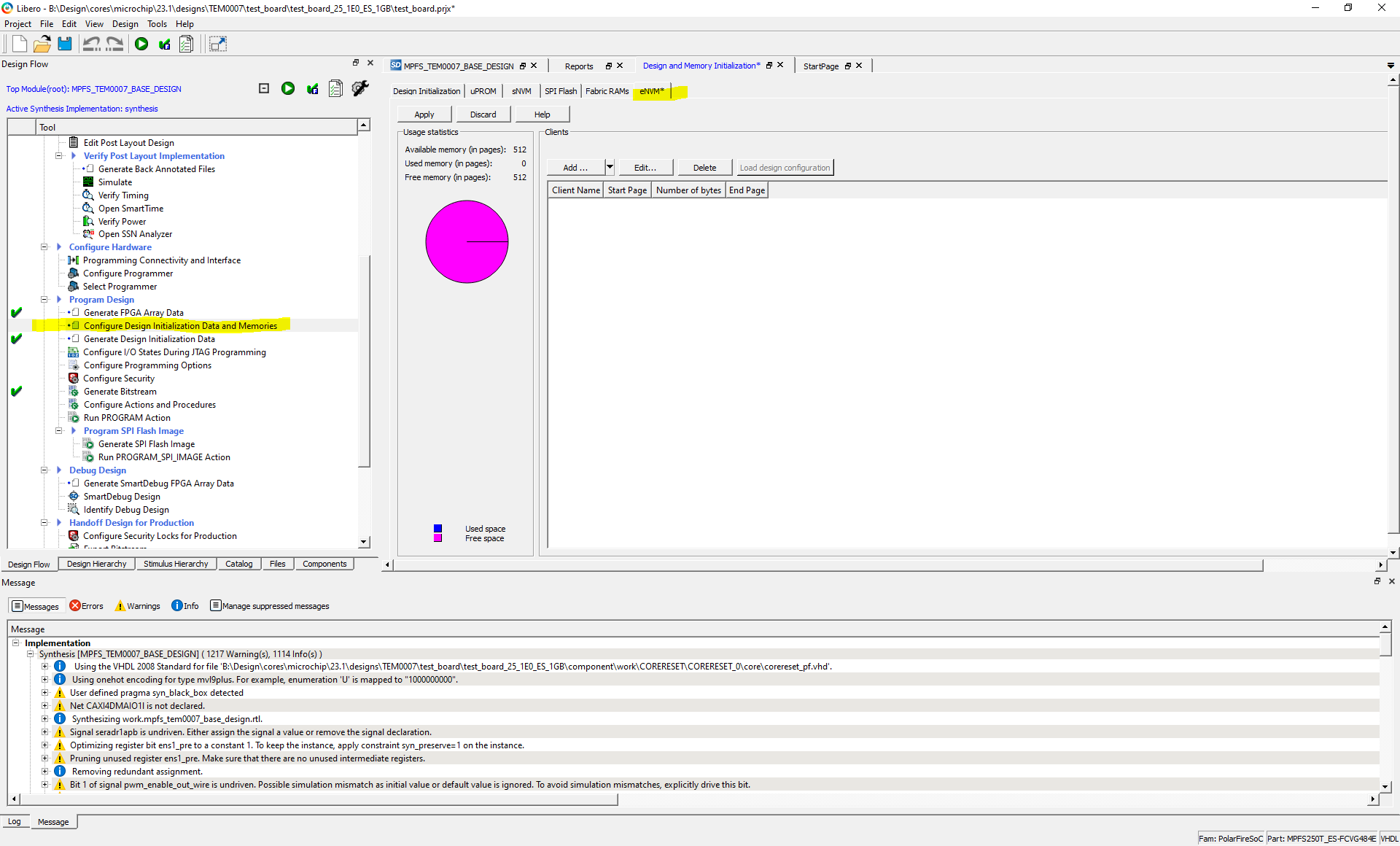

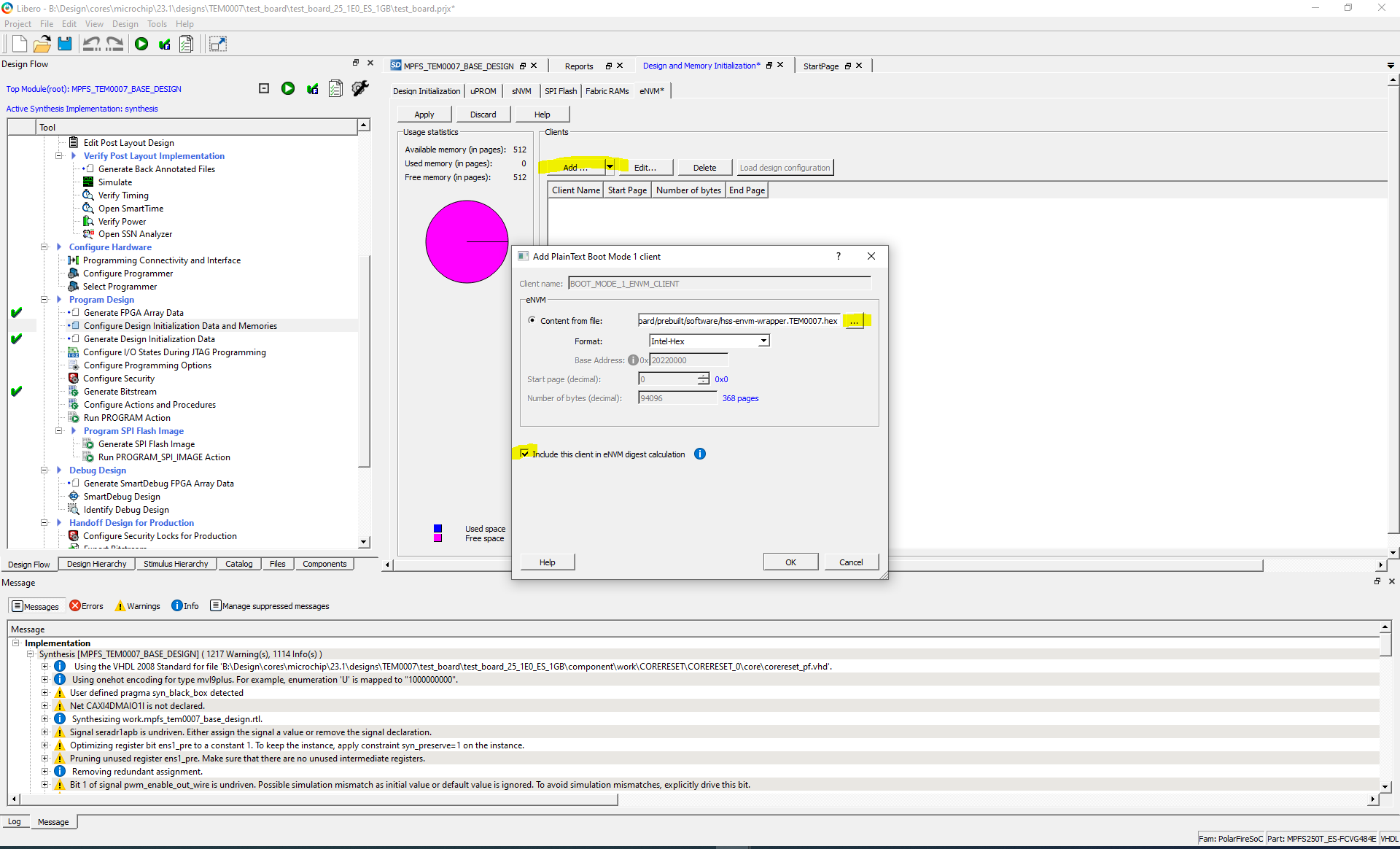

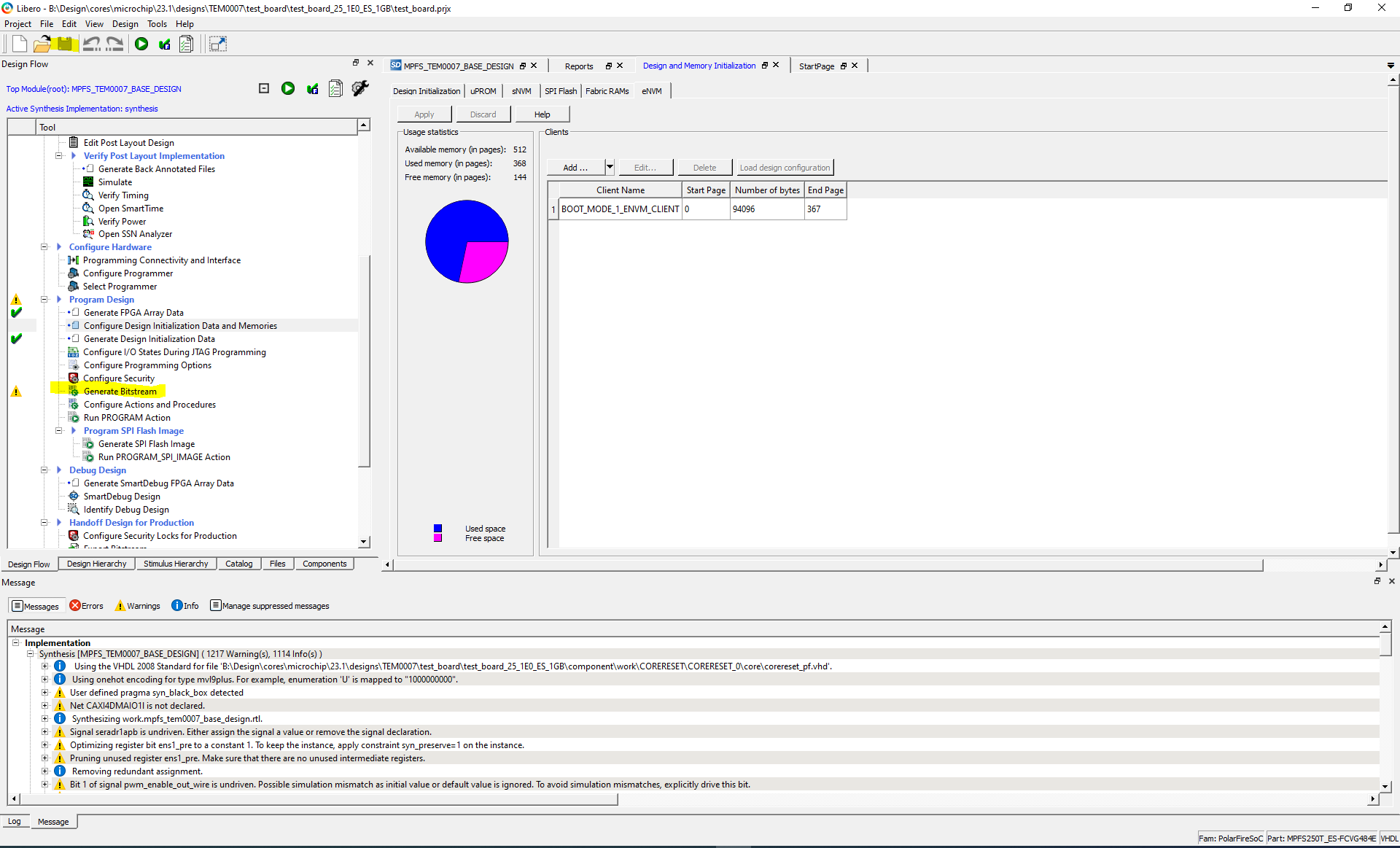

- After generating bitstream file double click on "Configure Design Initialization Data and Memories" in Design Flow now.

Expand title Configure Memory  Image Added

Image Added - Click on eNVM and after that on Add and click on Add Boot Mode 1 Client.

- Enter the path of generated *.hex File by SoftConsole software (HSS) or the path of saved *.hex file in prebuilt folder ( for example "...\test_board\prebuilt\hardware\250_1E_1GB"and click on OK.

Expand title HSS generated *.hex File attachment  Image Added

Image Added - Save the project and double click on Generate Bitstream.

Expand title Generate Bitstream again  Image Added

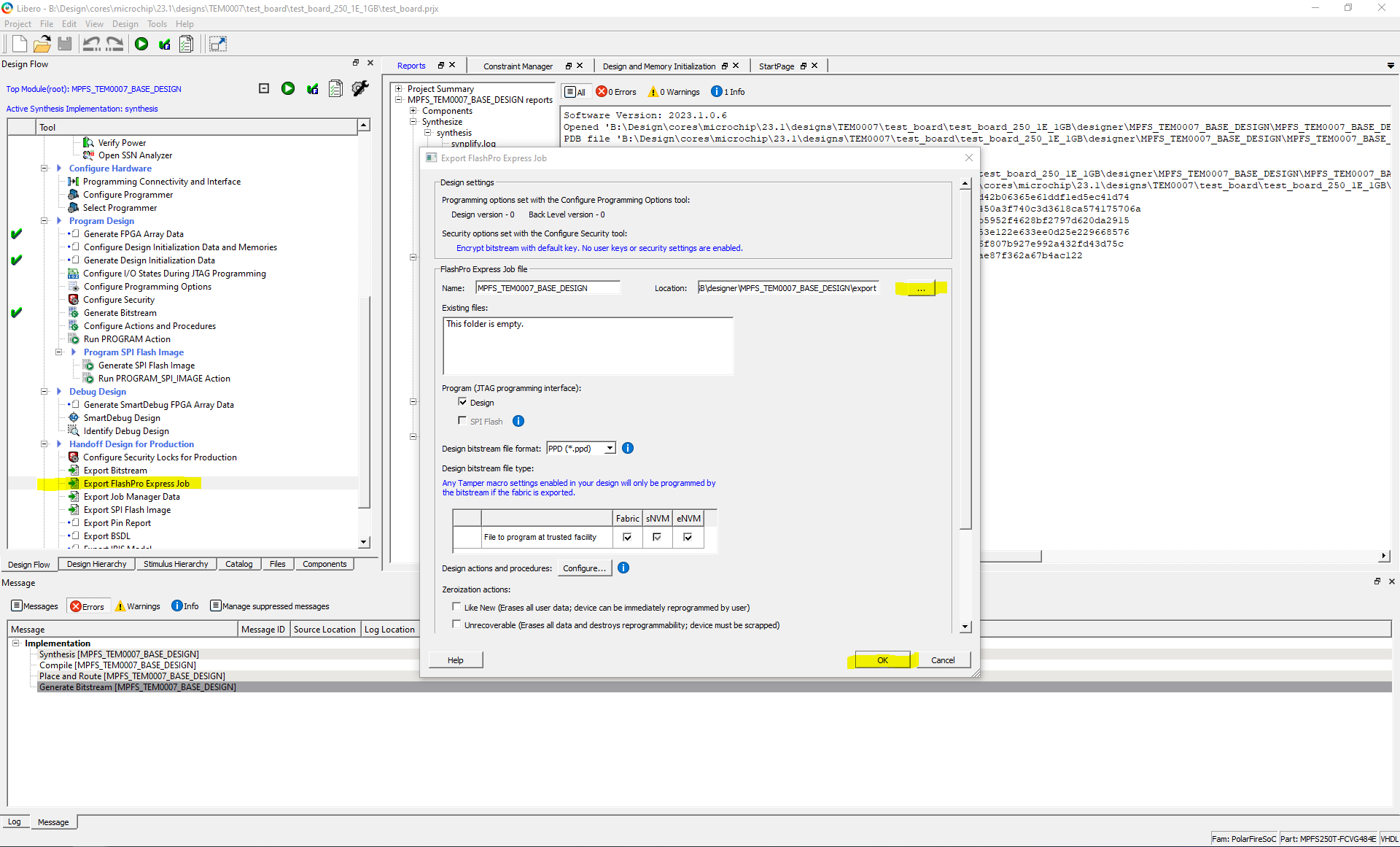

Image Added - Double click on "Export Flashpro ExpressJob" and enter the desired path for *.job file to generate .job File. The *.job will be used to program the polarfire soc in FPExpress software.

Expand title Generate Job File  Image Added

Image Added

Launch

| Scroll Ignore |

|---|

| Page properties | ||||

|---|---|---|---|---|

| ||||

Get prebuilt boot binaries

|

Hardware Setup

| Page properties | ||||

|---|---|---|---|---|

| ||||

|

- Connect the TEB2000 carrier board via its J4 mini USB connector to the PC. (For Linux console)

- Connect the TEB2000 carrier board via its J21 mini USB connector to the PC. (For HSS console)

- Connect the 5V power supply to 5V input voltage connector J13.

- Connect the RJ45 network cable to the ethernet interface J14.

- Connect the USB stick to the USB stick socket J12.

- For more information see TEB2000 Getting Started

Programming Bitstream

| Page properties | ||||

|---|---|---|---|---|

| ||||

| Describe how to programm the bitstream of the design onto the board or carrier . |

| Note |

|---|

Check module and carrier TRMs for proper HW configuration before you try any design. |

There is two ways to program bitstream file on FPGA. The Bitstream can be programmed into the FPGA / SOC by Libero SoC or Flash Pro Express :

Using Libero SoC

- Prepare the hardware see Hardware Setup

- Double click onto "Run PROGRAM Action" to program the Polarfire SoC.

| Expand | ||

|---|---|---|

| ||

|

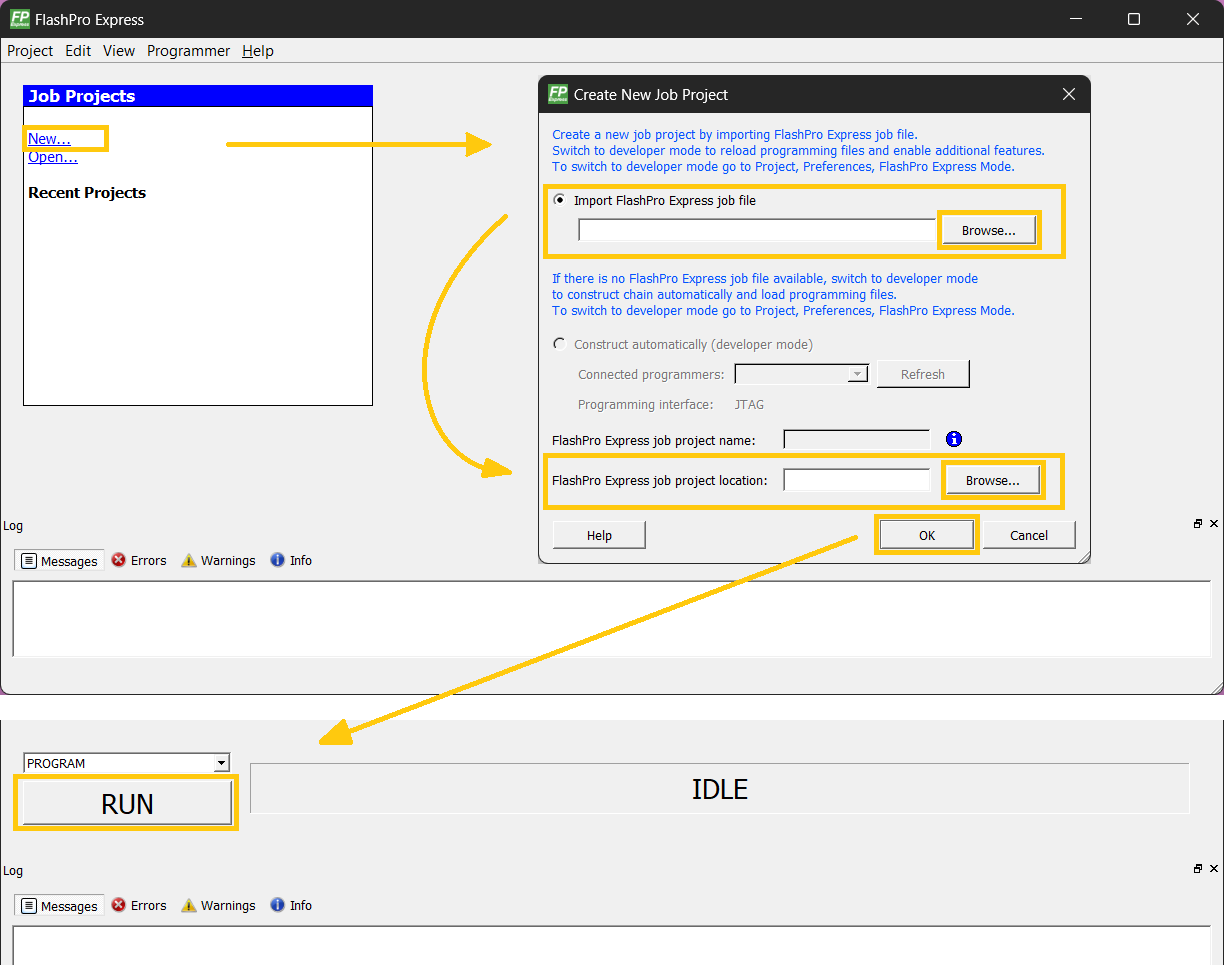

Using FPExpress software

- Prepare the hardware see Hardware Setup

- Click on NEW... to open the "Creat New Job Project" dialog

- Clicking onto the upper Browse... button to specify the Programming Job File location

- Clicking onto the lower Browse... button to specify the location of where to store the FlashPro Express Job Project which will be created .The Job Project name automatically uses the programming job name and cannot be changed .

- Click OK and a new Job Project will be created and opened for production programming

- Click on RUN to start the programming of a board

| Expand | ||

|---|---|---|

| ||

|

Programming eNVM

| Page properties | ||||

|---|---|---|---|---|

| ||||

| Describe how to programm the bitstream of the design onto the board or carrier . |

The eNVM is a user non-volatile flash memory that can be programmed independently. There is two methods to program eNVM:

Programming eNVM in SoftConsole

To program HSS *.hex file on FPGA:

- Prepare the hardware see Hardware Setup

- Open SoftConsole software as administrator, if it is not done yet.

- Select correct directory as workspace directory and import hart-software-services source code.

- Right click on the hart-software-services and click on Build Project, if it is not done yet. For more information see Hart Software Services (HSS)

- Click on Run > External Tools > Polarfire SoC program non-secure boot-mode 1

Programming eNVM in Flashpro Express

The HSS generated hex file can be attached to bitstream file. For more information see Design Flow

To program the eNVM in Flashpro Express see Using FlashPro Express

| Page properties | ||||

|---|---|---|---|---|

| ||||

Get prebuilt boot binaries

|

SD-Boot mode

This module supports SD card boot and JTAG boot mode. The selection between them will be done in HSS, so there is no need to select the boot mode via Dip Switches .

Prepare SD card as follows for SD card boot mode:

- Extract SD_Card.zip file

- Now there is a image file (SD_Card.img)

- Alternative SD card can be written via win32diskimager or balenaEtcher softwares in Windows OS.

- In the case of writing image file in linux there are two commands to write image file on the SD card after mounting SD card in the host linux same as WSL:

Expand title bmaptool command Code Block theme Midnight linenumbers true bmaptool copy --nobmap <Path of image file *.img> /dev/sdX- After mounting the SD card in linux the name of SD card recognized via "lsblk" command. For example SD card name can be sda or sdb.

Expand title dd command Code Block theme Midnight linenumbers true dd if=<Path of image file *.img> of=/dev/sdX- After mounting the SD card in linux the name of SD card recognized via lsblk command. For example SD card name can be sda or sdb.

JTAG

Not used on this example.

Usage

- Prepare HW like described on section Hardware Setup

- Power on PCB

UART

- Open two serial console for HSS and Linux console (e.g. PuTTY)

Select COM Port of linux console (UART1)

Info Win OS: see device manager

Linux OS: see dmesg | grep tty (UART is *USB1)

- Select COM port of HSS console (UART0)

- Speed for both consoles : 115200

- Press reset button

- Console output depends on used software project, see Application

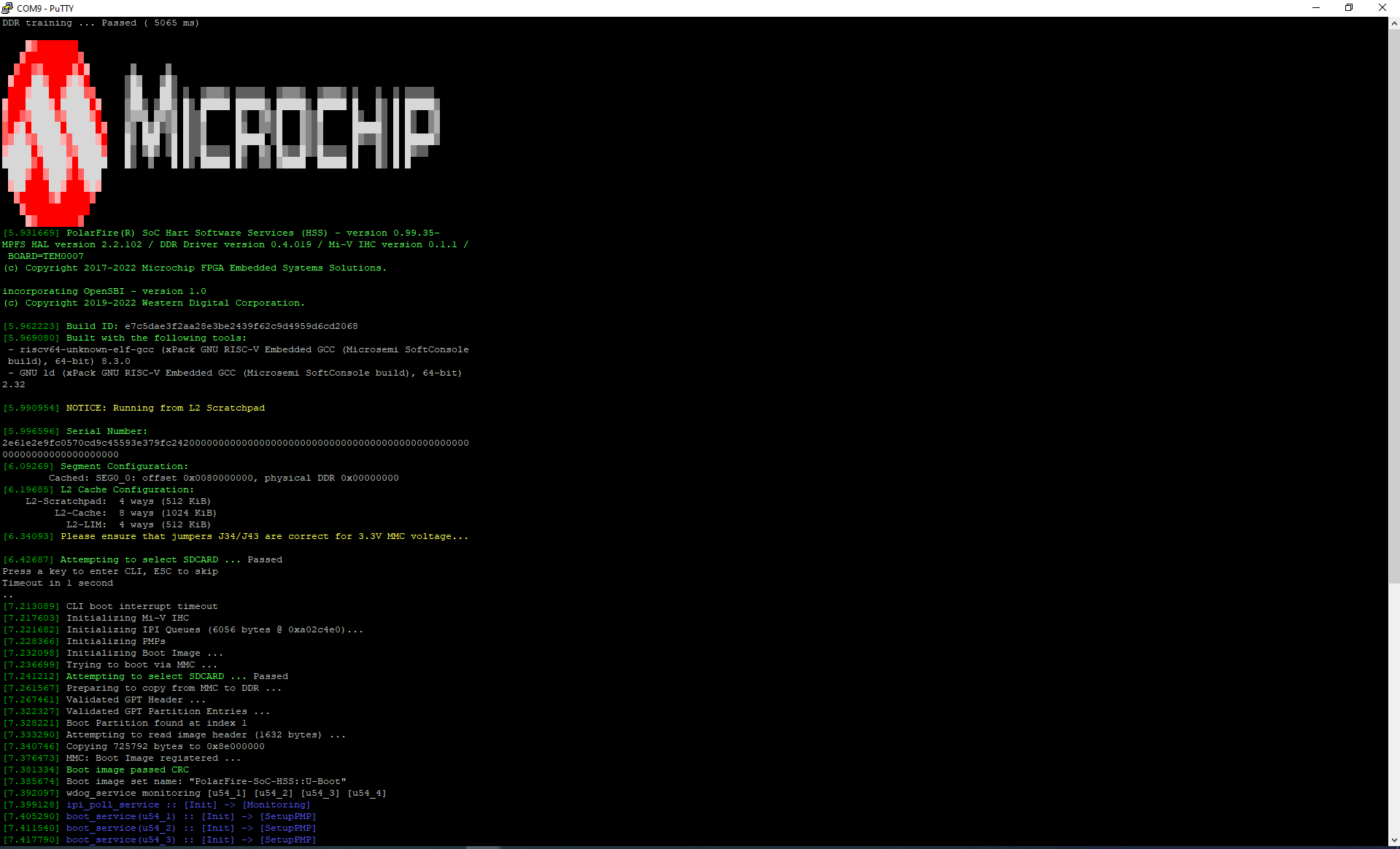

- HSS console (UART0):

- This console can be monitored by user , to know some additional information same as SD card status ( If SD card by booting is detected or not) , U54 cores status or memory size , ....

Expand title HSS Console  Image Added

Image Added

- This console can be monitored by user , to know some additional information same as SD card status ( If SD card by booting is detected or not) , U54 cores status or memory size , ....

- Linux Console (UART1):

Login data:

Info Note: Wait until Linux boot finished

Code Block theme Midnight linenumbers true tem0007 login: rootYou can use Linux shell now.

Code Block theme Midnight linenumbers true i2cdetect -l (check I2C Bus) ifconfig -a (ETH0 check) lsusb (USB check)Expand title Linux Console  Image Added

Image Added

System Design - Libero

| Scroll Ignore |

|---|

Block Design

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

The Block Design of a board variant or revision may differ slightly depending on the assembly variant.

| Scroll Title | ||||

|---|---|---|---|---|

| ||||

|

HPS Interfaces

| Page properties | ||||

|---|---|---|---|---|

| ||||

List of active interfaces of the design . Please update the list |

Activated interfaces:

| Type | Note |

| DDR | -- |

| EMAC0 | -- |

| GPIO1 | -- |

| GPIO2 | -- |

| I2C0 | -- |

| I2C1 | -- |

| SPI0 | -- |

| QSPI | -- |

| SDMMC | -- |

| UART0 | -- |

| UART1 | -- |

| USB | -- |

Constraints

| Page properties | ||||

|---|---|---|---|---|

| ||||

Insert all constraint files which the Hardware Design uses here . If a division into sub chapters is necessary , the subchapters "Basic module constrains" and "Design specific constrain" have been added . Delete them not necessary . |

| Code Block | ||

|---|---|---|

| ||

set_iobank -bank_name Bank0 \

-vcci 1.80 \

-fixed true \

-update_iostd true

set_iobank -bank_name Bank1 \

-vcci 3.30 \

-fixed true \

-update_iostd true

set_iobank -bank_name Bank4 \

-vcci 3.30 \

-fixed true \

-update_iostd true

|

| Code Block | ||

|---|---|---|

| ||

set_io -port_name REF_CLK_PAD_P \

-pin_name J19 \

-DIRECTION INPUT

set_io -port_name REF_CLK_PAD_N \

-pin_name J20 \

-DIRECTION INPUT |

| Code Block | ||

|---|---|---|

| ||

set_io -port_name GPIO_2_2 \

-pin_name D9 \

-fixed true \

-io_std LVCMOS33 \

-DIRECTION INOUT

set_io -port_name GPIO_2_3 \

-pin_name D6 \

-fixed true \

-io_std LVCMOS33 \

-DIRECTION INOUT

set_io -port_name GPIO_2_4 \

-pin_name C6 \

-fixed true \

-io_std LVCMOS33 \

-DIRECTION INOUT

set_io -port_name GPIO_2_7 \

-pin_name B5 \

-fixed true \

-io_std LVCMOS33 \

-DIRECTION INOUT

set_io -port_name GPIO_2_8 \

-pin_name C5 \

-fixed true \

-io_std LVCMOS33 \

-DIRECTION INOUT

set_io -port_name GPIO_2_9 \

-pin_name C4 \

-fixed true \

-io_std LVCMOS33 \

-DIRECTION INOUT

set_io -port_name GPIO_2_11 \

-pin_name F16 \

-fixed true \

-io_std LVCMOS33 \

-DIRECTION INOUT

set_io -port_name GPIO_2_12 \

-pin_name D14 \

-fixed true \

-io_std LVCMOS33 \

-DIRECTION INOUT

set_io -port_name GPIO_2_13 \

-pin_name E14 \

-fixed true \

-io_std LVCMOS33 \

-DIRECTION INOUT

set_io -port_name GPIO_2_14 \

-pin_name B4 \

-fixed true \

-io_std LVCMOS33 \

-DIRECTION INOUT |

| Code Block | ||

|---|---|---|

| ||

set_io -port_name MAC_0_MDC \

-pin_name H6 \

-fixed true \

-DIRECTION OUTPUT \

-io_std LVCMOS33

set_io -port_name MAC_0_MDIO \

-pin_name J3 \

-fixed true \

-DIRECTION INOUT \

-io_std LVCMOS33

|

| Code Block | ||

|---|---|---|

| ||

set_io -port_name MMUART_0_TXD \

-pin_name C2 \

-fixed true \

-DIRECTION OUTPUT \

-io_std LVCMOS33

set_io -port_name MMUART_0_RXD \

-pin_name D3 \

-fixed true \

-DIRECTION INPUT \

-io_std LVCMOS33 |

| Code Block | ||

|---|---|---|

| ||

set_io -port_name MMUART_1_TXD \

-pin_name H5 \

-fixed true \

-DIRECTION OUTPUT \

-io_std LVCMOS33

set_io -port_name MMUART_1_RXD \

-pin_name H2 \

-fixed true \

-DIRECTION INPUT \

-io_std LVCMOS33 |

| Code Block | ||

|---|---|---|

| ||

set_io -port_name USER_PWM0 \

-pin_name D7 \

-fixed true \

-io_std LVCMOS33 \

-RES_PULL Down \

-DIRECTION OUTPUT

set_io -port_name USER_IN0 \

-pin_name V19 \

-fixed true \

-DIRECTION INPUT

set_io -port_name USER_OUT0 \

-pin_name AB19 \

-fixed true \

-DIRECTION OUTPUT

# JM2-Pin73/ JB2-Pin74 / B13_L16_N (Suitable for modified TE0703)

#set_io -port_name RESETN \

-pin_name H13 \

-fixed true \

-io_std LVTTL \

-CLAMP_DIODE OFF \

-RES_PULL Up \

-DIRECTION INPUT

# JM2-Pin55 TEM0007 / JB2-Pin56 (SRST) TEB2000 / B13_L9_P

set_io -port_name RESETN \

-pin_name E15 \

-fixed true \

-io_std LVTTL \

-CLAMP_DIODE OFF \

-RES_PULL Up \

-DIRECTION INPUT

|

| Code Block | ||

|---|---|---|

| ||

set_io -port_name QSPI_CLK \

-pin_name C10 \

-fixed true \

-io_std LVCMOS33 \

-DIRECTION INOUT

set_io -port_name QSPI_DATA_0 \

-pin_name D13 \

-fixed true \

-io_std LVCMOS33 \

-DIRECTION INOUT

set_io -port_name QSPI_DATA_1 \

-pin_name B12 \

-fixed true \

-io_std LVCMOS33 \

-DIRECTION INOUT

set_io -port_name QSPI_DATA_2 \

-pin_name C9 \

-fixed true \

-io_std LVCMOS33 \

-DIRECTION INOUT

set_io -port_name QSPI_DATA_3 \

-pin_name C12 \

-fixed true \

-io_std LVCMOS33 \

-DIRECTION INOUT

set_io -port_name QSPI_SEL \

-pin_name A13 \

-fixed true \

-io_std LVCMOS33 \

-DIRECTION INOUT |

| Code Block | ||

|---|---|---|

| ||

create_generated_clock -name {CLOCKS_AND_RESETS_inst_0/CCC_FIC_x_CLK/PF_CCC_C0_0/pll_inst_0/OUT0} -multiply_by 5 -source [ get_pins { CLOCKS_AND_RESETS_inst_0/CCC_FIC_x_CLK/PF_CCC_C0_0/pll_inst_0/REF_CLK_0 } ] -phase 0 [ get_pins { CLOCKS_AND_RESETS_inst_0/CCC_FIC_x_CLK/PF_CCC_C0_0/pll_inst_0/OUT0 } ]

create_generated_clock -name {CLOCKS_AND_RESETS_inst_0/CCC_FIC_x_CLK/PF_CCC_C0_0/pll_inst_0/OUT1} -multiply_by 5 -source [ get_pins { CLOCKS_AND_RESETS_inst_0/CCC_FIC_x_CLK/PF_CCC_C0_0/pll_inst_0/REF_CLK_0 } ] -phase 0 [ get_pins { CLOCKS_AND_RESETS_inst_0/CCC_FIC_x_CLK/PF_CCC_C0_0/pll_inst_0/OUT1 } ]

create_generated_clock -name {CLOCKS_AND_RESETS_inst_0/CCC_FIC_x_CLK/PF_CCC_C0_0/pll_inst_0/OUT2} -multiply_by 5 -source [ get_pins { CLOCKS_AND_RESETS_inst_0/CCC_FIC_x_CLK/PF_CCC_C0_0/pll_inst_0/REF_CLK_0 } ] -phase 0 [ get_pins { CLOCKS_AND_RESETS_inst_0/CCC_FIC_x_CLK/PF_CCC_C0_0/pll_inst_0/OUT2 } ]

create_generated_clock -name {CLOCKS_AND_RESETS_inst_0/CCC_FIC_x_CLK/PF_CCC_C0_0/pll_inst_0/OUT3} -multiply_by 2 -source [ get_pins { CLOCKS_AND_RESETS_inst_0/CCC_FIC_x_CLK/PF_CCC_C0_0/pll_inst_0/REF_CLK_0 } ] -phase 0 [ get_pins { CLOCKS_AND_RESETS_inst_0/CCC_FIC_x_CLK/PF_CCC_C0_0/pll_inst_0/OUT3 } ]

create_generated_clock -name {CLOCKS_AND_RESETS_inst_0/PF_CLK_DIV_C1_0/PF_CLK_DIV_C1_0/I_CD/Y_DIV} -edges {1 7 11} -source [ get_pins { CLOCKS_AND_RESETS_inst_0/PF_CLK_DIV_C1_0/PF_CLK_DIV_C1_0/I_CD/A } ] [ get_pins { CLOCKS_AND_RESETS_inst_0/PF_CLK_DIV_C1_0/PF_CLK_DIV_C1_0/I_CD/Y_DIV } ]

set_false_path -through [ get_nets { FIC_0_PERIPHERALS_1/DMA_INITIATOR_inst_0/ARESETN* } ]

set_false_path -through [ get_nets { FIC_0_PERIPHERALS_1/FIC0_INITIATOR_inst_0/ARESETN* } ]

|

Software Design - SoftConsole

| Scroll Ignore |

|---|

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

| Page properties | ||||

|---|---|---|---|---|

| ||||

Describe How to generate / compile the application . Use sections for different applications . E.g. : |

Application

| Page properties | ||||

|---|---|---|---|---|

| ||||

---------------------------------------------------------- General Example: |

Template location: <project folder>/softconsole_source/

Hart Software Services (HSS)

Hart Software Services (HSS) code on PolarFire SoC, is comprised of two portions:

A superloop monitor running on the E51 minion processor, which receives requests from the individual U54 application processors to perform certain services on their behalf.

A Machine-Mode software interrupt trap handler, which allows the E51 to send messages to the U54s, and request them to perform certain functions for it related to rebooting a U54.

The HSS performs boot and system monitoring functions for PolarFire SoC. The HSS is compressed (DEFLATE) and stored in eNVM. On power-up, a small decompressor wrapper inflates the HSS from eNVM flash to L2-Scratchpad memory and starts the HSS.

Creating HSS workspace in SoftConsole

- Download the test board design zip file in the following path : TEM0007 "Test Board" Reference Design

- Unzip the test board zip file

- Copy the HSS folder (hart-software-services-<HSS version>) from softconsole_source folder in the SoftConsole workspace folder

- Open SoftConsole software as administrator

- Select correct directory as workspace directory. The workspace folder must consist of hart-software-services-<HSS version> folder. The hart-software-services-<HSS version> project can be imported in the workspace as an Existing project.

- Left click on board folder

- There is created already a subfolder for TEM0007 module and HSS is ready to be compiled as shown:

Expand title TEM0007 HSS  Image Added

Image Added - Right click on hart-software-services-<HSS version> and click on Build project to compile it.

- It is ready to program created hex file on the Polarfire SoC. See Programming eNVM

Note that HSS can be changed for every TEM0007 variant. Therefore the hex file for every variant is created and saved in the following path of test design folder separately: (<project folder>/prebuilt/soctware/<short name of the module variant>)

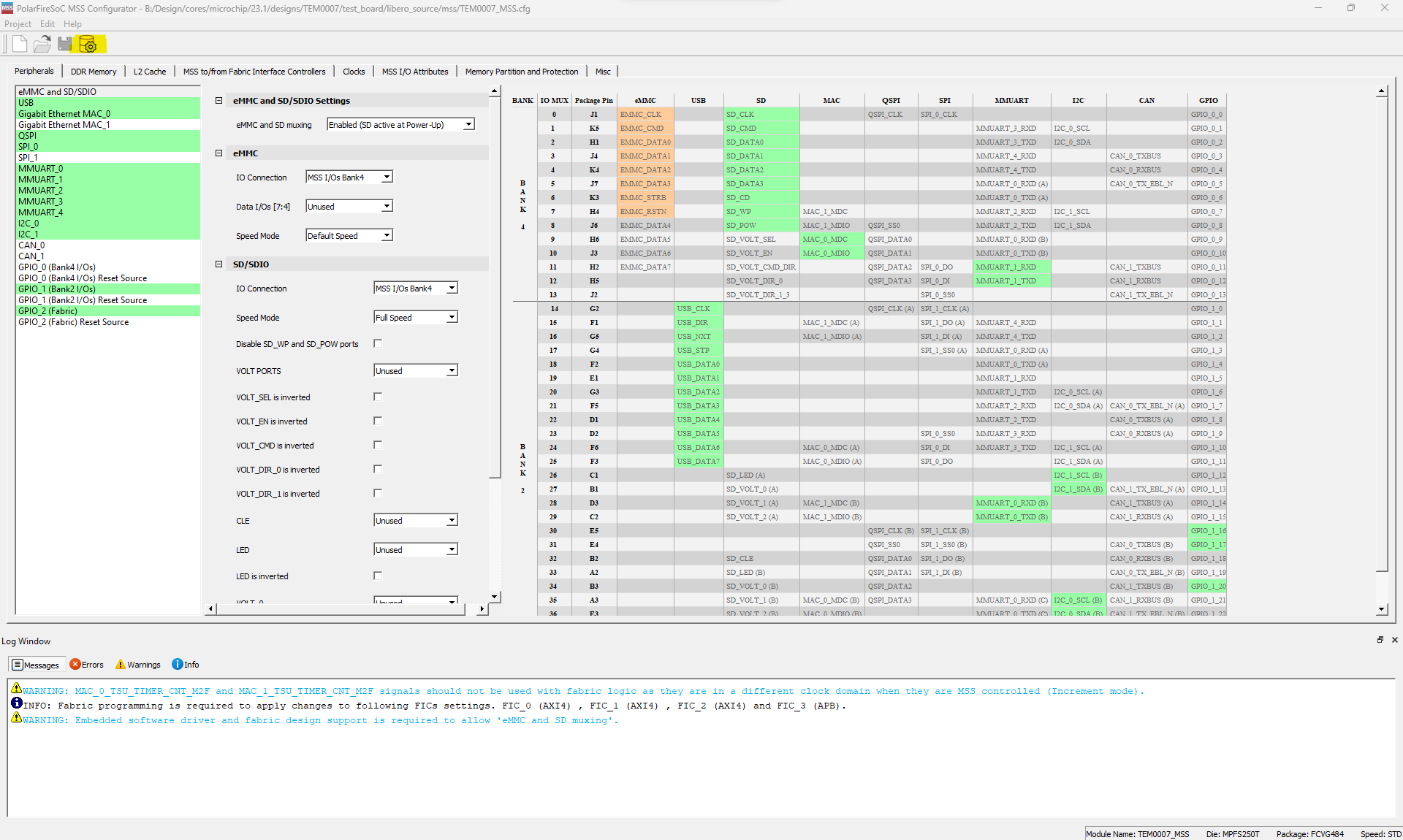

Creating XML file in PolarfireSoC MSS Configurator Software

To create HSS file for a desired module variant the saved MSS configuration xml file in "<softconsole workspace folder>/ hart-software-services-<HSS version>/board/TEM0007/soc_fpgs_design/xml/" must be matched for its related xml file. To do it:

- Open the PolarfireSoC MSS Configurator software.

- Click on Project→Open

- Select the generated TEM0007_MSS.cfg file that is saved in the "<project folder>/prebuilt/mss/<short name of the module variant>" folder.

- Click on Generate icon. It will be opened a window to enter the desired path for generated xml file.

Expand title Creating xml file  Image Added

Image Added - MSS configuration xml file is generated. This file must be imported in SoftConsole software. To import this file copy the generated MSS configuration xml file and replace it with previous xml file in the following path : "<softconsole workspace folder>/ hart-software-services-<HSS version>/boards/TEM0007/soc_fpga_design/xml"

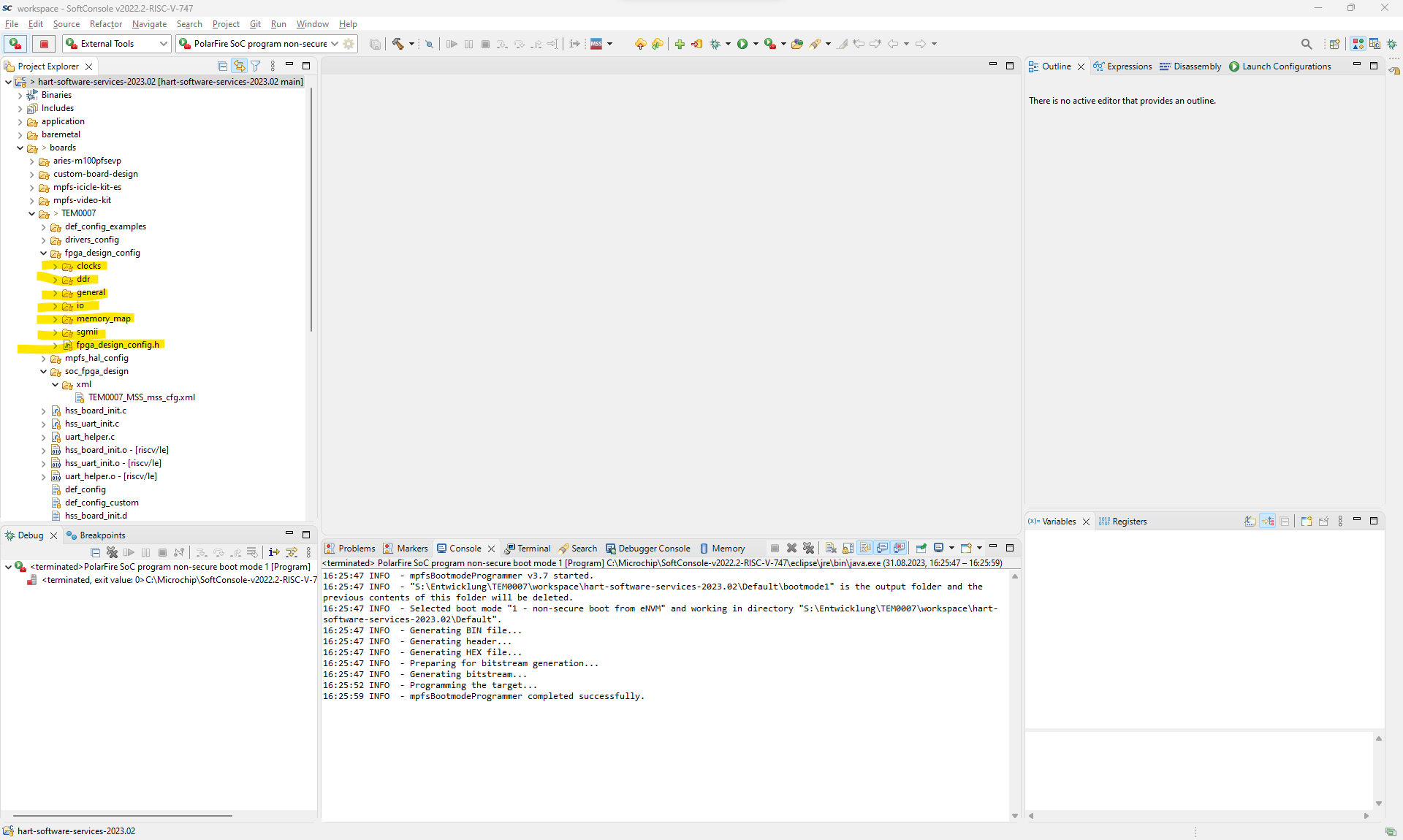

- Right click on the project in SoftConsole software and click on Clean Project.

- In SoftConsole software delete all configuration header files in "<softconsole workspace folder>/ hart-software-services-<HSS version>/boards/TEM0007/fpga_design-config"folder.

Expand title Delete configuration header files  Image Added

Image Added - Right click on the project in SoftConsole software again and click on Build Project to compile the project.

- The new configuration header files will be generated again by the python script in "<softconsole workspace folder>/ hart-software-services-<HSS version>/tools/polarfire-soc-configuration-generator/mpfs_configuration_generator.py "folder. The generated hex file can be found in the "<softconsole workspace folder>/ hart-software-services-<HSS version>/Default " folder.

- This new hex file must be replaced in Libero to generate new Bitstream file, if this hex file should be attached in Bitstream file. See Libero SoC

Note that this hex file can be programmed in eNVM in SoftConsole directly. See Programming eNVM in SoftConsole

Software Design - Yocto

| Scroll Ignore |

|---|

| Page properties | ||||

|---|---|---|---|---|

| ||||

Describe how to generate / compile the Linux distribution . E.g. : |

The host pc must be prepared for using the yocto. For more information about host pc setup for yocto and the required packets please refer to System Requirements

Software Design - Yocto

Trenz electronic has developed his own BSP for Microchip devices same as polarfire soc in Yocto. In the following will be explained the folders in detail.

| meta-trenz-polarfire-bsp Folder | Description | |

|---|---|---|

| recipes-apps* | Contains Consists of start up application for executing of init.sh by booting. More application can be saved in this folder. | |

| recipes-bsp | Contains Consists of uboot necessary required files same as *.bbappend files, device tree and etc. | |

| recipes-core | Contains Consists of *.bb file for Trenz defined image version. In this file are defined necessary This file consists of required packets or files that must be installed in linux. | |

| recipes-kernel | Contains Consists of kernel necessary required files same as *.bbappend files, device tree, config files and etc. | |

| recipes-tools | Contains Consists of a *.bbappend file. | |

| tools | Contains Consists of manifest xml file to define necessary meta data that are required. | |

| wic | Contains *.wks file that decrips disk image properteisConsists of *.wks file that describes disk image properties. |

*Note: In this version is not used.

In the following table exists more information about required packets and supported version.

| Meta data | Supported Version | Description |

|---|---|---|

| meta-riscv | Kirkstone | |

| openembedded-core | Kirkstone | |

| meta-openembedded | Kirkstone | |

| meta-polarfire-soc-yocto-bsp | 2022.11 |

Trenz BSP contains of a shell script. If this shell script in be is executed , all required processes for making a linux image file will be executed automatically. The user needs only to write the generated image file on the SD card. To prepare the image file :

- Create a new folder (for example TEM0007) in host linux ( here Ubuntu18.04 and Ubuntu 20.04 have been tested )

- Download the test board design as zip file (See Download) and save meta-trenz-polarefile-bsp BSP folder from "<project folder>/os/yocto/ " folder in the created folder. (for example TEM0007)

- Go to the created folder (for example TEM0007) that meta-trenz-polarfire-bsp is saved in the host linux and execute its shell script as shown:

*Note: The shell script must be executed in created new folder (for example TEM0007) that has bsp folder saved in it.Expand title Execute shell script Code Block theme Midnight linenumbers true . ./meta-trenz-polarfire-bsp/trenz_polarfire_setup.sh

- After compiling image file *.img and its converted zip file *.zip will be saved in trenz bsp folder:

- " <trenz bsp BSP folder>/prebuilt/boot/yocto/SD_Card.img "

" <trenz

bspBSP folder>/prebuilt/boot/yocto/SD_Card.zip "

- " <trenz bsp BSP folder>/prebuilt/boot/yocto/SD_Card.img "

U-Boot

| Page properties | ||||

|---|---|---|---|---|

| ||||

Please update the listing of ... . |

File location: meta-trenz-<SoC name>-bsp <trenz BSP folder>/recipes-bsp/u-boot/

Changes:

CONFIG_PHY_MARVELL=y

CONFIG_DEFAULT_DEVICE_TREE="tem0007"

CONFIG_DEFAULT_FDT_FILE="tem0007.dtb"

CONFIG_OF_LIST="tem0007"

CONFIG_DM_GPIO=y

CONFIG_CMD_GPIO=y

CONFIG_LOG=y

CONFIG_LOG_MAX_LEVEL=y

CONFIG_LOG_CONSOLE=y

CONFIG_NVMEM=y → to be able to read MAC vom EEPROM

CONFIG_DM_RTC=y

Device Tree

| Page properties | ||||

|---|---|---|---|---|

| ||||

Please insert the Device Tree files into the Codeblocks below . Add or remove Codeblocks if necessary |

U-boot Device Tree

| Code Block | ||||

|---|---|---|---|---|

| ||||

// SPDX-License-Identifier: (GPL-2.0 OR MIT)

/*

* Copyright (C) 2020 Microchip Technology Inc.

* Padmarao Begari <padmarao.begari@microchip.com>

*/

/ {

aliases {

cpu1 = &cpu1;

cpu2 = &cpu2;

cpu3 = &cpu3;

cpu4 = &cpu4;

};

}; |

| Code Block | ||

|---|---|---|

| ||

// SPDX-License-Identifier: (GPL-2.0+ OR MIT)

/*

* Copyright (C) 2021 Microchip Technology Inc.

* Padmarao Begari <padmarao.begari@microchip.com>

*/

/dts-v1/;

#include "microchip-mpfs.dtsi"

#include "dt-bindings/gpio/gpio.h"

/* Clock frequency (in Hz) of the rtcclk */

#define RTCCLK_FREQ 1000000

/ {

model = "Microchip PolarFire-SoC Icicle Kit";

compatible = "microchip,mpfs-icicle-kit", "microchip,mpfs";

aliases {

serial1 = &uart1;

ethernet0 = &mac0;

spi0 = &qspi;

};

chosen {

stdout-path = "serial1";

};

cpus {

timebase-frequency = <RTCCLK_FREQ>;

};

ddrc_cache: memory@80000000 {

device_type = "memory";

reg = <0x0 0x80000000 0x0 0x40000000>;

clocks = <&clkcfg CLK_DDRC>;

status = "okay";

};

usb_phy: usb_phy {

#phy-cells = <0>;

compatible = "usb-nop-xceiv";

reset-gpios = <&gpio1 17 GPIO_ACTIVE_LOW>;

reset-names = "OTG_RST";

};

};

&uart1 {

status = "okay";

};

&mmc {

status = "okay";

bus-width = <4>;

disable-wp;

cap-mmc-highspeed;

cap-sd-highspeed;

cd-debounce-delay-ms;

card-detect-delay = <200>;

// mmc-ddr-1_8v;

// mmc-hs200-1_8v;

sd-uhs-sdr12;

sd-uhs-sdr25;

sd-uhs-sdr50;

sd-uhs-sdr104;

};

&i2c1 {

status = "okay";

#address-cells = <1>;

#size-cells = <0>;

eeprom: eeprom@50 {

compatible = "microchip,24aa025", "atmel,24c02";

//compatible = "atmel,24c02";

reg = <0x50>;

#address-cells = <1>;

#size-cells = <1>;

eth0_addr: eth-mac-addr@FA {

reg = <0xFA 0x06>;

};

};

};

&refclk {

clock-frequency = <125000000>;

};

&mac1 {

status = "disabled";

};

&mac0 {

status = "okay";

phy-mode = "sgmii";

nvmem-cells = <ð0_addr>;

nvmem-cell-names = "mac-address";

phy-handle = <&phy0>;

phy0: ethernet-phy@1 {

device-type = "ethernet-phy";

reg = <1>;

reset-names = "ETH_RST";

reset-gpios = <&gpio1 16 GPIO_ACTIVE_LOW>;

};

};

&qspi {

status = "okay";

num-cs = <1>;

flash0: spi-nor@0 {

compatible = "spi-nor";

reg = <0x0>;

spi-tx-bus-width = <4>;

spi-rx-bus-width = <4>;

spi-max-frequency = <20000000>;

spi-cpol;

spi-cpha;

};

};

&usb {

status = "okay";

dr_mode = "otg";

// dr_mode = "host";

phys = <&usb_phy>;

};

|

Kernel Device Tree

| Code Block | ||||

|---|---|---|---|---|

| ||||

// SPDX-License-Identifier: (GPL-2.0 OR MIT)

/* Copyright (c) 2020-2021 Microchip Technology Inc */

/dts-v1/;

#include "mpfs.dtsi"

#include <dt-bindings/gpio/gpio.h>

#include <dt-bindings/phy/phy.h>

/* Clock frequency (in Hz) of the rtcclk */

#define MTIMER_FREQ 1000000

/ {

#address-cells = <2>;

#size-cells = <2>;

model = "Trenz TEM0007";

compatible = "trenz,tem0007","microchip,mpfs";

aliases {

ethernet0 = &mac0;

serial0 = &mmuart0;

serial1 = &mmuart1;

serial2 = &mmuart2;

serial3 = &mmuart3;

serial4 = &mmuart4;

};

chosen {

stdout-path = "serial1:115200n8";

};

cpus {

timebase-frequency = <MTIMER_FREQ>;

};

//******************************************************//

ddrc_cache: memory@80000000 {

device_type = "memory";

reg = <0x0 0x80000000 0x0 0x40000000>;

status = "okay";

};

reserved-memory {

#address-cells = <2>;

#size-cells = <2>;

ranges;

fabricbuf0ddrc: buffer@A0000000 {

compatible = "shared-dma-pool";

reg = <0x0 0xA0000000 0x0 0x2000000>;

no-map;

};

};

udmabuf0 {

compatible = "ikwzm,u-dma-buf";

device-name = "udmabuf-ddr-c0";

minor-number = <0>;

size = <0x0 0x2000000>;

memory-region = <&fabricbuf0ddrc>;

sync-mode = <3>;

};

//******************************************************//

usb_phy: usb_phy {

#phy-cells = <0>;

compatible = "usb-nop-xceiv";

reset-gpios = <&gpio1 17 GPIO_ACTIVE_LOW>;

reset-names = "OTG_RST";

};

soc {

dma-ranges = <0 0 0 0 0x40 0>;

};

};

&gpio1 {

status = "okay";

};

&gpio2 {

interrupts = <53>, <53>, <53>, <53>,

<53>, <53>, <53>, <53>,

<53>, <53>, <53>, <53>,

<53>, <53>, <53>, <53>,

<53>, <53>, <53>, <53>,

<53>, <53>, <53>, <53>,

<53>, <53>, <53>, <53>,

<53>, <53>, <53>, <53>;

status = "okay";

};

&i2c0 {

status = "okay";

};

&i2c1 {

status = "okay";

#address-cells = <1>;

#size-cells = <0>;

eeprom: eeprom@50 {

compatible = "microchip,24aa025", "atmel,24c02";

//compatible = "atmel,24c02";

reg = <0x50>;

#address-cells = <1>;

#size-cells = <1>;

eth0_addr: eth-mac-addr@FA {

reg = <0xFA 0x06>;

};

};

};

&mac0 {

status = "okay";

phy-mode = "sgmii";

nvmem-cells = <ð0_addr>;

nvmem-cell-names = "mac-address";

phy-handle = <&phy0>;

phy0: ethernet-phy@1 {

device-type = "ethernet-phy";

reg = <1>;

reset-names = "ETH_RST";

reset-gpios = <&gpio1 16 GPIO_ACTIVE_LOW>;

};

};

&mbox {

status = "okay";

};

&mmc {

status = "okay";

bus-width = <4>;

disable-wp;

cap-sd-highspeed;

cap-mmc-highspeed;

// mmc-ddr-1_8v;

// mmc-hs200-1_8v;

sd-uhs-sdr12;

sd-uhs-sdr25;

sd-uhs-sdr50;

sd-uhs-sdr104;

};

&mmuart1 {

status = "okay";

};

&mmuart2 {

status = "okay";

};

&mmuart3 {

status = "okay";

};

&mmuart4 {

status = "okay";

};

&qspi {

status = "okay";

num-cs = <1>;

};

&refclk {

clock-frequency = <125000000>;

};

&spi0 {

status = "okay";

};

&usb {

status = "okay";

dr_mode = "otg";

// dr_mode = "host";

phys = <&usb_phy>;

};

&syscontroller {

status = "okay";

};

|

Kernel

| Page properties | ||||

|---|---|---|---|---|

| ||||

Please update the listing of ... . |

File location: meta-trenz-<SoC name>-bsp <trenz BSP folder>/recipes-kernel/linux/

Changes:

CONFIG_CMDLINE_BOOL=y

CONFIG_CMDLINE="earlycon=sbi root=/dev/mmcblk0p3 rootwait uio_pdrv_genirq.of_id=generic-uio"

CONFIG_EEPROM_AT24=y

CONFIG_NVMEM=y

CONFIG_NVMEM_SYS=y

CONFIG_REGMAP_I2C=y

- CONFIG_MARVELL_PHY=y

CONFIG_LEDS_GPIO=y

CONFIG_LEDS_CLASS=y

CONFIG_NEW_LEDS=y

CONFIG_GPIOLIB=y

CONFIG_USB_MUSB_HOST=y

CONFIG_USB_MUSB_DUAL_ROLE=y

CONFIG_MTD_SPI_NOR_USE_4K_SECTORS=n

CONFIG_MTD_UBI=y

CONFIG_MTD_CMDLINE_PARTS=y

CONFIG_UBIFS_FS=y

CONFIG_MTD_SPI_NOR=y

CONFIG_OF_OVERLAY=y

CONFIG_OF_CONFIGFS=y

CONFIG_MFD_SENSEHAT_CORE=m

CONFIG_INPUT_JOYDEV=m

CONFIG_INPUT_JOYSTICK=y

CONFIG_JOYSTICK_SENSEHAT=m

CONFIG_AUXDISPLAY=y

CONFIG_SENSEHAT_DISPLAY=m

CONFIG_HTS221=m

CONFIG_IIO_ST_PRESS=m

CONFIG_IIO_ST_LSM6DSX=m

CONFIG_IIO_ST_MAGN_3AXIS=m

#CONFIG_MUSB_PIO_ONLY is not set

CONFIG_USB_INVENTRA_DMA=y

Images

| Page properties | ||||

|---|---|---|---|---|

| ||||

Please update the listing of ... . |

Image recipe for minimal console image

File location: meta-trenz-<SoC name>-bsp <trenz BSP folder>/recipes-core/images/

Image recipes:

- te-image-minimal.bb: create minimal linux image

Added packages/recipes:

startup

iputils-ping

expect

rsync

rng-tools

iperf3

devmem2

can-utils

usbutils

pciutils

polarfire-soc-linux-examples

dt-overlay-mchp

libgpiod

libgpiod-tools

libgpiod-dev

i2c-tools

vim vim-vimrc

net-tools

htop

iw

python3

python3-pip

python3-flask

python3-flask-dev

python3-werkzeug

libudev

glib-2.0

sqlite3

dtc

cmake

tar

wget

zip

mtd-utils

mtd-utils-ubifs

Rootfs

| Page properties | ||||

|---|---|---|---|---|

| ||||

Please update the listing of ... . |

Used filesystem: Root file system (RootFS)

Appx. A: Change History and Legal Notices

| Scroll Ignore | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||

Document Change History

To get content of older revision got to "Change History" of this page and select older document revision number.

| Page properties | ||||

|---|---|---|---|---|

| ||||

|

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Legal Notices

| Include Page | ||||

|---|---|---|---|---|

|

| Scroll Only | ||

|---|---|---|

|

| Scroll pdf ignore | ||||||

|---|---|---|---|---|---|---|

|