Page History

...

- SoC/FPGA

- Package: SFVC784

- Device: ZU2 ...ZU5, *

- Engine: EG, CG, EV, *

- Speed: -1, -1L, -2, -2L, 3, *, **

- Temperature: I, E, *, **

- RAM/Storage

- 2x DDR4 SDRAM,

- Data Width: 16 32 Bit

- Size: 8 16 Gb, *

- Speed: 2400 3733 Mbps, ***

- 2x QSPI boot Flash in dual parallel mode

- Data Width: 8 Bit

- Size: 512 Mb Gb, *

- 1x e.MMC Memory

- Data Width: 16 8 Bit

- Size: 8 32 Gb, *

- MAC address serial EEPROM

- 2x DDR4 SDRAM,

- On Board

- Lattice MachXO2 CPLD

- Programmable Clock Generator

- Hi-speed USB2 ULPI Transceiver

- 4x LEDS

- Interface

- 1 1x GB/s serial GMII interface

- 1x Hi-speed USB2 ULPI transceiver with full OTG support

- 34 154 x High Performance (HP) und 96 x High Density PL (HD) I/Os

- 14 78 x PS MIOs (6 of the MIOs intended for SD card interface in default configuration)

- 4 x serial PS GTR transceivers

- PCI Express interface version 2.1 compliant

- SATA 3.1 specification compliant interface

DisplayPort source-only interface with video resolution up to 4k x 2k

- USB 3.0 specification compliant interface implementing a 5 Gbit/s line rate

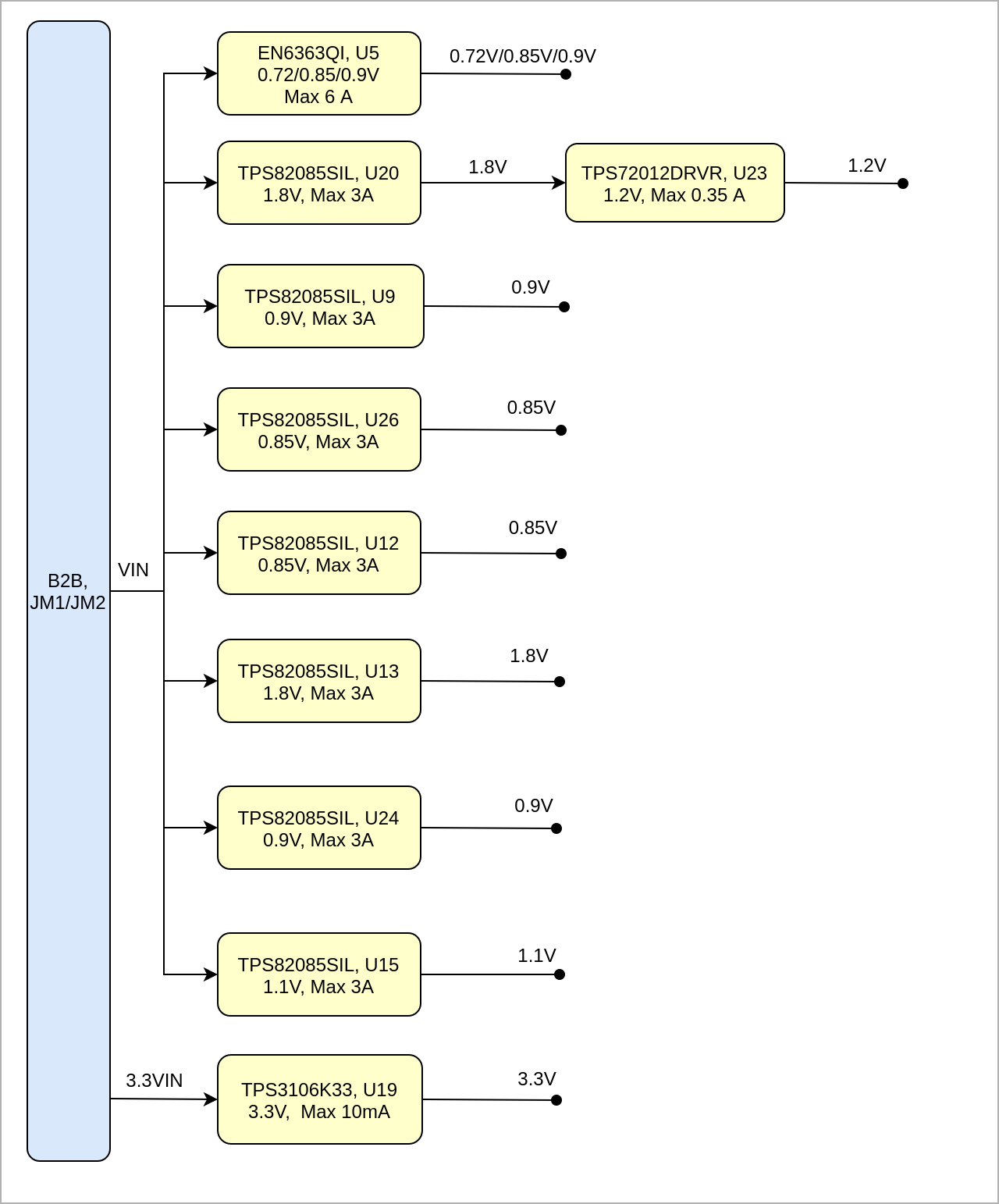

- Power

- All power regulators on board

- Dimension

- 40 x 50 mm

- Note

- * depends on assembly version

- ** also non low power assembly options possible

- *** depends on used U+ Zynq and DDR4 combination

- Rugged for shock and high vibration

- Block Diagram

...

| Scroll Title | ||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||

|

Power-On Sequence

...

Overview

Content Tools