...

Overview

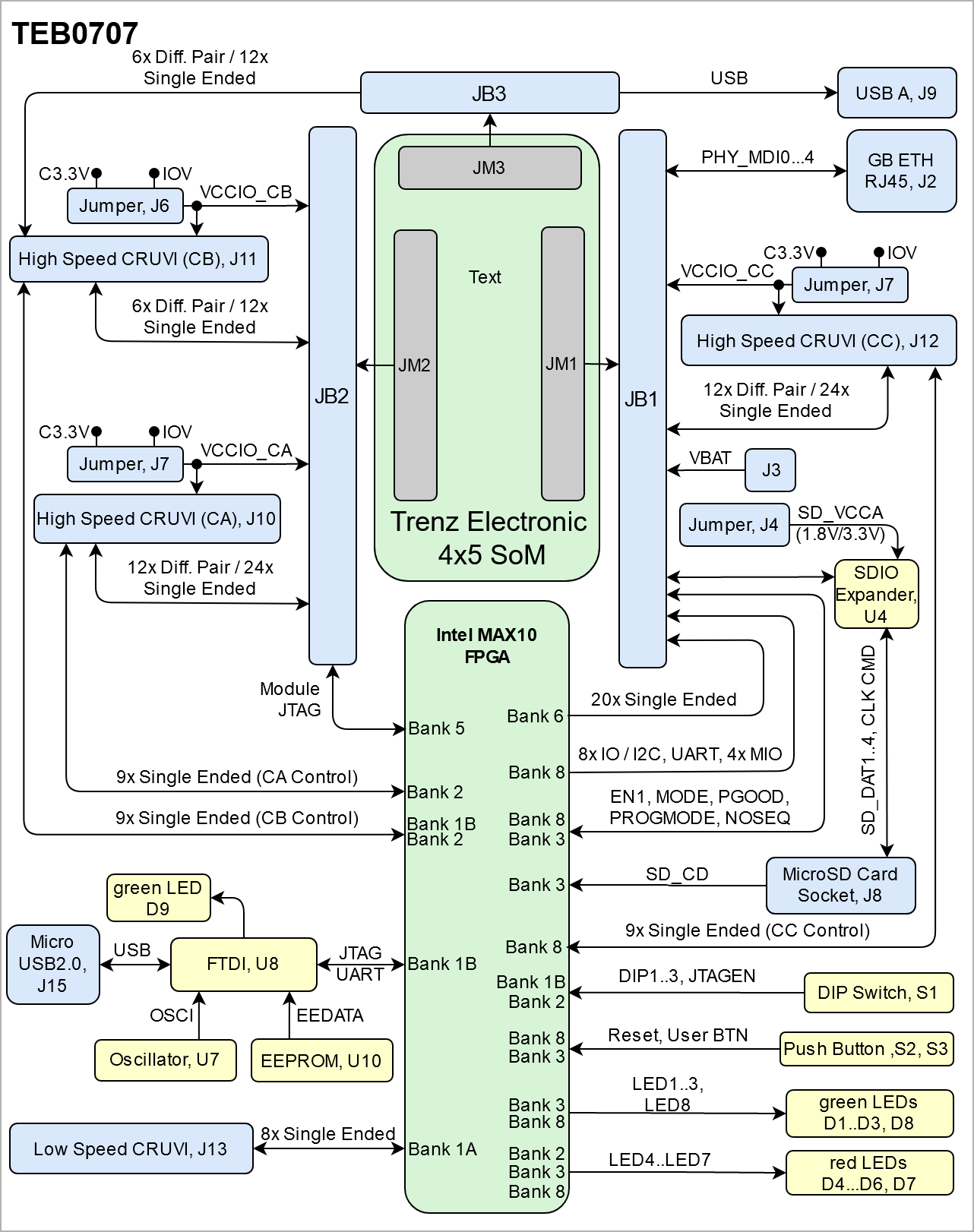

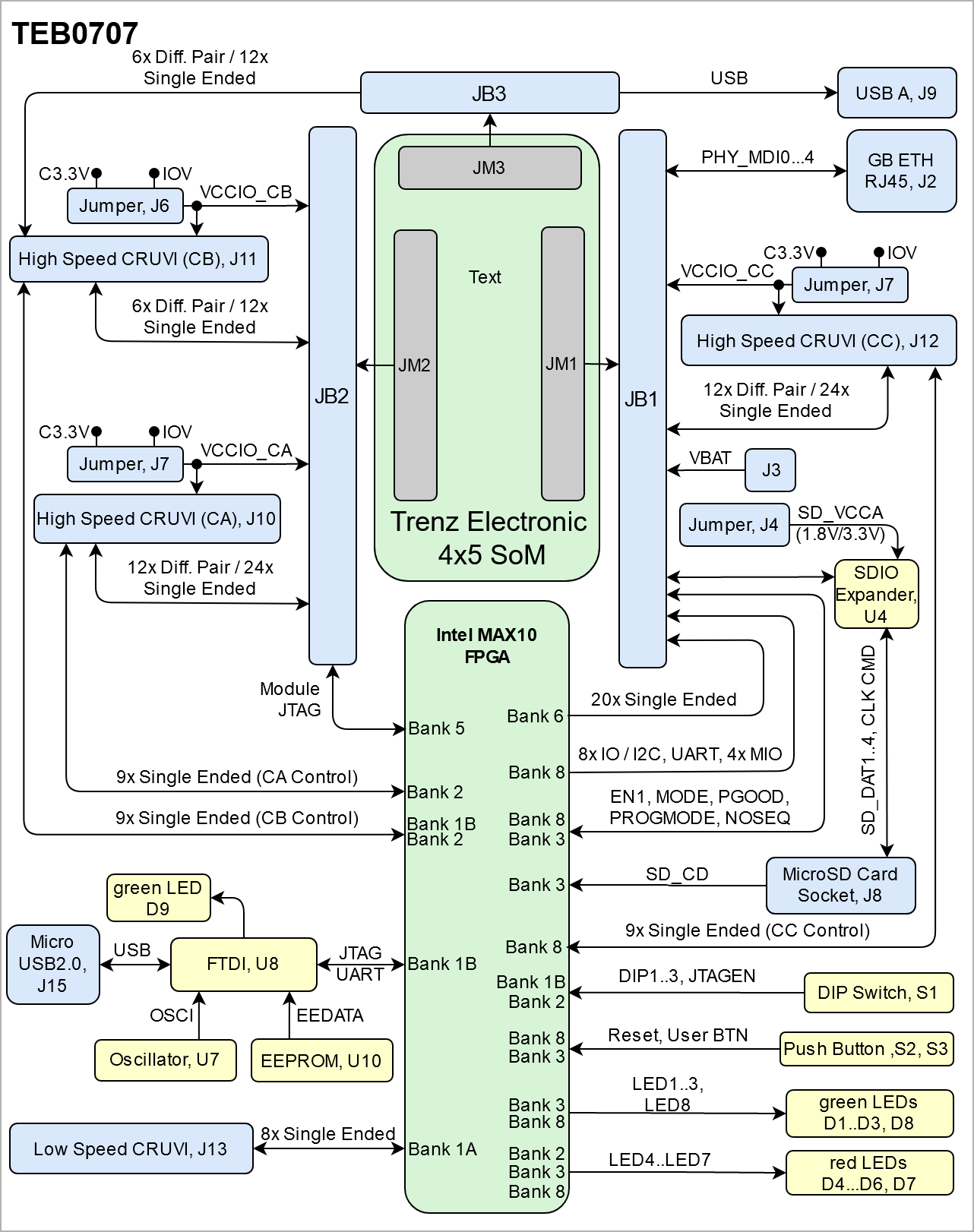

The Trenz Electronic TEM0707 is an industrial-grade module TEB0707 is a carrier for 4 x 5 Trenz Electronic modules. It provides three high speed and one low speed CRUVI extension connectors. For more information, please refer to the CRUVI B2B Connectors. The TEB0707 is integrated with an Intel MAX10 FPGA as system controller and it is equipped with a Micro USB2.0 Socket with FTDI to JTAG/UART solution, RJ45 LAN Socket, Micro USB A Socket, Micro SD Card Socket, Low and High Speed Board to Board Connectors, User LEDs, FTDI, Push Buttons and DIP Switch Switches for controlling the SoM. Furtheremore, the TEB0707 provides CRUVI Extension connectors. For more information, Please refer to the CRUVI B2B Connectors.

Refer to http://trenz.org/teb0707-info for the current online version of this manual and other available documentation.

...

- Modules

- 4x5 Trenz Electronic modules

- RAM/Storage

- EEPROM (FTDI Configuration)

- On Board

- Intel Max 10 FPGA

- FTDI FT2223

- 8x Green 6x User LEDs (3x green, 3x red)

- 2x Status LED

- DIP Switch

- Push Buttons

- Interface

- Gigabit RJ45 LAN socket

- SD Card socket

- Micro USB2.0 Socket

- USB A Socket

- 3x High Speed CRUVI B2B Connectors

- 1x Low Speed CRUVI B2B Connector

- 4x Jumpers

- Power

- Dimension

- Notes

...

| Scroll Title |

|---|

| anchor | Figure_OV_BD |

|---|

| title | TEB0707 block diagram |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| |

|---|

| diagramName | TEB0707_OV_BD |

|---|

| simpleViewer | false |

|---|

| width | 639 |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| diagramWidth | 641 |

|---|

| revision | 1523 |

|---|

|

|

| Scroll Only |

|---|

| |

|

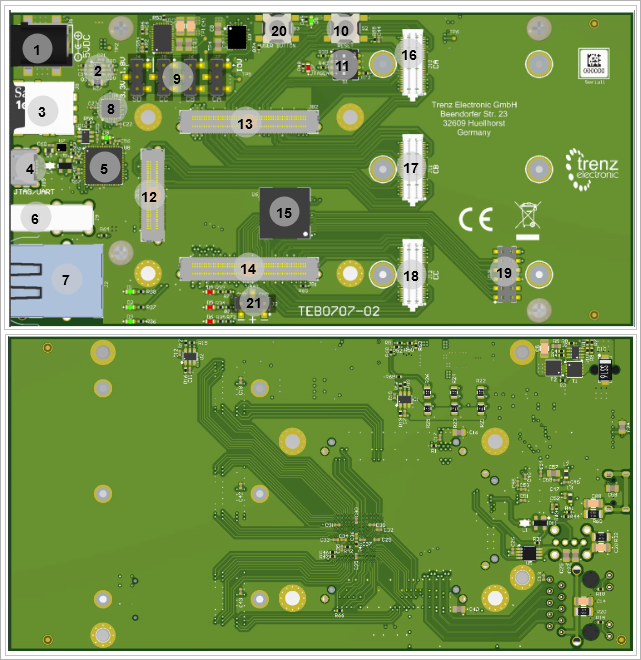

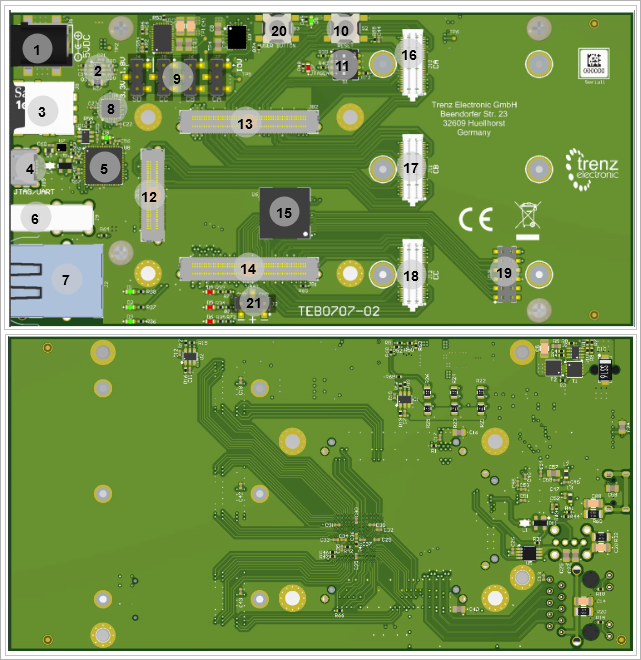

Main Components

| Page properties |

|---|

|

Notes : - Picture of the PCB (top and bottom side) with labels of important components

- Add List below

| Note |

|---|

For more information regarding how to add board photoes, Please refer to "Diagram Drawing Guidline" . | draw.io Diagram |

|---|

| border | false |

|---|

| |

|---|

| diagramName | TEB0707_OV_BD |

|---|

| simpleViewer | false |

|---|

| width | 639 |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| diagramWidth | 641 |

|---|

| revision | 1523 |

|---|

|

|

|

| Scroll Title |

|---|

| anchor | Figure_OV_MC |

|---|

| title | TEB0707 main components |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| |

|---|

| diagramName | TEB0707_OV_MC |

|---|

| simpleViewer | false |

|---|

| width | 639 |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| diagramWidth | 641 |

|---|

| revision | 46 |

|---|

|

|

| Scroll Only |

|---|

|

|

- Barrel Jack Power Supply, J1

- Voltage Regulator, U1

- Micro SD Card Socket, J8

- Micro USB2.0 Socket, J15

- FT2232H FTDI, U8

- USB A Socket, J9

- RJ45 LAN Socket, J2

- SDIO Port Expander, U4

- Jumpers, J4...7

- Push Button (Reset), S2

- DIP Switch, S1

- B2B Connector, JB3

- B2B Connector, JB2

- B2B Connector, JB1

- Intel MAX 10 FPGA, U6

- High speed Speed CRUVI Connector, J10

- High speed Speed CRUVI Connector, J11

- High speed Speed CRUVI Connector, J12

- Low Speed CRUVI Connector, J13

- User Push Button, S3

- JumperPin header, J3

Initial Delivery State

...

| Scroll Title |

|---|

| anchor | Table_OV_BP |

|---|

| title | Boot process. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

MODE Signal State | Boot Mode |

|---|

MODESoM Mode control pin (depnds on SoM | Boot Mode: | | PROGMODE | Programming Mode: - select between CPLD (low, closed, on)

- on SoM or FPGA/SoC (high, open, off )

|

|

...

| Scroll Title |

|---|

| anchor | Table_OV_RST |

|---|

| title | Reset process. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

Signal B2B | Connected to | I/O | Note |

|---|

Reset | Push Button, S2 | RESIN | JB2- 17 | Out | SoM Module Reset signal |

|

Signals, Interfaces and Pins

| Page properties |

|---|

|

Notes : - For carrier or stand-alone boards use subsection for every connector type (add designator on description, not on the subsection title), for example:

- For modules which needs carrier use only classes and refer to B2B connector if more than one is used, for example

|

Board to Board (B2B)

...

Interfaces and Number FPGA bank number and number of I/O signals connected to the B2B connectorconnectors for Trenz 4x5 modules:

| Scroll Title |

|---|

| anchor | Table_SIP_B2B |

|---|

| title | General PL I/O to B2B connectors information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| B2B Connector | Interface | I/O Signal Count | Connected to | Notes |

|---|

|

CRUVI B2B Connectors

The TEMB0707 is equipped with a Low Speed Connectors J 13 and three High Speed Connector J10...12. These connectors are provided for CRUVI extension cards. More information is provided in the B2B Connectors section.

...

| anchor | Table_SIP_CRUVIB2B |

|---|

| title | CRUVI B2B connectors information |

|---|

...

SMB_ALERT

SMB_SDA

SMB_SCL

...

JB1

| Ethernet LAN | 4x Diff pairs | RJ45 Socket, J2 |

| | SD Card | 6 x Single Ended | IO Expander, U4 |

| | I/Os | 20x Single Ended | MAX10 FPGA Bank 6, U6 |

| | CRUVI | 12x Diff pairs/24x Single ended 4x Single Ended | High Speed CRUVI, J12 | CRUVI C | | SoM Control Signals | 5x Single Ended | MAX10 FPGA, U6 |

| | I/Os | 8x Single ended | MAX10 FPGA Bank 8, U6 |

| JB2

| CRUVI | 12x Diff pairs/24x Single ended 4x Single Ended | High Speed CRUVI, J10 | CRUVI A | | CRUVI | 6x Diff pairs/12x Single ended | High Speed CRUVI, J11 | CRUVI B | | JTAG | 4x Single Ended | FPGA Bank 5, U6 |

| | JB3 | CRUVI | 6x Diff pairs/12x Single ended 4x Single Ended | High Speed CRUVI, J11 | CRUVI B | | USB | 1x Diff pair, 2x Single Ended | USB A, J9 |

|

|

CRUVI B2B Connectors

The TEMB0707 is equipped with a Low Speed Connectors J 13 and three High Speed Connector J10...12. These connectors are provided for CRUVI extension cards. More information is provided in the B2B Connectors section.

| Scroll Title |

|---|

| anchor | Table_SIP_CRUVIB2B |

|---|

| title | CRUVI B2B connectors information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Speed | Designators | Schematic | Connected to | Notes |

|---|

| High

| CRUVI C, J12 | A0...A5 (N/P) | B2B, JB1 |

| | B0...B5 (N/P) | B2B, JB1 |

| | MODE, REFCLK, SMB_ALERT, SMB_SDA, SMB_SCL, SEL, DO, DI, SCK | MAX10 FPGA Bank 8, U6 | 3.3V User IOs (Max10 Firmware dependent) | | HSIO, HI, HO, RESET | B2B, JB1 |

| | High

| CRUVI B, J11 | A0...A5 (N/P) | B2B, JB1 |

| | B0...B5 (N/P) | B2B, JB1 |

| | MODE, REFCLK, SMB_ALERT, SMB_SDA, SMB_SCL, SEL, DO, DI, SCK | MAX10 FPGA Bank 2/3, U6 | 3.3V User IOs (Max10 Firmware dependent) | | HSIO, HSI, HSO, RESET | B2B, JB3 |

| | High

| CRUVI A, J13

| A0...A5 (N/P) | B2B, JB2 |

| | B0...B5 (N/P) | B2B, JB2 |

| MODE, REFCLK, SMB_ALERT, SMB_SDA, SMB_SCL, SEL, DO, DI, SCK | MAX10 FPGA Bank 2/3, U6 | 3.3V User IOs (Max10 Firmware dependent) | | HSIO, HSI, HSO, RESET | B2B, JB2 |

| | Low | CRUVI | X0...X7 | MAX10 FPGA Bank 1A, U6 |

|

|

JTAG Interface

JTAG signals form FTDI U8 are routed to MAX10 CPLD. Via dip setting JTAG of MAX10 or JTAG of the connected Trenz 4x5 module can be selected. Forwarding signals to SoM is MAX10 Firmware dependent

...

JTAG access to the attached SoM through B2B connector JB2. The JTAG Enable is connected to VCC and after power on it will be enable.

...

| anchor | Table_SIP_MJTG |

|---|

| title | JTAG pins connection |

|---|

...

JTAG Signal

...

B2B Connector

...

JB2-98

...

There is an Intel MAX10 provided on TEB0707 as CPLD and JTAG access to the Intel MAX10 SoC is provided through the FTDI U8.

| Scroll Title |

|---|

| anchor | Table_SIP_MJTG |

|---|

| title | JTAG pins connection |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

JTAG Signal | MAX10 Pin Bank 1B, U6 | Connected to |

|---|

| M_TMS | G1 | FTDI (U8) - ADBUS3 | | M_TDI | F5 | FTDI (U8) - ADBUS1 | | M_TDO | F6 | FTDI (U8) - ADBUS2 | | M_TCK | G2 | FTDI (U8) - ADBUS0 |

|

Micro USB2.0

JTAG access to the Trenz 4x5 module is through B2B connector JB2There is a USB2.0 Socket, J15 provided in order to communicate with the FTDI, U8. Data signals from USB2.0 are passed through a Line Filter L4 and a Diode U9 in order to be protected against inverse polarity connection.

| Scroll Title |

|---|

| anchor | Table_SIP_USB2MJTG |

|---|

| title | USB2.0 Socket informationJTAG pins connection |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

|

| Pin | Schematic | Connected to | Notes |

|---|

ID | N.C | N.C | | D+ | USB_P | FTDI, U8 | Through Line Filter, L4 |

| D- | USB_N | FTDI, U8 | Through Line Filter, L4 |

Vbus | VBUS | Diode, U9 |

Micro USB A

JTAG Signal | MAX10 Pin Bank5, U6 | B2B Connector |

|---|

| M_TMS | L12 | JB2-94 | | M_TDI | L13 | JB2-96 | | M_TDO | J10 | JB2-100 | | M_TCK | H8 | JB2-98 | | VCCJTAG | J11, J12 | JB2-92 |

|

SD Card socket

The TEB0707 is equipped with an Micro SD Card slot, J8. For levelshifting an IO Expander (U4) is used.

| Scroll Title |

|---|

|

| Scroll Title |

|---|

| anchor | Table_SIP_USBA |

|---|

| title | USB2.0 Socket information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Pin | Schematic | Connected to | Notes | ID | N.C | N.C |

|---|

| D+ | DL_P | FTDI, U1 | Through Line Filter, L1 | | D- | DL_N | FTDI, U1 | Through Line Filter, L1 | Vbus | VBUS | Diode, U2 |

|

RJ45 LAN Socket

| DAT0...3 | ESD_DAT0...3 | B2B, JB1 | Through IO Expander, U4 | | CMD | ESD_CMD | B2B, JB1 | Through IO Expander, U4 | | VDD | 3.3V_SD | B2B, JB1 | Through IO Expander, U4 | | CLK | ESD_CLK | B2B, JB1 | Through IO Expander, U4 | | DLT | SD_CD | FPGA Bank 3, U6 | Card detect. |

|

Micro USB2.0 Socket

There is a micro USB2.0 Socket, J15 provided in order to communicate with the FTDI, U8There is a RJ45 Ethernet LAN Socket, J2 connected to B2B, JB1 via 4x channels data receive and transmit.

| Scroll Title |

|---|

| anchor | Table_SIP_ETHUSB2 |

|---|

| title | RJ45 LAN Micro USB2.0 Socket information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Pin | Schematic | Connected to | Notes |

|---|

2 | PHY_MDI0_ JB13 | PHY_MDI0_N | B2B, JB1 | | JB3 | Through Line Filter, L4 | | D- | O2-D_ |

4 | PHY_MDI1_P | B2B, JB1 | 5 | PHY_MDI1_ JB16 | PHY_MDI2_P | B2B, JB1 | 7 | PHY_MDI2_N| JB3 | Through Line Filter, L4 | | Vbus | VBUS | B2B, |

JB18 | PHY_MDI3_P | B2B, JB1 | 9 | PHY_MDI3_N | B2B, JB1 | VCC | ETH-VCC | B2B, JB1 | | Green LED | ETH1_LED0 | Intel MAX 10, U6 | Link/Activity indicator | | Yellow LED | ETH1_LED1 | Intel MAX 10, U6 | Speed indicator | |

Test Points

...

you must fill the table below with group of Test Point which are indicated as TP in a schematic. If there is no Test Point remarked in the schematic, delet the Test Point section.

Example:

USB A Socket

The SoM USB 2.0 signals are routed to a USB A socket (host).

| Scroll Title |

|---|

| anchor | Table_SIP_USBA |

|---|

| title | USB A Socket information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Pin | Schematic | Connected to | Notes |

|---|

| Data+ | O2-D_P | B2B, JB3 | Through Line Filter, L1 | | Data- | O2-D_N | B2B, JB3 | Through Line Filter, L1 | | VCC | USB_VBUS | B2B, JB3 |

|

|

RJ45 LAN Socket

There is a RJ45 Ethernet LAN MagJack, J2 connected to B2B, JB1.

...

| Scroll Title |

|---|

| anchor | Table_SIP_TPsETH |

|---|

| title | Test Points InformationRJ45 LAN Socket information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

Test PointSignal| Schematic | Connected to | Notes |

|---|

TP1 | 3.3V | Regulator, U1 | TP2 | VIN | Voltage Protection, U2 | TP4 | IOV | Regulator, U3 | TP5 | 3.3V | Power Switch, Q1 | TP6 | C5VIN | Power Switch, Q2 | |

On-board Peripherals

| Page properties |

|---|

|

Notes : - add subsection for every component which is important for design, for example:

- Two 100 Mbit Ethernet Transciever PHY

- USB PHY

- Programmable Clock Generator

- Oscillators

- eMMCs

- RTC

- FTDI

- ...

- DIP-Switches

- Buttons

- LEDs

|

| Page properties |

|---|

|

Notes : In the on-board peripheral table "chip/Interface" must be linked to the corresponding chapter or subsection |

| 2 | PHY_MDI0_P | B2B, JB1 |

| | 3 | PHY_MDI0_N | B2B, JB1 |

| | 4 | PHY_MDI1_P | B2B, JB1 |

| | 5 | PHY_MDI1_N | B2B, JB1 |

| | 6 | PHY_MDI2_P | B2B, JB1 |

| | 7 | PHY_MDI2_N | B2B, JB1 |

| | 8 | PHY_MDI3_P | B2B, JB1 |

| | 9 | PHY_MDI3_N | B2B, JB1 |

| | VCC | ETH-VCC | B2B, JB1 |

| | Green LED | ETH1_LED0 | Intel MAX 10, U6 | MAX10 Firmware dependent | | Yellow LED | ETH1_LED1 | Intel MAX 10, U6 | MAX10 Firmware dependent |

|

Jumpers

There are three Jumpers provided to choose the CRUVI Extension power voltage.

| Scroll Title |

|---|

| anchor | Table_SIP_Jumpers |

|---|

| title | Jumpers information |

|---|

|

| Scroll Title |

|---|

| anchor | Table_OBP |

|---|

| title | On board peripherals |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

Chip/Interface| Notes | Intel MAX 10 | U6 | FTDI | U8 | SDIO Expander | U4 | EEPROM | U10 | Oscillator | U7 | LEDs | D1...8 | |

Quad SPI Flash Memory

...

Notes :

...

| Schematic | Connected to | Notes |

|---|

| J14 | VCCIO_CC | B2B, JB2 | CRUVI C | | J16 | VCCIO_CB | B2B, JB2 | CRUVI B | | J17 | VCCIO_CA | B2B, JB2 | CRUVI A |

|

| Scroll Title |

|---|

| anchor | Table_OBPSIP_SPISMD |

|---|

| title | Quad SPI interface MIOs and pinsJumpers information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

|

...

Test Points

| Page properties |

|---|

|

you must fill the table below with group of Test Point which are indicated as TP in a schematic. If there is no Test Point remarked in the schematic, delet the Test Point section. Example: | Test Point | Signal | B2B | Notes |

|---|

| 10 | PWR_PL_OK | J2-120 |

|

|

| Scroll Title |

|---|

| anchor | Table_SIP_TPs |

|---|

| title | Test Points Information |

|---|

|

| Scroll Title |

|---|

| anchor | Table_OBP_EEP |

|---|

| title | I2C EEPROM interface MIOs and pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

style | widths | | sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

| MIO Pin | Schematic | U?? Pin | Notes |

|---|

| Scroll Title |

|---|

| anchor | Table_OBP_I2C_EEPROM |

|---|

| title | I2C address for EEPROM |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Test Point | Signal | Connected to |

|---|

MIO Pin | I2C Address | Designator |

LEDs

...

| anchor | Table_OBP_LED |

|---|

| title | On-board LEDs |

|---|

| TP1 | 3.3V | Regulator, U1 |

| | TP2 | VIN | Voltage Protection, U2 |

| | TP4 | IOV | Regulator, U3 |

| | TP5 | 3.3V | Power Switch, Q1 |

| | TP6 | C5VIN | Power Switch, Q2 |

|

|

On-board Peripherals

| Page properties |

|---|

|

Notes : - add subsection for every component which is important for design, for example:

- Two 100 Mbit Ethernet Transciever PHY

- USB PHY

- Programmable Clock Generator

- Oscillators

- eMMCs

- RTC

- FTDI

- ...

- DIP-Switches

- Buttons

- LEDs

|

| Page properties |

|---|

|

Notes : In the on-board peripheral table "chip/Interface" must be linked to the corresponding chapter or subsection |

| Scroll Title |

|---|

| anchor | Table_OBP |

|---|

| title | On board peripherals |

|---|

|

...

EEPROM

| Scroll Title |

|---|

| anchor | Table_OBP_EEP |

|---|

| title | I2C EEPROM interface MIOs and pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

PinSchematic| Connected to | CSEECS, CLKEECLK U8DIN | EEDATA | FTDI, U8 | |

| Scroll Title |

|---|

| anchor | Table_OBP_I2C_EEPROM |

|---|

| title | I2C address for EEPROM |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

style | widths | | sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

| I2C Address | Designator | Notes |

|---|

A0 | U15 |

Ethernet

Intel Max10 CPLD

The TEB0707 is quipped with an Intel Max10 as CPLD used for levelshifting of 3.3V signals on CRUVI connectors, JTAG/UART forward to modules, Module control pis, power sequencing and IO voltage selection along with providing User Push buttons, LEDs and switches. For complete information, please see the TEB0707 MAX10 CPLD.

FTDI FT2232H

The FTDI chip (U8) converts signals from USB2 to variety of standard serial and parallel interfaces. Refer to the FTDI data sheet to get information about the capacity of the FT2232H chip which is used in Multi-Protocol Synchronous Serial Engine (MPPSE) mode for JTAG.

The configuration of FTDI FT2232H chip is pre-programmed on the EEPROM U10.

| Scroll Title |

|---|

| anchor | Table_OBP_FT2232H |

|---|

| title | FTDI chip interfaces and pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Pin | Schematic | Connected to | Notes |

|---|

| ADBUS0 | TCK | FPGA Bank 1B, U6 | JTAG interface | | ADBUS1 | TDI | FPGA Bank 1B, U6 | | ADBUS2 | TDO | FPGA Bank 1B, U6 | | ADBUS3 | TMS | FPGA Bank 1B, U6 | | BDBUS0 | F_UART_TX | FPGA Bank 1B, U6 | UART Transmitter output | | BDBUS1 | F_UART_RX | FPGA Bank 1B, U6 | UART Receiver Input | | OSCI | OSCI | Oscillator, U7 | Clock 12 MHz | | EECS | EECS | EEPROM, U10 | EEPROM Contains FTDI configuration | | EECLK | EECLK | EEPROM, U10 | | EEDATA | EEDATA | EEPROM, U10 | | DM/DP | FD_N/ FD_P | Micro USB, J15 | USB to UART | | nRESET | 3.3V | 3.3V |

|

|

LEDs

The functions of the LEDs are MAX10 Firmware dependent. See TEB0707 MAX10 CPLD LEDs.

| Scroll Title |

|---|

| anchor | Table_OBP_LED |

|---|

| title | On-board LEDs |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Designator | Color | Schematic | Connected to | Active Level | Note |

|---|

| D1 | green | LED3 | FPGA Bank 8 | Active High |

| | D2 | green | LED5 | FPGA Bank 8 | Active High |

| | D3 | green | LED7 | FPGA Bank 8 | Active High |

| | D4 | red | LED4 | FPGA Bank 3 | Active High |

| | D5 | red | LED6 | FPGA Bank 2 | Active High |

| | D6 | red | LED8 | FPGA Bank 8 | Active High |

| | D7 | red | LED2 | FPGA Bank 3 | Active High |

| | D8 | green | LED1 | FPGA Bank 3 | Active High |

|

|

EEPROM

The EEPROM IC, U8 contains the FTDI configuration and is prprogrammed with Xilinx JTAG licence.

| Scroll Title |

|---|

| anchor | Table_OBP_EEP |

|---|

| title | I2C EEPROM interface MIOs and pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Pin | Schematic | Connected to | Notes |

|---|

| CS | EECS | FTDI, U8 |

| | CLK | EECLK | FTDI, U8 |

| | DIN | EEDATA | FTDI, U8 |

|

|

DIP Switch

There is a DIP Switch provided for user controlling of settings. Dip1..3 are connected to MAX10 CPLD and therefore function is Firmware dependent, see TEB0707 MAX10 Dips.

| Scroll Title |

|---|

| anchor | Table_OBP_DIP |

|---|

| title | DIP Switch connections |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Pin | Schematic | Function (in standard Firmware) | Notes |

|---|

| DIP1 | DIP1 | Forwarded to IO so SoM | MAX10 firmware dependent. | | DIP2 | DIP2 | IO Voltage selection | 1.8V ('high', open, OFF), 2.5V ('low', closed, ON) | | DIP3 | DIP3 (PROGMODE) | Programming mode (JTAG selection on Trenz 4x5 module) | Select between FPGA/SoC (high, open, OFF ) or CPLD (low, closed, ON), MAX10 firmware dependent.

| | DIP4 | JTAGEN | JTAG Selection | JTAG mode between CPLD (high, closed, ON) or SoM (low, open, OFF) |

|

Push Buttons

Buttons are connected MAX10 CPLD and therefore function is Firmware dependent, see TEB0707 MAX10 CPLD Buttons

| Scroll Title |

|---|

| anchor | Table_OBP_ETHBTN |

|---|

| title | Ethernet PHY to Zynq SoC connectionsPush Buttons informations |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

|

| U?? Pin | Signal Name | Connected to | Signal Description | Note |

|---|

Clock Sources

...

| anchor | Table_OBP_CLK |

|---|

| title | Osillators |

|---|

| Designator | Schematic | Function (in standard Firmware) | Notes |

|---|

| S2 | RESET | SoM Reset | Hardware debounced. | | S3 | BUTTON1 | User Button | debounced in Max10 FPGA |

|

Clock Sources

MEMS U7 Oscillator is nedded for FTDI. It is additionally connectd to MAX 10 FPGA Bank 2 Pin H4 and can be used in custom Firmware

...

Programmable Clock Generator

There is a programmable clock generator on-board (U??) provided in order to generate variable clocks for the module. Programming can be done using I2C via PIN header J??. The I2C Address is 0x??.

| Scroll Title |

|---|

| anchor | Table_OBP_PCLKCLK |

|---|

| title | Programmable Clock Generator Inputs and OutputsOsillators |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Designator | Description | Frequency |

|---|

U?? Pin

| Signal | Connected to | DirectionIN0IN1 | IN2 | IN3 | XAXB | SCLK | SDA | OUT0 | OUT1 | OUT2 | OUT3 | OUT4 | OUT5 | OUT6 | OUT7 | OUT8/OUT9 |

|

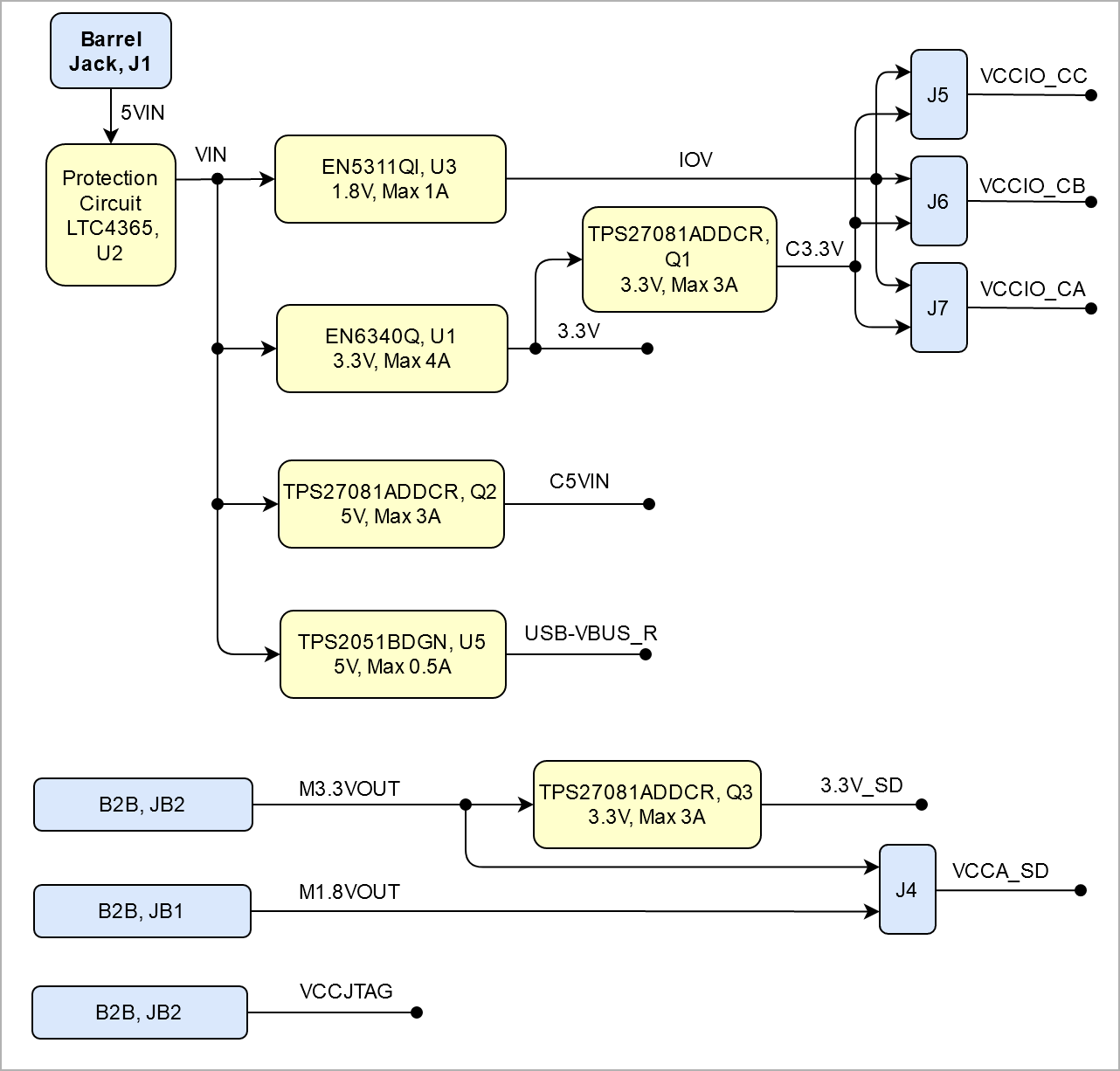

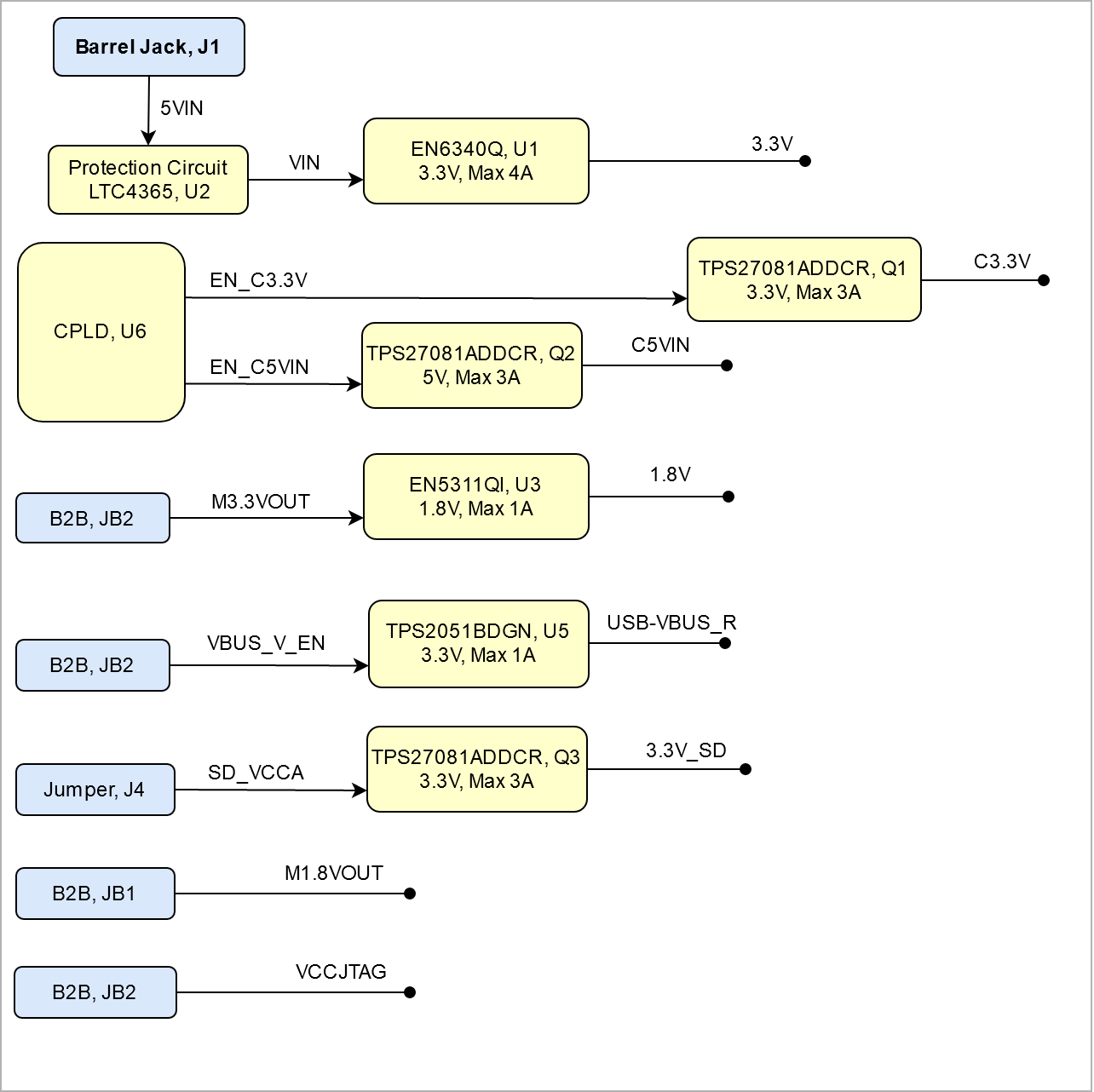

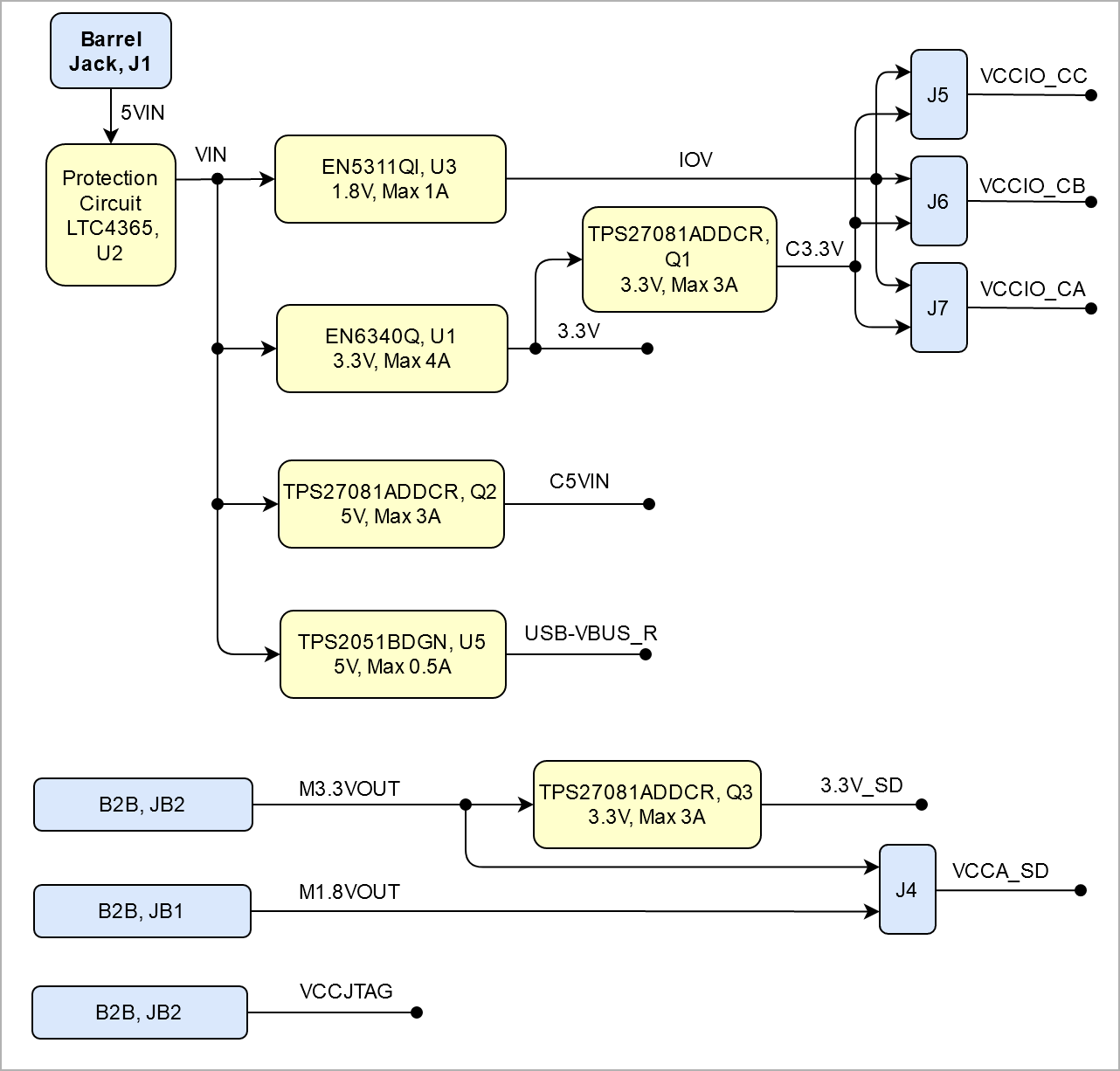

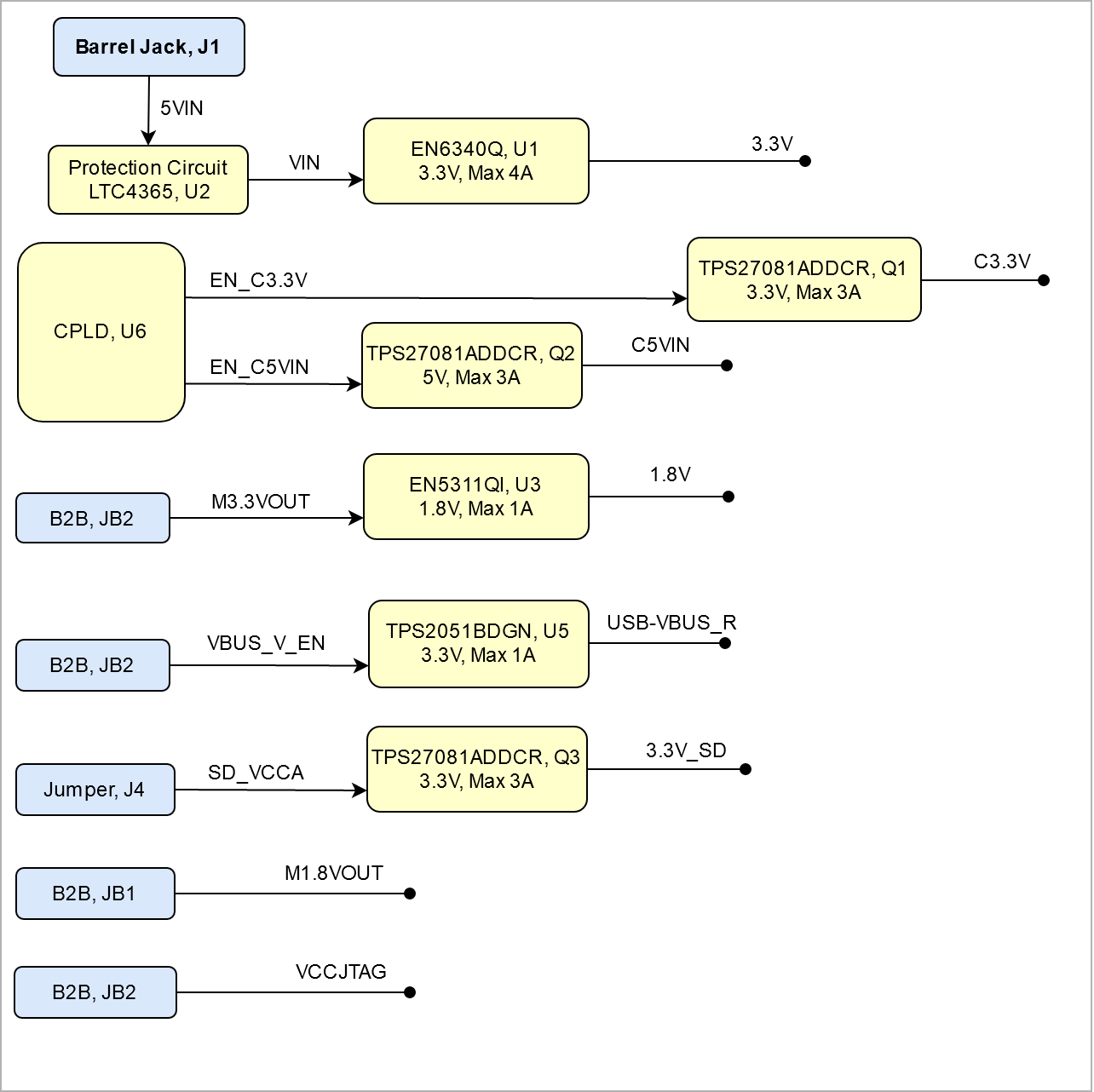

Power and Power-On Sequence

| Page properties |

|---|

|

In 'Power and Power-on Sequence' section there are three important digrams which must be drawn: - |Power on-sequence

- Power distribution

- Voltage monitoring circuit

|

...

Power supply with minimum current capability of xx 3 A for system startup is recommended.

...

| Scroll Title |

|---|

| anchor | Figure_PWR_PD |

|---|

| title | Power Distribution |

|---|

| scroll-ignore |

| draw.io Diagram |

|---|

| border | false |

|---|

| |

|---|

| diagramName | TEB0707_PWR_ |

|---|

|

PD| DP | | simpleViewer | false |

|---|

| width | 639 |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| diagramWidth | 641 |

|---|

| revision |

|---|

|

2

| Scroll Only |

|---|

Image Removed Image Removed Image Added Image Added

|

|

Power-On Sequence

| Scroll Title |

|---|

| anchor | Figure_PWR_PS |

|---|

| title | Power Sequency |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| |

|---|

| diagramName | TEB0707_PWR_PS |

|---|

| simpleViewer | false |

|---|

| width | 639 |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| diagramWidth | 641 |

|---|

| revision | 14 |

|---|

|

|

| Scroll Only |

|---|

|

|

Voltage Monitor Circuit

...

| anchor | Figure_PWR_VMC |

|---|

| title | Voltage Monitor Circuit |

|---|

| Scroll Ignore |

|---|

Create DrawIO object here: Attention if you copy from other page, objects are only linked. |

| Scroll Only |

|---|

image link to the generate DrawIO PNG file of this page. This is a workaround until scroll pdf export bug is fixed |

Power Rails

| Scroll Title |

|---|

| anchor | Table_PWR_PR |

|---|

| title | Module power rails. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Power Rail Name | B2B Connector JB1 Pin | B2B Connector JB2 Pin | B2B Connector JB3 Pin | Direction | Notes |

|---|

| VCCIO_CA | - | 8, 10 | - | Output |

| | VCCIO_CB | - | 2, 4, 6 | - | Output |

| | VCCIO_CC | 10, 12 | - | - | Output |

| 3.3V | 14, 16 | - | - | Output |

| | M1.8VOUT | 40 | - | - | Input |

| | M3.3VOUT | - | 9, 11 | - | Input |

| | ETH-VCC | 13 | - | - | Input |

|

|

Bank Voltages

Below MAX10 CPLD Bankvoltages are summarized.

Power Rails

...

| anchor | Table_PWR_PR |

|---|

| title | Module power rails. |

|---|

...

B2B Connector

JM1 Pin

...

B2B Connector

JM2 Pin

...

B2B Connector

JM3 Pin

...

Bank Voltages

| Scroll Title |

|---|

| anchor | Table_PWR_BV |

|---|

| title | Zynq SoC bank voltages. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Schematic Name | | Notes | Notes |

|---|

| Bank 1A | 3.3V | 3.3V |

| | Bank 1B | 3.3V | 3.3V |

| | Bank 2 | 3.3V | 3.3V |

| | Bank 3 | 3.3V | 3.3V |

| | Bank 5 | VCCJTAG |

| from SoM | | Bank 6 | VCCIO_CC |

| Variable | | Bank 8 | 3.3V | 3.3V |

|

|

Board to Board Connectors

| Page properties |

|---|

|

- This section is optional and only for modules.

use "include page" macro and link to the general B2B connector page of the module series, For example: 6 x 6 SoM LSHM B2B Connectors

| Include Page |

|---|

| PD:6 x 6 SoM LSHM B2B ConnectorsPD: |

|---|

| 6 x 6 SoM LSHM B2B Connectors |

|---|

|

|

| Include Page |

|---|

| PD:4 x 5 SoM LSHM B2B ConnectorsPD: |

|---|

| 4 x 5 SoM LSHM B2B Connectors |

|---|

|

CRUVI Connectors

| Include Page |

|---|

| CRUVI B2B Connectors |

|---|

| CRUVI B2B Connectors |

|---|

|

Technical Specifications

...

| Scroll Title |

|---|

| anchor | Table_TS_AMR |

|---|

| title | PS absolute maximum ratings |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Symbols | Description | Min | Max | Unit |

|---|

| 5VIN | Input supply Voltage | -40 | 60 | V | | T_STG | Storage Temperature | -40 | 85 | °C |

|

Recommended Operating Conditions

...

| Scroll Title |

|---|

| anchor | Table_TS_ROC |

|---|

| title | Recommended operating conditions. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Parameter | Min | Max | Units | Reference Document |

|---|

| Input supply Voltage | 4.06 | 5.58 | V | See ???? the OV/UV in the carrier datasheets. | | T_OPT | 0 | 70 | °C | See Push Button | °C | See Xilinx ???? datasheet. |

|

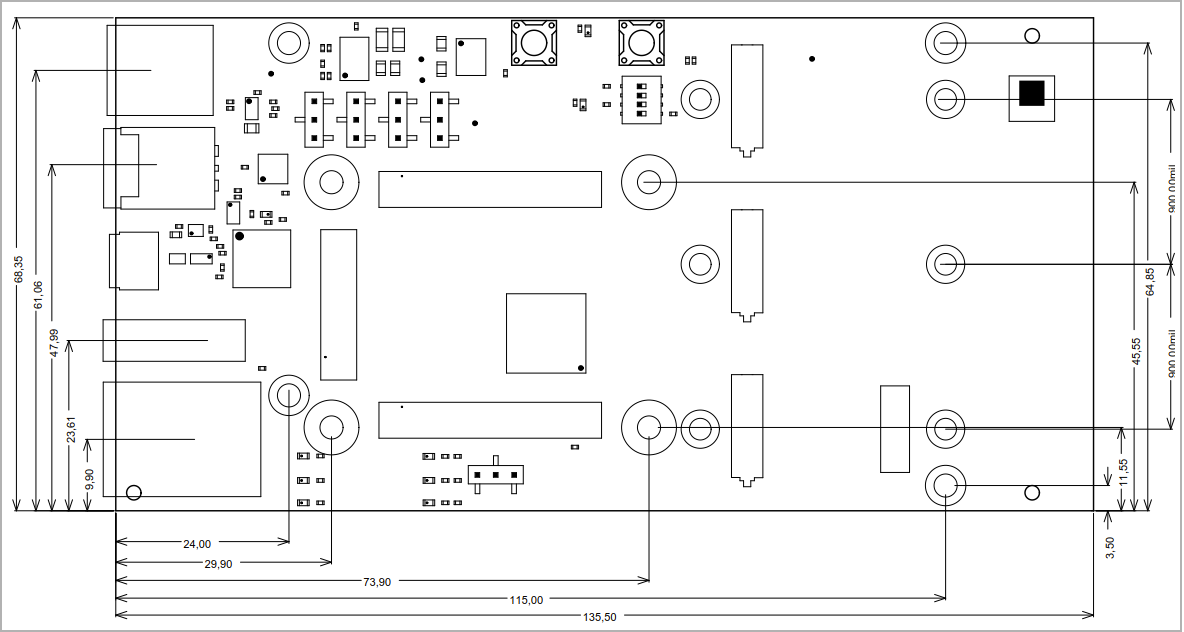

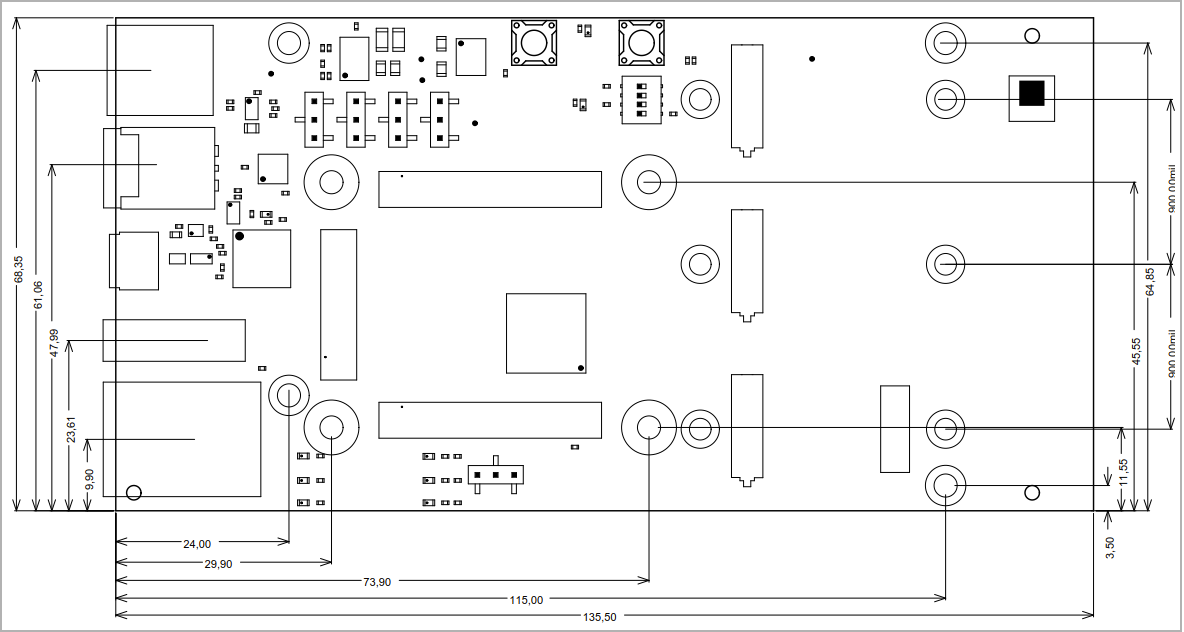

Physical Dimensions

...

| Scroll Title |

|---|

| anchor | Figure_TS_PD |

|---|

| title | Physical Dimension |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| |

|---|

| diagramName | TEB0707_TS_PD |

|---|

| simpleViewer | false |

|---|

| width | 639 |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| diagramWidth | 641591 |

|---|

| revision | 67 |

|---|

|

|

| Scroll Only |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

|

|

|

...

| Scroll Title |

|---|

| anchor | Table_RH_HRH |

|---|

| title | Hardware Revision History |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Revision | Changes | Documentation Link |

|---|

| 2020-11-20 | REV02 | first production release | REV02 | | 2020-04-01 | REV01 | PrototypesInitial Release | - |

|

Hardware revision number can be found on the PCB board together with the module model number separated by the dash.

| Scroll Title |

|---|

| anchor | Figure_RV_HRN |

|---|

| title | Board hardware revision number. |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| |

|---|

| diagramName | TEB0707_RV_HRN |

|---|

| simpleViewer | false |

|---|

| width | 200 |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| diagramWidth | 238122 |

|---|

| revision | 37 |

|---|

|

|

| Scroll Only |

|---|

Image Removed Image Removed Image Added Image Added

|

|

Document Change History

...

| Scroll Title |

|---|

| anchor | Table_RH_DCH |

|---|

| title | Document change history. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Revision | Contributor | Description |

|---|

| Page info |

|---|

| infoType | Modified date |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| type | Flat |

|---|

|

| | Page info |

|---|

| infoType | Current version |

|---|

| prefix | v. |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| | Page info |

|---|

| infoType | Modified by |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| | -- | all | | Page info |

|---|

| infoType | Modified users |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| |

|

...

| Include Page |

|---|

| IN:Legal Notices |

|---|

| IN:Legal Notices |

|---|

|

| draw.io Diagram |

|---|

| border | false |

|---|

| diagramName | TEB0707_OV_MC |

|---|

| simpleViewer | false |

|---|

| width | 639 |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

diagramDisplayName | | lbox | true |

|---|

| diagramWidth | 641 |

|---|

| revision | 3 |

|---|

|