Page History

...

| Scroll pdf title | ||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||

|

...

| Scroll pdf title | ||

|---|---|---|

| ||

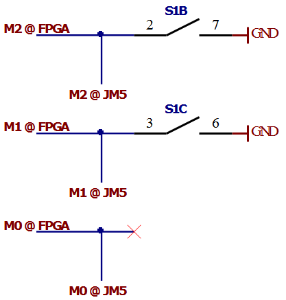

Xilinx Spartan-3 generation FPGAs have a dedicated four-wire IEEE 1149.1/1532 JTAG port that is always available any time the FPGA is powered and regardless of the mode pin settings. However, when the FPGA mode pins are set for JTAG mode (M[2:0] = <1:0:1>), the FPGA waits to be configured via the JTAG port after a power-on event or after PROG_B is pulsed Low. Selecting the JTAG mode simply disables the other configuration modes. No other pins are required as part of the configuration interface.

M0-M2 have Pull ups in FPGA.

...

| Scroll pdf title | ||||||||

|---|---|---|---|---|---|---|---|---|

| ||||||||

|

...

| title | Configuration modes schematic |

|---|

...

Overview

Content Tools