| Page properties |

|---|

|

Template Revision 3.1

- Module: TRM Name always "TE Series Name" +TRM

Example: "TE0728 TRM"

Template Change history: Template Change history: - 3.02 to 3.1

- New general notes for temperature range to "Recommended Operating Conditions"

- 3.01 to 3.02

- add again fix table of content with workaround to use it for pdf and wiki

- Export Link for key features examples

- Notes for different Types (with and without Main FPGA)

- Export Link for Signals, Interfaces and Pins examples

- Notes for different Types (Modul, Modul Hypride, Evalboard, Carrier)

- 3.0 to 3.01

- remove fix table of content and page layout ( split page layout make trouble with pdf export)

- changed and add note to signal and interfaces, to on board periphery section

- ...(not finished)

- 2.13 to 3.00

- → separation of Carrier/Module and evaluation kit TRM

- 2.14 to 2.15

- add excerpt macro to key features

- 2.13 to 2.14

- add fix table of content

- add table size as macro

|

| Page properties |

|---|

|

Important General Note:

|

| Page properties |

|---|

|

----------------------------------------------------------------------- |

| Page properties |

|---|

|

Note for Download Link of the Scroll ignore macro: |

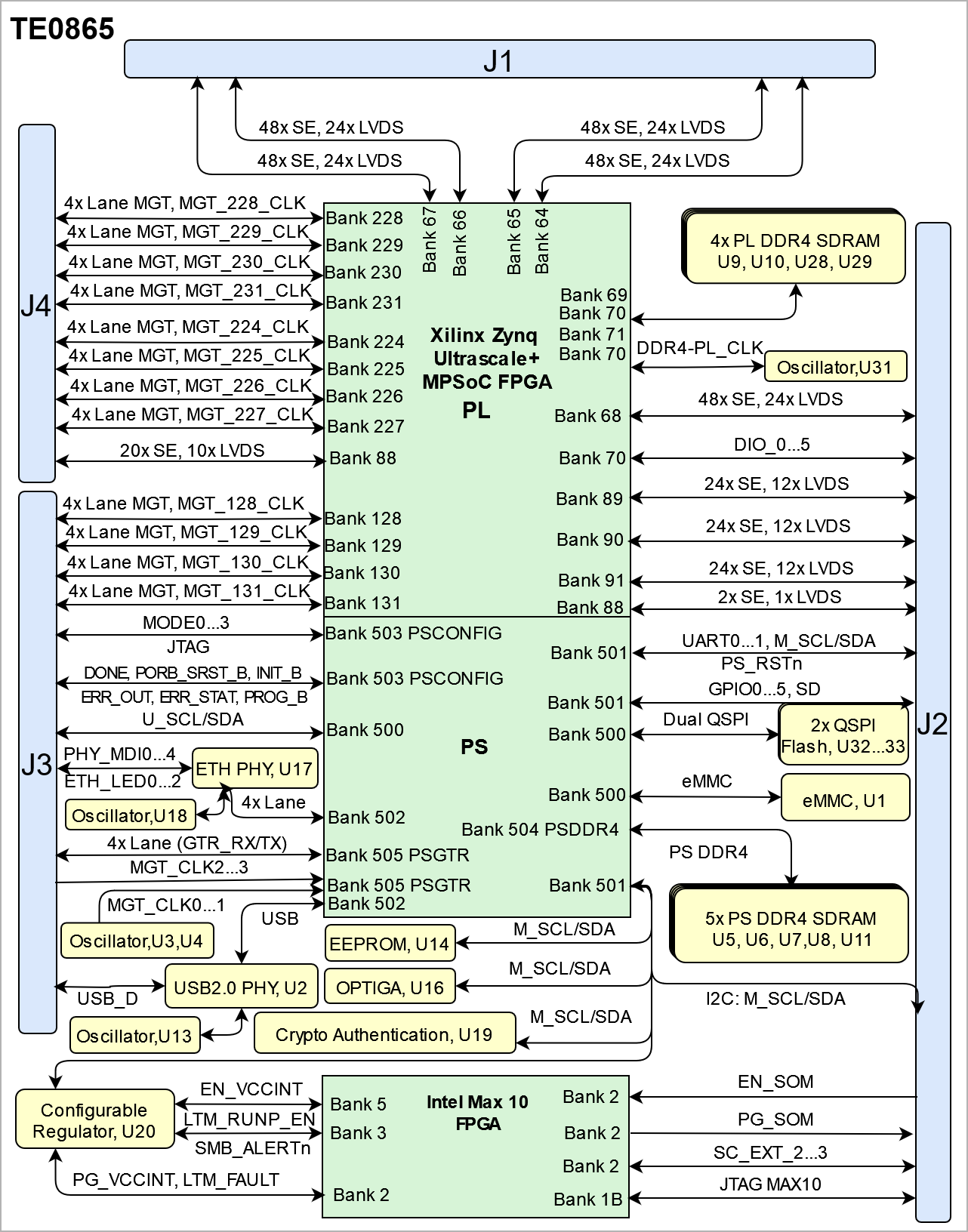

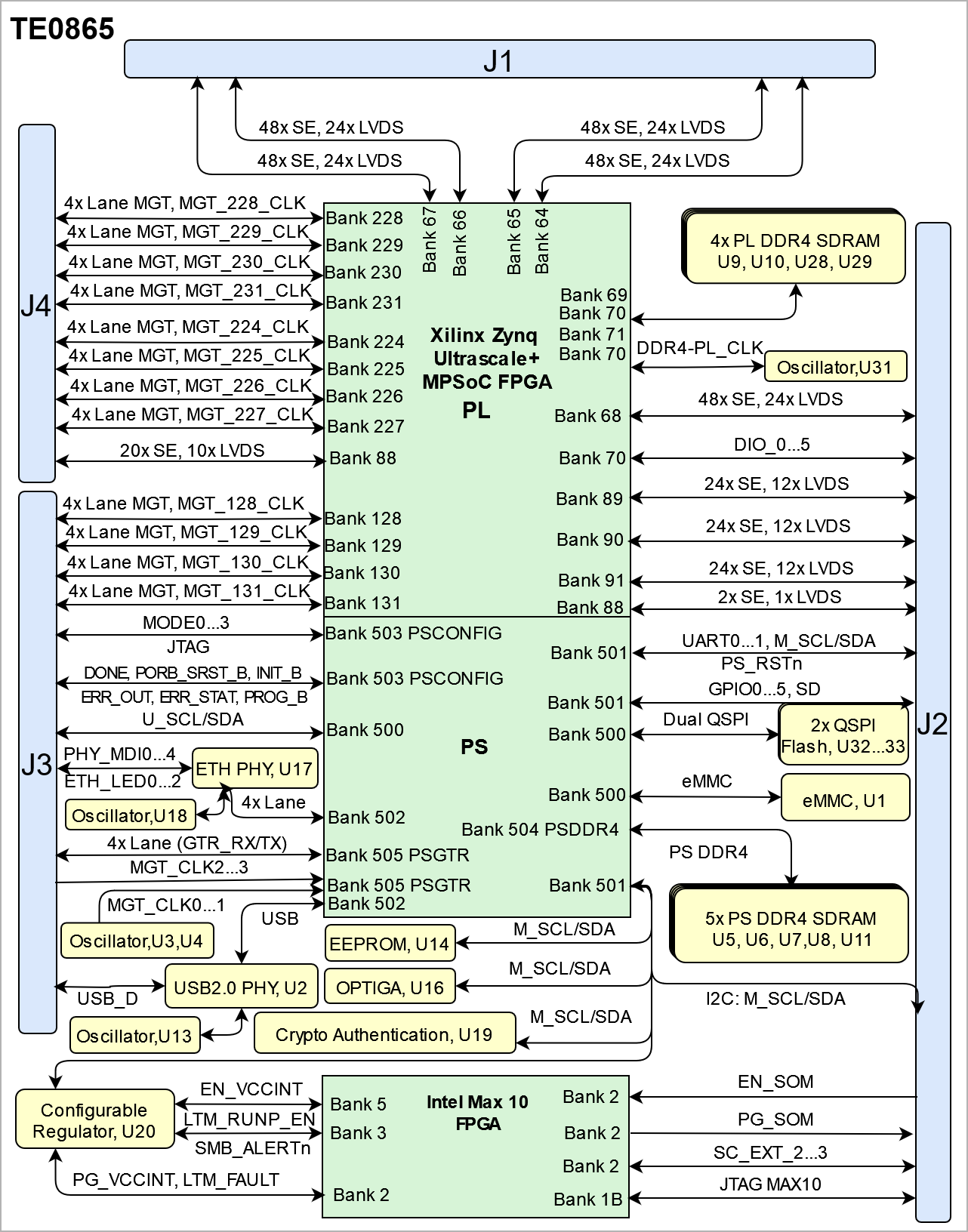

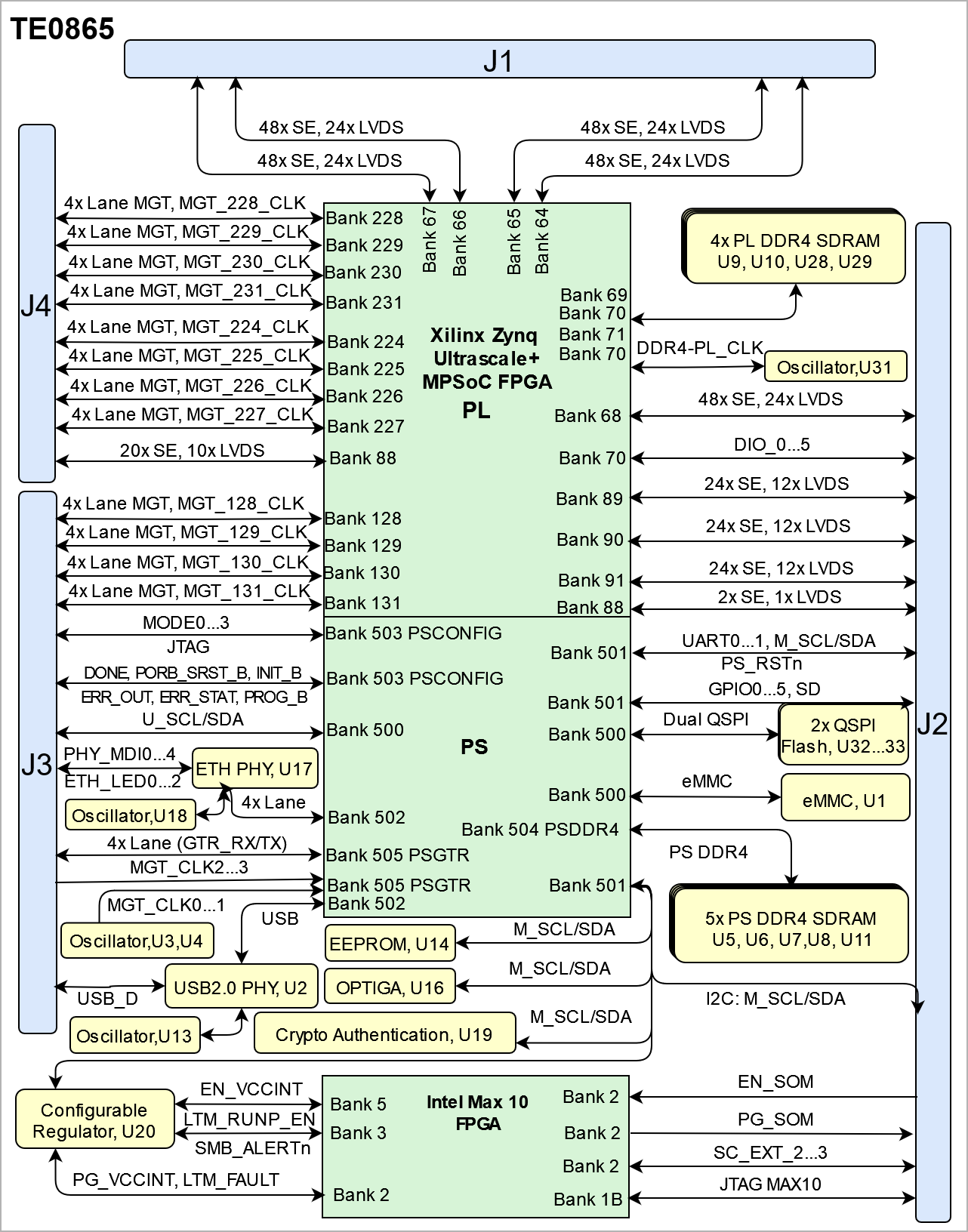

Overview

The Trenz Electronic TE0865 is an industrial/extended grade module based on Xilinx Zunq UltraScale+ MPSoC. The TE0865 is equipped with 4x 2GB DDR4 SDRAM connected to Programmable Logic(PL) and 5x 2GB DDR4 SDRAM connected to Processing System(PS), 8 GB eMMC, 2x 64MB Quad SPI Flash, Gigabit Ethernet Transceiver, USB Transceiver, Ultra micro power terminal and an Intel MAx 10 as system controller CPLD.

Refer to http://trenz.org/te0865-info for the current online version of this manual and other available documentation.

Key Features

| Excerpt |

|---|

- SoC/FPGA

- Package: C1760

- Device: ZU11, ZU17, ZU19*

- Engine: EG*

- Speed: -1, -2,*, **

- Temperature: I, E,*, **

- RAM/Storage

- Low Power DDR4 on PS

- Data width: 16bit

- Size: def. 2GB*

- Speed: 3200 (MT/s) ***

- Low Power DDR4 on PL

- Data width: 16bit

- Size: def. 2GB*

- Speed:***

- eMMC

- Data width: 8Bit

- size: def. 8GB *

- Dual QSPI boot Flash in dual parallel mode (size depends on assembly version)

- Data width: 8bit

- size: def. 64MB *

- MAC address serial EEPROM with EUI-48™ node identity (Microchip 24AA025E48)

- On Board

- Intel Max 10 as CPLD

- 6x MEMS Oscillator

- Gigabit Ethernet transceiver PHY (Marvell Alaska 88E1512)

- Hi-speed USB2 ULPI transceiver with full OTG support (Microchip USB3340C)

- Interface

- 214 x PS I/Os

- 96x HD I/Os

- 416x HP I/Os

- 4x PS GTR

- 3x Samtec Accelerate HD B2B connector

- 78x MIOs

- Power

- 12V input supply voltage

- Variable Bank IO Power Input

- Dimension

- Notes

- * depends on assembly version

- ** also non low power assembly options possible

- *** depends on used U+ Zynq and DDR4 combination

|

Block Diagram

| Page properties |

|---|

|

add drawIO object in Scroll Ignore section and add reference image in Scroll Only.

| Note |

|---|

Title (not anchor) of all Scroll Title such as DrawIOs and Tables should be changed according to the Module name. Example: TE0812 Block Diagram |

| Note |

|---|

All created DrawIOs should be named according to the Module name: Example: DrawIO of TE0812 Block Diagram should be named TE0812_OV_BD |

|

| Scroll Title |

|---|

| anchor | Figure_OV_BD |

|---|

| title | TE0865 block diagram |

|---|

|

| Scroll Ignore |

|---|

| Scroll Only |

|---|

Image Removed Image Removed| draw.io Diagram |

|---|

| border | false |

|---|

| |

|---|

| diagramName | TE0865_OV_BD |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| diagramWidth | 641 |

|---|

| revision | 17 |

|---|

|

|

| Scroll Only |

|---|

Image Added Image Added

|

|

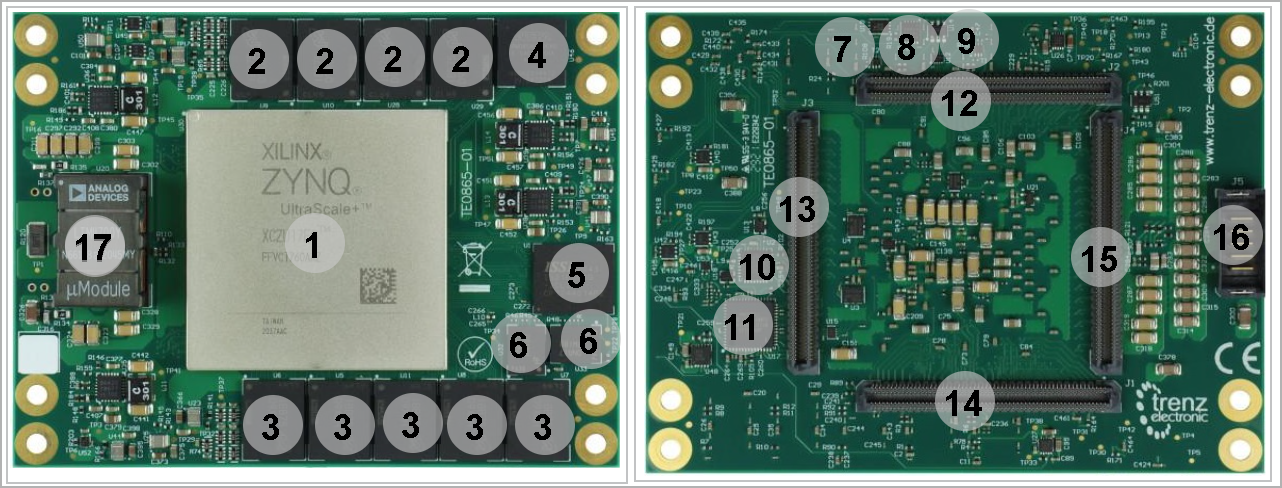

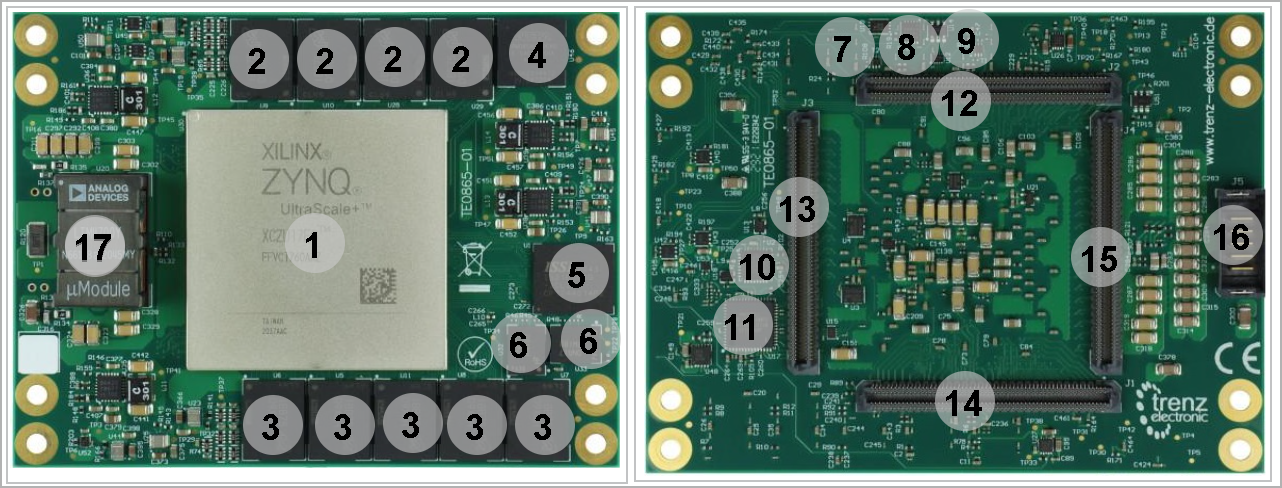

Main Components

| Page properties |

|---|

|

Notes : - Picture of the PCB (top and bottom side) with labels of important components

- Add List below

|

| Scroll Title |

|---|

| anchor | Figure_OV_MC |

|---|

| title | TE0865 main components |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| |

|---|

| diagramName | TE0865_OV_MC |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| diagramWidth | 641 |

|---|

| revision | 4 |

|---|

|

|

| Scroll Only |

|---|

|

|

- ZYNQ Ultrascale+ MPSoC FPGA, U30

- PL DDR4 SDRAM, U9, U10, U28, U29

- PS DDR4 SDRAM, U5...U8, U11

- Intel MAX 10 FPGA, U46

- eMMC RAM, U1

- Dual QSPI Flash, U32, U33

- Crypto Authentication IC, U19

- OPTIGA Trust M Authentication IC, U16

- EEPROM MAC Address, U14

- USB2.0 Transceiver, U2

- Gigabit Ethernet Transceiver, U17

- B2B Connector, J2

- B2B Connector, J3

- B2B Connector, J1

- B2B Connector, J4

- Power Terminal, J5

Initial Delivery State

| Page properties |

|---|

|

| Note |

|---|

Only components like EEPROM, QSPI flash can be initialized by default at manufacture. If there is no components which might have initial data ( possible on carrier) you must keep the table empty |

|

| Scroll Title |

|---|

| anchor | Table_OV_IDS |

|---|

| title | Initial delivery state of programmable devices on the module |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

Storage device name | Content | Notes |

|---|

Quad SPI Flash | Not Programmed |

| | EEPROM | Programmed | MAC Address | | System Controller CPLD | Programmed | Intel MAX 10 | | PL DDR4 SDRAM | Not Programmed |

| | PS DDR4 SDRAM | Not Programmed |

| | eMMC | Not Programmed |

|

|

Configuration Signals

| Page properties |

|---|

|

- Overview of Boot Mode, Reset, Enables.

|

| Scroll Title |

|---|

| anchor | Table_OV_CNTRL |

|---|

| title | Controller signal. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

Function | Schematic | Connected to | Direction | Description |

|---|

Boot Mode | MODE0...3 | B2B, J3A | Input |

| | Reset | PERST0 | B2B, J1B | Input |

| | PGOOD | PG_VCCINT | CPLD, U46 | Output |

| | Power Enable | EN_VCCINT | CPLD, U46 | Input |

|

|

Signals, Interfaces and Pins

Board to Board (B2B) I/Os

FPGA bank number and number of I/O signals connected to the B2B connector:

| Scroll Title |

|---|

| anchor | Table_SIP_B2B |

|---|

| title | General PL I/O to B2B connectors information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| FPGA Bank | B2B Connector | I/O Signal Count | Voltage Level | Notes |

|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

JTAG Interface

JTAG access to the UltraScale+ MPsoC FPGA through B2B connector J3B.

| Scroll Title |

|---|

| anchor | Table_SIP_JTG |

|---|

| title | JTAG pins connection |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

JTAG Signal | B2B Connector |

|---|

| TMS | J3B- D59 | | TDI | J3B- D57 | | TDO | J3B- D58 | | TCK | J3B- D56 |

|

JTAG access to the system controller CPLD, Intel MAX10 FPGA(U46) through B2B connector J2B.

| Scroll Title |

|---|

| anchor | Table_SIP_JTG |

|---|

| title | JTAG pins connection |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

JTAG Signal | B2B Connector |

|---|

| TCK_MAX10 | J2B- D56 | | TMS_MAX10 | J2B- D57 | | TDO_MAX10 | J2B- D58 | | TDI_MAX10 | J2B- D59 | | JTAGEN | Pulled Up |

|

MIO Pins

| Page properties |

|---|

|

you must fill the table below with group of MIOs which are connected to a specific components or peripherals, you do not have to specify pins in B2B, Just mention which B2B is connected to MIOs. The rest is clear in the Schematic. Example: | MIO Pin | Connected to | B2B | Notes |

|---|

| MIO12...14 | SPI_CS , SPI_DQ0... SPI_DQ3 SPI_SCK | J2 | QSPI |

|

| Scroll Title |

|---|

| anchor | Table_SIP_MIOs |

|---|

| title | MIOs pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| MIO Pin | Connected to | Notes |

|---|

| MIO0...5 | QSPI Flash, U32 |

| | MIO6...11 | QSPI, Flash, 33 |

| | MIO13...22 | eMMC, U1 |

| | MIO23 | B2B, J2A | U_INIT | | MIO24...25 | B2B, J3B | I2C U via Voltage Transform, U15 | | MIO26...27 | B2B, J2A | UART0_RX | | MIO28...29 | B2B, J2A | UART1_RX | | MIO30...31 | B2B, J2A | I2C M via Voltage Transform, U12 | | MIO32...37 | B2B, J2A | GPIO0...5 | | MIO38 | B2B, J2A | M_INIT | | MIO39...42 | B2B, J2B | SD | | MIO43 | B2B, J2A | PS_RSTn | | MIO44...51 | B2B, J2A | SD | | MIO52...63 | USB2.0, U2 | USB2.0 | | MIO64...77 | ETH PHY, U17 | ETH PHY |

|

Test Points

| Page properties |

|---|

|

you must fill the table below with group of Test Point which are indicated as TP in a schematic. If there is no Test Point remarked in the schematic, delet the Test Point section. Example: | Test Point | Signal | B2B | Notes |

|---|

| 10 | PWR_PL_OK | J2-120 |

|

|

| Scroll Title |

|---|

| anchor | Table_SIP_TPs |

|---|

| title | Test Points Information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Test Point | Signal | Notes |

|---|

| TP1...2 | +12.0V |

| | TP3...4 | +3.3V |

| | TP5...6 | +3.3V_SW |

| | TP7...8 | +2.3V |

| | TP9...10 | +1.8V |

| | TP11...12 | +1.8V_AUX |

| | TP13...14 | +1.8V_VCCADC |

| | TP15...16 | +0.85V_VCCINT |

| | TP17...18 | +1.2V_PL_DDR |

| | TP19...20 | +2.5V_PL_DDR |

| | TP21...22 | +0.85V_GTR_AVCC_PS |

| | TP23...24 | +1.8V_GTR_AVTT_PS |

| | TP25...26 | +1.8V_AUX_PS |

| | TP27...28 | +1.2V_PLL_PS |

| | TP29...30 | +1.2V_PS_DDR |

| | TP31...32 | +2.5V_PS_DDR |

| | TP33...34 | VREFA_DDR_PS |

| | TP35...36 | VREFA_DDR_PL |

| | TP37...38 | VTT_DDR_PS |

| | TP39...40 | VTT_DDR_PL |

| | TP41...42 | +0.9V_GTH_AVCC |

| | TP43...44 | +1.8V_GTH_AUX |

| | TP45...46 | +1.2V_GTH_AVTT |

| | TP47...48 | +0.9V_GTY_AVCC |

| | TP49...50 | +1.8V_GTY_AUX |

| | TP51...52 | +1.2V_GTY_AVTT |

|

|

On-board Peripherals

| Page properties |

|---|

|

Notes : In the on-board peripheral table "chip/Interface" must be linked to the corresponding chapter or subsection by assigning advance link using: #NameOfTheSection Example: #ClockSources, #CPLD, #QuadSPIFlash |

| Scroll Title |

|---|

| anchor | Table_OBP |

|---|

| title | On board peripherals |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Chip/Interface | Designator | Notes |

|---|

| Intel MAX 10 | U46 |

| | PL DDR4 SDRAM | U9, U10, U28, U29 |

| | PS DDR4 RAM | U5...U8, U11 |

| | Dual QSPI Flash | U32, U33 |

| | eMMC RAM | U1 |

| | USB2.0 Transceiver | U2 |

| | Gigabit Ethernet Transceiver | U17 |

| | EEPROM | U14 |

| | Crypto Authentication | U19 |

| | OPTIGA Authentication | U16 |

| | MEMS Oscillator, |

|

|

|

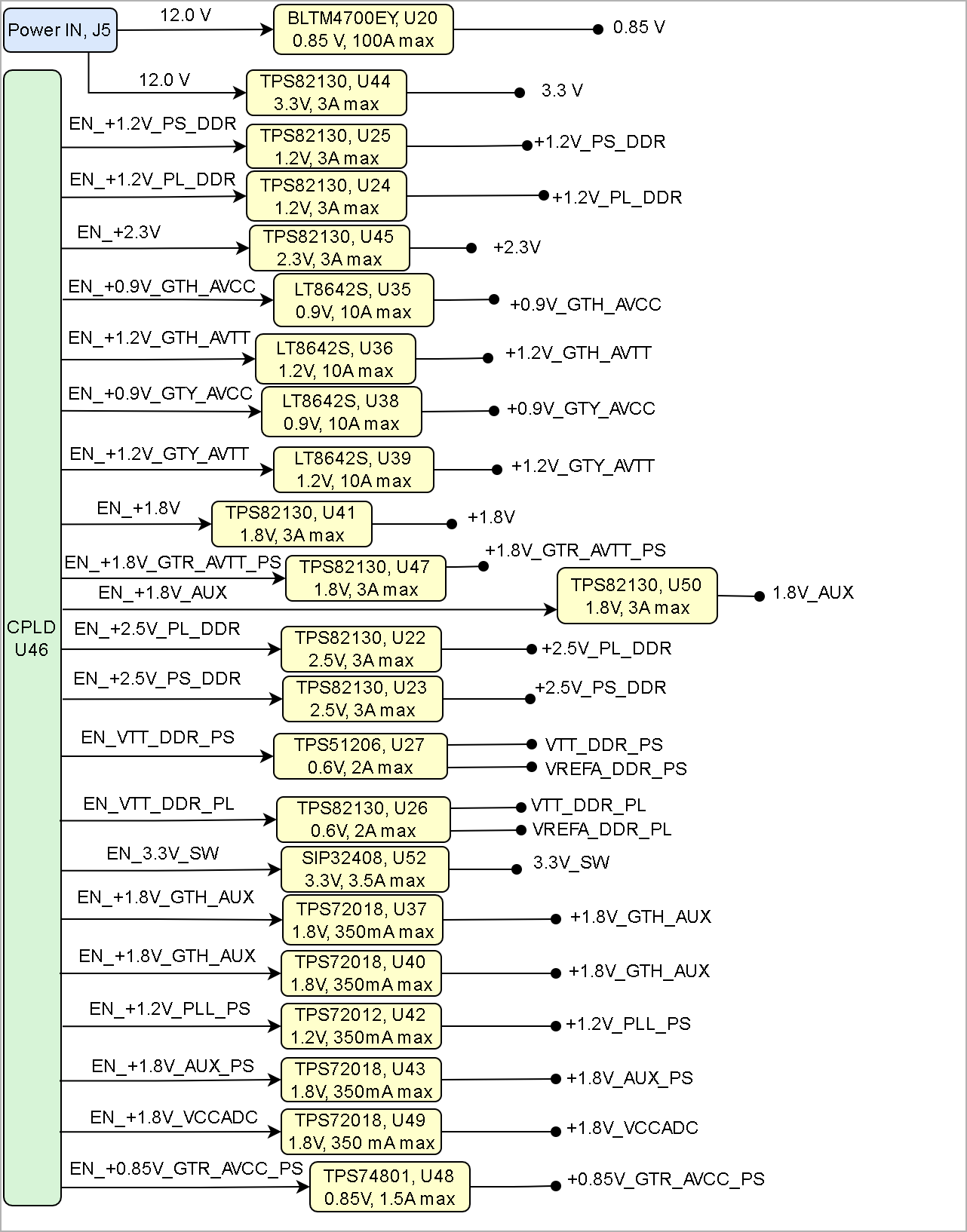

CPLD

| Page properties |

|---|

|

| Note |

|---|

Link always to CPLD Documentation, because CPLD Firmware can be changed during the time. Describe used device type and basic Pin connection to B2B and Main FPGA |

|

Quad SPI Flash Memory

| Page properties |

|---|

|

Notes : Minimum and Maximum density of quad SPI flash must be mentioned for other assembly options. |

| Scroll Title |

|---|

| anchor | Table_OBP_SPI |

|---|

| title | Quad SPI interface MIOs and pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| MIO Pin | Schematic | U?? Pin | Notes |

|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Crypto Authentication

OPTIGA Authentication

EEPROM

| Scroll Title |

|---|

| anchor | Table_OBP_EEP |

|---|

| title | I2C EEPROM interface MIOs and pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| MIO Pin | Schematic | U?? Pin | Notes |

|---|

|

|

|

|

|

|

|

|

|

| Scroll Title |

|---|

| anchor | Table_OBP_I2C_EEPROM |

|---|

| title | I2C address for EEPROM |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| MIO Pin | I2C Address | Designator | Notes |

|---|

|

|

|

|

|

PL DDR4 SDRAM

| Page properties |

|---|

|

Notes : Minimum and Maximum density of DDR3 SDRAM must be mentioned for other assembly options. (pay attention to supported address length for DDR3) |

The TE???? SoM has ??? GByte volatile DDR3 SDRAM IC for storing user application code and data.

- Part number:

- Supply voltage:

- Speed:

- NOR Flash

- Temperature:

PS DDR4 SDRAM

| Page properties |

|---|

|

Notes : Minimum and Maximum density of DDR3 SDRAM must be mentioned for other assembly options. (pay attention to supported address length for DDR3) |

The TE???? SoM has ??? GByte volatile DDR3 SDRAM IC for storing user application code and data.

- Part number:

- Supply voltage:

- Speed:

- NOR Flash

- Temperature:

Ethernet

| Scroll Title |

|---|

| anchor | Table_OBP_ETH |

|---|

| title | Ethernet PHY to Zynq SoC connections |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| U?? Pin | Signal Name | Connected to | Signal Description | Note |

|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

eMMC

| Scroll Title |

|---|

| anchor | Table_OBP_eMMC |

|---|

| title | eMMC Information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

|

Clock Sources

| Scroll Title |

|---|

| anchor | Table_OBP_CLK |

|---|

| title | Osillators |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Designator | Description | Frequency | Note |

|---|

|

| MHz |

|

|

| MHz |

|

|

| KHz |

|

|

|

|

|

|

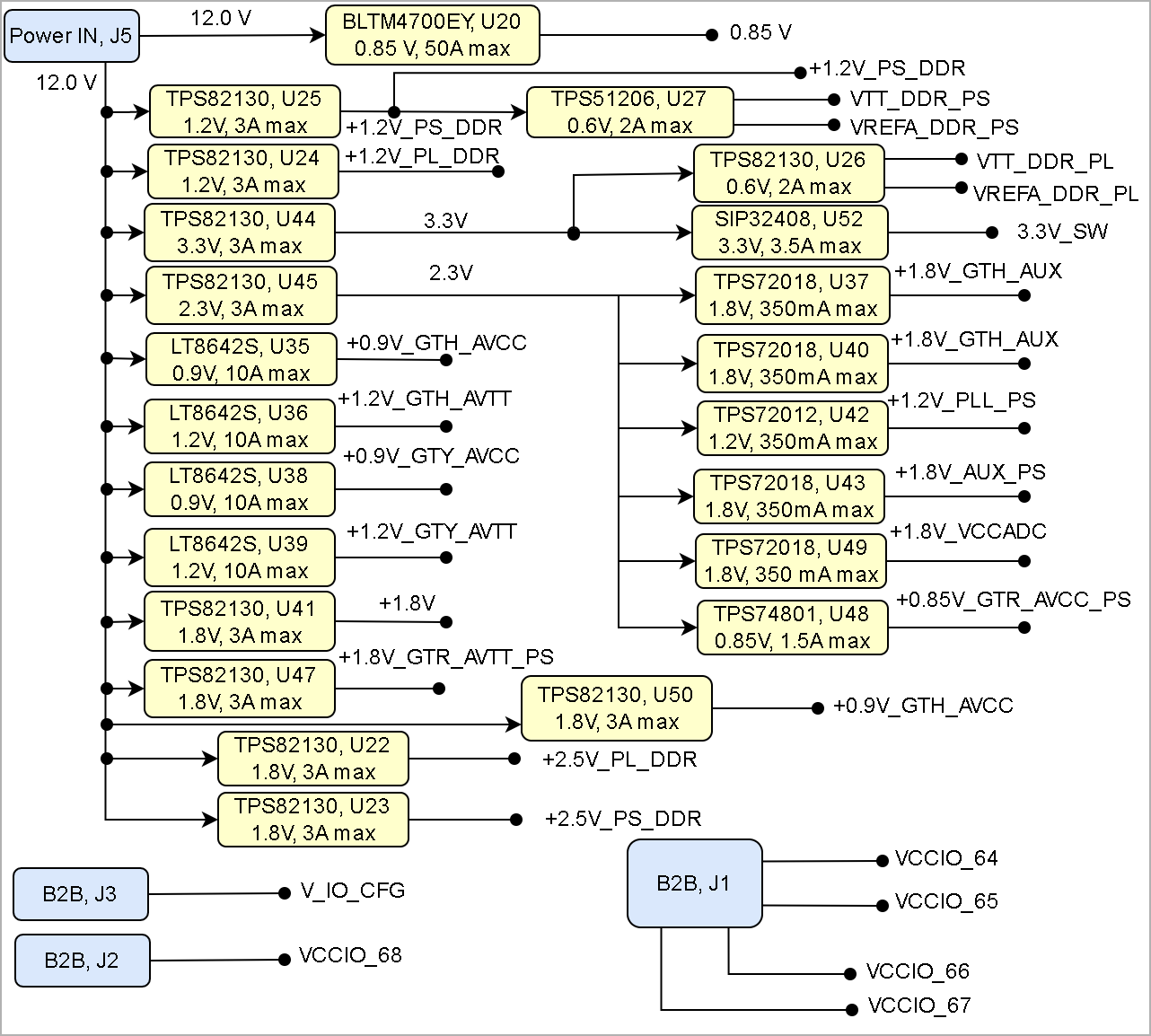

Power and Power-On Sequence

| Page properties |

|---|

|

In 'Power and Power-on Sequence' section there are three important digrams which must be drawn: - Power on-sequence

- Power distribution

- Voltage monitoring circuit

|

Power Supply

Power supply with minimum current capability of xx A for system startup is recommended.

Power Consumption

| Scroll Title |

|---|

| anchor | Table_PWR_PC |

|---|

| title | Power Consumption |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Power Input Pin | Typical Current |

|---|

| VIN | TBD* |

|

* TBD - To Be Determined

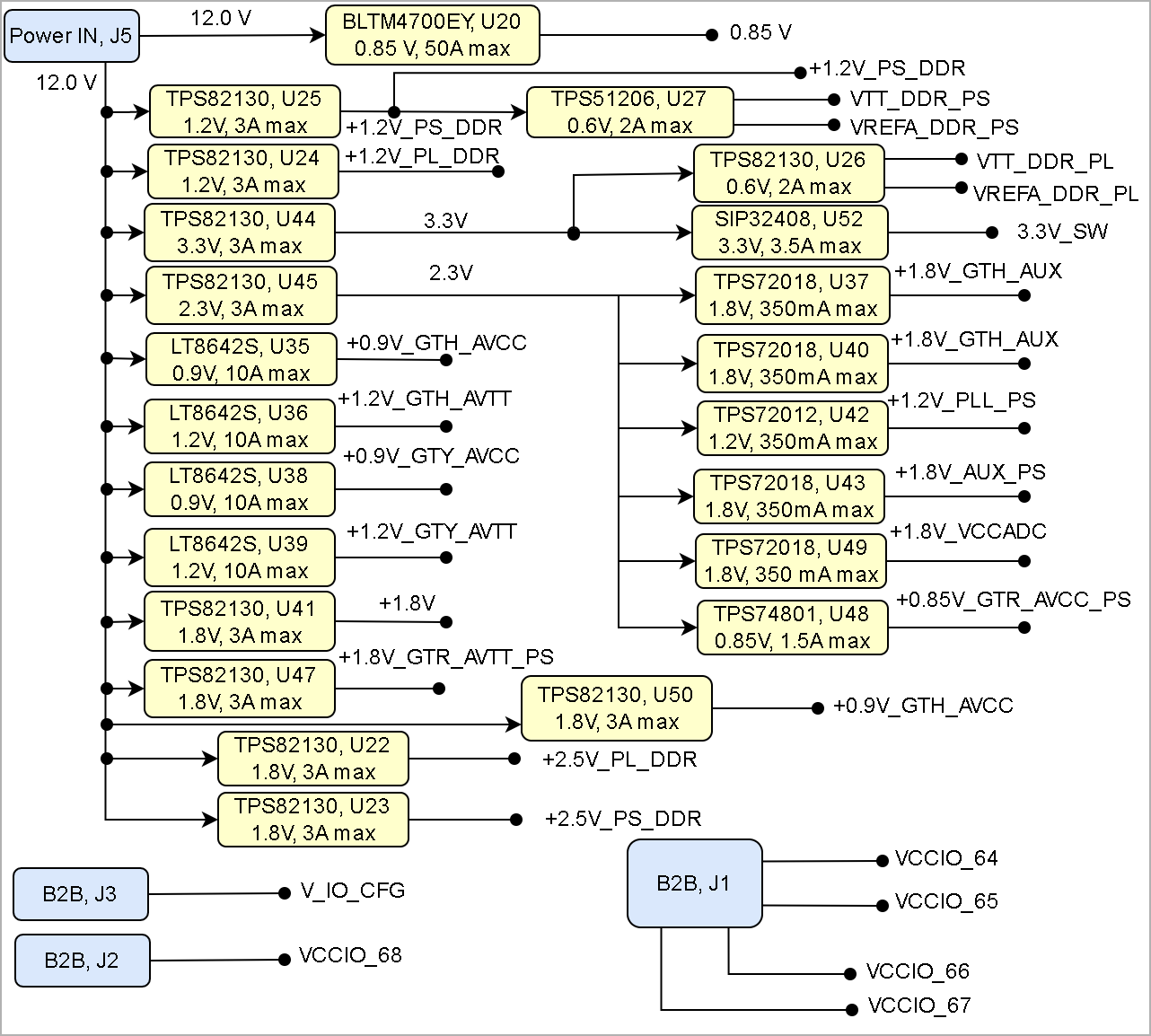

Power Distribution Dependencies

| Scroll Title |

|---|

| anchor | Figure_PWR_PD |

|---|

| title | Power Distribution |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| |

|---|

| diagramName | TE0865_PWR_PD |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| diagramWidth | 641 |

|---|

| revision | 1 |

|---|

|

|

| Scroll Only |

|---|

|

|

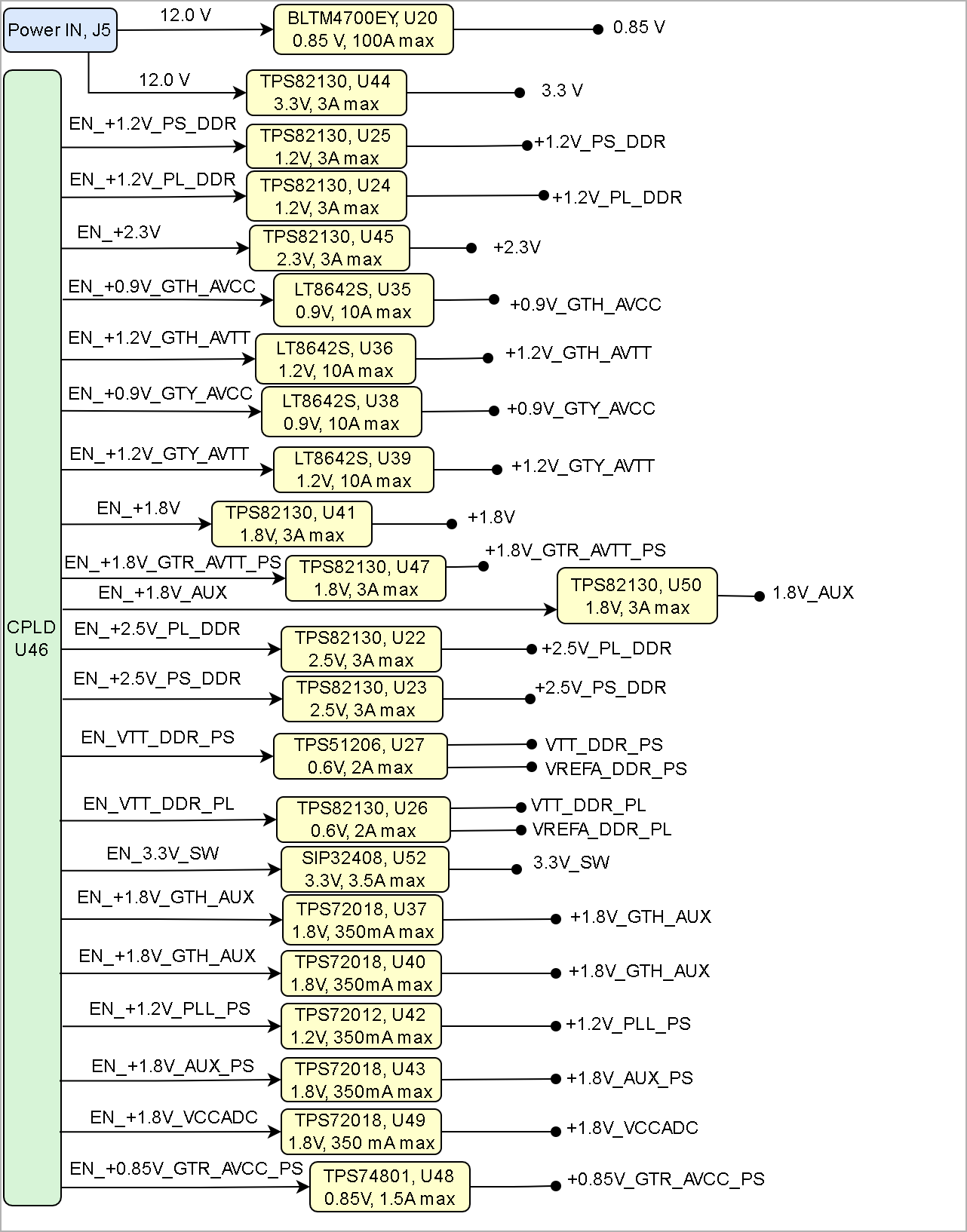

Power-On Sequence

| Scroll Title |

|---|

| anchor | Figure_PWR_PS |

|---|

| title | Power Sequency |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| |

|---|

| diagramName | TE0865_PWR_PS |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| diagramWidth | 641 |

|---|

| revision | 1 |

|---|

|

|

| Scroll Only |

|---|

|

|

Voltage Monitor Circuit

| Scroll Title |

|---|

| anchor | Figure_PWR_VMC |

|---|

| title | Voltage Monitor Circuit |

|---|

|

| Scroll Ignore |

|---|

Create DrawIO object here: Attention if you copy from other page, objects are only linked. |

| Scroll Only |

|---|

image link to the generate DrawIO PNG file of this page. This is a workaround until scroll pdf export bug is fixed |

|

Power Rails

| Scroll Title |

|---|

| anchor | Table_PWR_PR |

|---|

| title | Module power rails. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Power Rail Name | B2B J1 Pin | B2B J2 Pin | B2B J3 Pin | B2B J4 Pin | Direction | Notes |

|---|

| VCCIO_67 | D10 | - | - | - | In |

| | VCCIO_66 | D20 | - | - | - | In |

| | VCCIO_64 | D35 | - | - | - | In |

| VCCIO_65 | D45 | - | - | - | In |

| | VCCIO_91 | - | A6, | - | - | In |

| | VCCIO_90 | - | B10 | - | - | In |

| | VCCIO_89 | - | A21 | - | - | In |

| | V_IO_CFG | - | A45 | - | - | In |

| | +1.2V_PL_DDR | - | B44 | - | - | Out |

| | VCCIO_68 | - | C29 | - | - | In |

| | VCCIO_88 | - | D44 | - | - | In |

| | +3.3V | - | D60 | - | - | Out |

| | +1.8V | - |

| D60 | - | Out |

|

|

Bank Voltages

| Scroll Title |

|---|

| anchor | Table_PWR_BV |

|---|

| title | Zynq SoC bank voltages. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Schematic Name | | Notes |

|---|

| 64 HP | VCCIO_64 | max 1.8 V |

| | 65 HP | VCCIO_65 | max 1.8 V |

| | 66 HP | VCCIO_66 | max 1.8 V |

| | 67 HP | VCCIO_67 | max 1.8 V |

| | 68 HP | VCCIO_68 | max 1.8 V |

| | 69 HP | VCCIO_69 | 1.2 V |

| | 70 HP | VCCIO_70 | 1.2 V |

| | 71 HP | VCCIO_71 | 1.2 V |

| | 88 HD | VCCIO_88 | max 3.3V | ZU17 Bank 90 HD | | 89 HD | VCCIO_88 | max 3.3 V | ZU17 Bank 91 HD | | 90 HD | VCCIO_88 | max 3.3V | ZU17 Bank 93 HD | | 91 HD | VCCIO_88 | max 3.3V | ZU17 Bank 94 HD | | 128 GTY | MGTAVCC_L | 0.9 V |

| | 129 GTY | MGTAVCC_L | 0.9 V |

| | 224 GTH | MGTAVCC_RS | 0.9 V |

| | 225 GTH | MGTAVCC_RS | 0.9 V |

| | 228 GTH | MGTAVCC_RN | 0.9 V |

| | 229 GTH | MGTAVCC_RN | 0.9 V |

| | 500 PSMIO | VCCO_PSIO0_500 | 1.8 V |

| | 501 PSMIO | VCCO_PSIO0_501 | max 3.3 V |

| | 502 PSMIO | VCCO_PSIO0_502 | 1.8 V |

| | 504 PSDDR | VCCO_PSDDR_504 | 1.2 V |

| | 505 PSGTR | PS_MGTRAVCC | 0.85 V |

|

|

Board to Board Connectors

| Page properties |

|---|

|

- This section is optional and only for modules.

use "include page" macro and link to the general B2B connector page of the module series, For example: 6 x 6 SoM LSHM B2B Connectors

| Include Page |

|---|

| PD:6 x 6 SoM LSHM B2B Connectors |

|---|

| PD:6 x 6 SoM LSHM B2B Connectors |

|---|

|

|

Technical Specifications

Absolute Maximum Ratings

| Scroll Title |

|---|

| anchor | Table_TS_AMR |

|---|

| title | PS absolute maximum ratings |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Symbols | Description | Min | Max | Unit |

|---|

|

|

|

| V |

|

|

|

| V |

|

|

|

| V |

|

|

|

| V |

|

|

|

| V |

|

|

|

| V |

|

|

|

| V |

|

|

|

| V |

|

|

|

| °C |

|

Recommended Operating Conditions

Operating temperature range depends also on customer design and cooling solution. Please contact us for options.

| Scroll Title |

|---|

| anchor | Table_TS_ROC |

|---|

| title | Recommended operating conditions. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Parameter | Min | Max | Units | Reference Document |

|---|

|

|

| V | See ???? datasheets. |

|

|

| V | See ???? datasheet. |

|

|

| V | See ???? datasheet. |

|

|

| V | See ???? datasheet. |

|

|

| V | See ???? datasheet. |

|

|

| V | See ???? datasheet. |

|

|

| V | See ???? datasheet. |

|

|

| °C | See ???? datasheet. |

|

|

| °C | See ???? datasheet. |

|

Components are mainly classified in 3 temperature groups, according to range specifications: commercial: 0°C - 75°C extended: 0°C - 85°C industrial: -40°C - 85°C

Classification of the module can be locked up here: Article Number Information i.e.: TE0803-03-5D"I"21-AS (The I indicates industrial)

The actual operation temperature range depends on the FPGA/SoC design/utilization and cooling, as well as other variables. Please note: These are only indications!

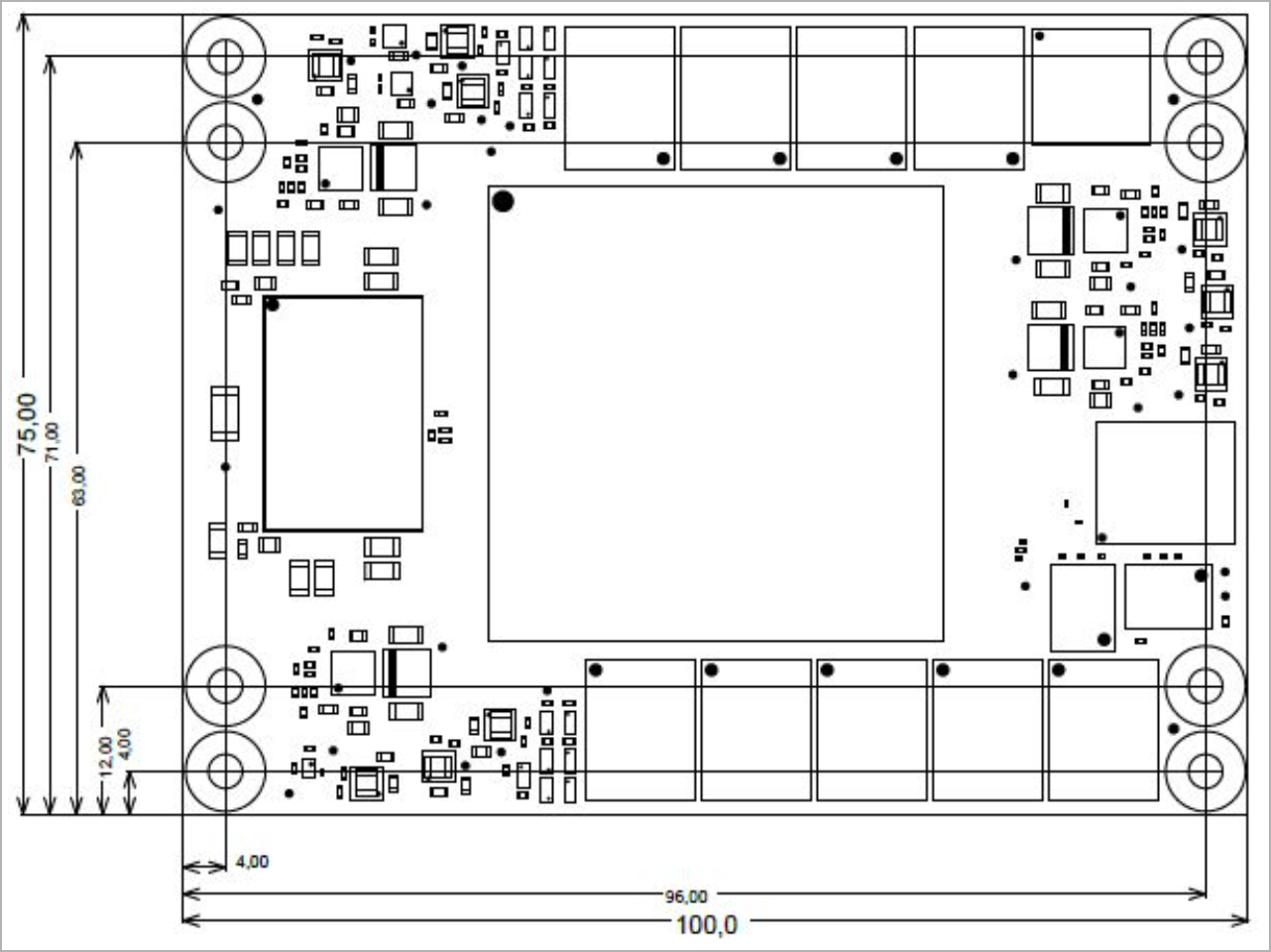

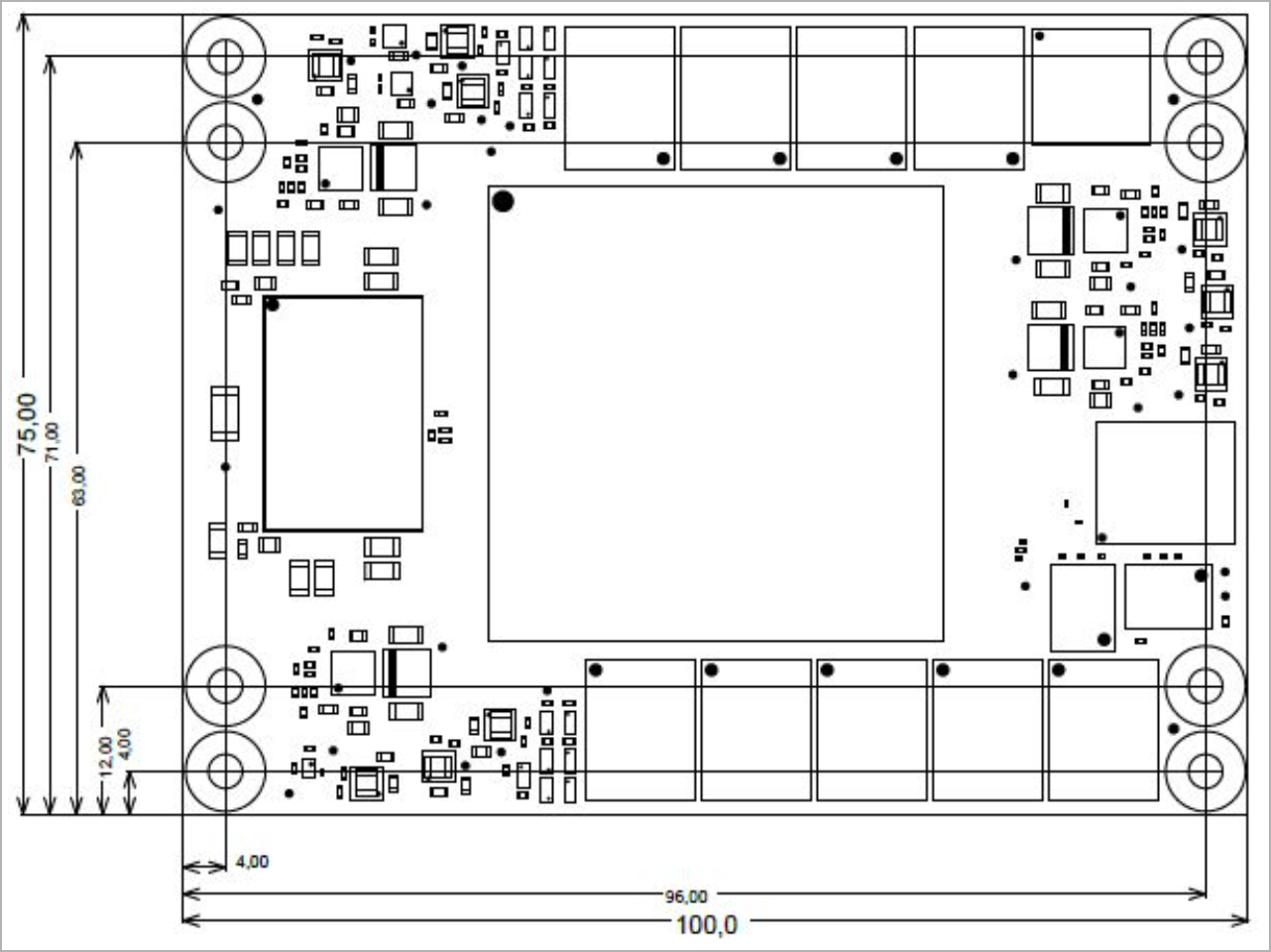

Physical Dimensions

PCB thickness: 2 mm.

| Scroll Title |

|---|

| anchor | Figure_TS_PD |

|---|

| title | Physical Dimension |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| |

|---|

| diagramName | TE0865_TS_PD |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| diagramWidth | 641 |

|---|

| revision | 2 |

|---|

|

|

| Scroll Only |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

|

|

|

Currently Offered Variants

| Scroll Title |

|---|

| anchor | Table_VCP_SO |

|---|

| title | Trenz Electronic Shop Overview |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

|

Revision History

Hardware Revision History

| Scroll Title |

|---|

| anchor | Figure_RV_HRN |

|---|

| title | Board hardware revision number. |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| |

|---|

| diagramName | TE0865_RV_HRN |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| diagramWidth | 132 |

|---|

| revision | 2 |

|---|

|

|

| Scroll Only |

|---|

|

|

| Scroll Title |

|---|

| anchor | Table_RH_HRH |

|---|

| title | Hardware Revision History |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Revision | Changes | Documentation Link |

|---|

| 2021-04-15 | REV01 | Initial Release |

|

|

Hardware revision number can be found on the PCB board together with the module model number separated by the dash.

Document Change History

| Page properties |

|---|

|

- Note this list must be only updated, if the document is online on public doc!

- It's semi automatically, so do following

Add new row below first Copy "Page Information Macro(date)" Macro-Preview, Metadata Version number, Author Name and description to the empty row. Important Revision number must be the same as the Wiki document revision number Update Metadata = "Page Information Macro (current-version)" Preview+1 and add Author and change description. --> this point is will be deleted on newer pdf export template - Metadata is only used of compatibility of older exports

|

| Scroll Title |

|---|

| anchor | Table_RH_DCH |

|---|

| title | Document change history. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Revision | Contributor | Description |

|---|

| Page info |

|---|

| infoType | Modified date |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| type | Flat |

|---|

|

| | Page info |

|---|

| infoType | Current version |

|---|

| prefix | v. |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| | Page info |

|---|

| infoType | Modified by |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| | -- | all | | Page info |

|---|

| infoType | Modified users |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| |

|

Disclaimer

| Include Page |

|---|

| IN:Legal Notices |

|---|

| IN:Legal Notices |

|---|

|