1 Overview

This guide shows the main components of the TE0802 module and introduces the first steps to get the provided reference design up and running.

This module TE00802 has a Xilinx Zynq Ultrascale+ and several hardware features onboard that allows you to create digital hardware and software designs. For communication and configuration the module board offers a JTAG/UART Interface.

| Scroll Title |

|---|

| anchor | Figure_VHM |

|---|

| title-alignment | center |

|---|

| title | Module TE0802 |

|---|

|

| draw.io Diagram |

|---|

| border | true |

|---|

| |

|---|

| diagramName | TE0802_start |

|---|

| simpleViewer | false |

|---|

| width | 800 |

|---|

| links | auto |

|---|

| tbstyle | top |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| diagramWidth | 1584 |

|---|

| revision | 11 |

|---|

|

|

1.1 Prerequisites

| Hardware | Software |

|---|

- TE0802 module

- power supply (5V)

- MicroUSB cable

- 3.5mm earphone jack (optional)

- VGA cable (optional)

- ethernet cable

- display port cable (optional)

- USB keyboard (optional)

- SD card

- M.2 NVMe SSD (optional)

| |

Documentation

- Official links to the shop:

- Technical Reference Manual:

- Resources & Reference Designs:

1.3Hardware Features and Overview

Hardware |

| TE0802-02-1AEV2-A | TE0802-02-2AEV2-A |

|---|

| MPSoC | Xilinx Zynq UltraScale+

- XCZU1CG-1SBVA484E

- Speed Grade: -1

- Temperature Grade: Extended (0 to +100 °C)

| Xilinx Zynq UltraScale+

- XCZU2CG-1SBVA484E

- Speed Grade: -1

- Temperature Grade: Extended (0 to +100 °C)

| | Storage | - 1 GByte LPDDR4

- 32 MByte SPI Flash

- MicroSD-Karte

- M2 PCIe SSD support

- EEPROM

| | Display | - DisplayPort

- VGA

- 4-digit 7-segment LED

- 8 LEDs

| | Audio | - 3.5 mm earphone jack (PWM output)

| | Connectors | | | Communication & Debug | - USB 3.0 Host (type A connector)

- USB JTAG/UART Micro-USB

- 1GB Ethernet RJ45

| | Input | - 5 push buttons

- 8 bit slide switches

- Reset button

|

|

| Scroll Title |

|---|

| anchor | Figure_VHM |

|---|

| title-alignment | center |

|---|

| title | TE0802 Hardware overview |

|---|

|

| draw.io Diagram |

|---|

| border | true |

|---|

| |

|---|

| diagramName | TE0802_OV_start |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | top |

|---|

| lbox | true |

|---|

| diagramWidth | 638 |

|---|

| revision | 1 |

|---|

|

|

| Info |

|---|

Information on IO routing and FPGA pin connections can be found in the |

2 Board Power-Up

2.1 TE0802 Reference Design - Introduction

| Scroll Ignore |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

|

|

| Page properties |

|---|

|

ACHTUNG!!! Hier soll noch entschieden werden, ob hier nur kurz auf das Referenzdesign eingegangen wird und die Inhalte im public doc - test board Beschreibung rein genommen werden bzw ... was hier überhaupt noch sinnvoll reingehört ? |

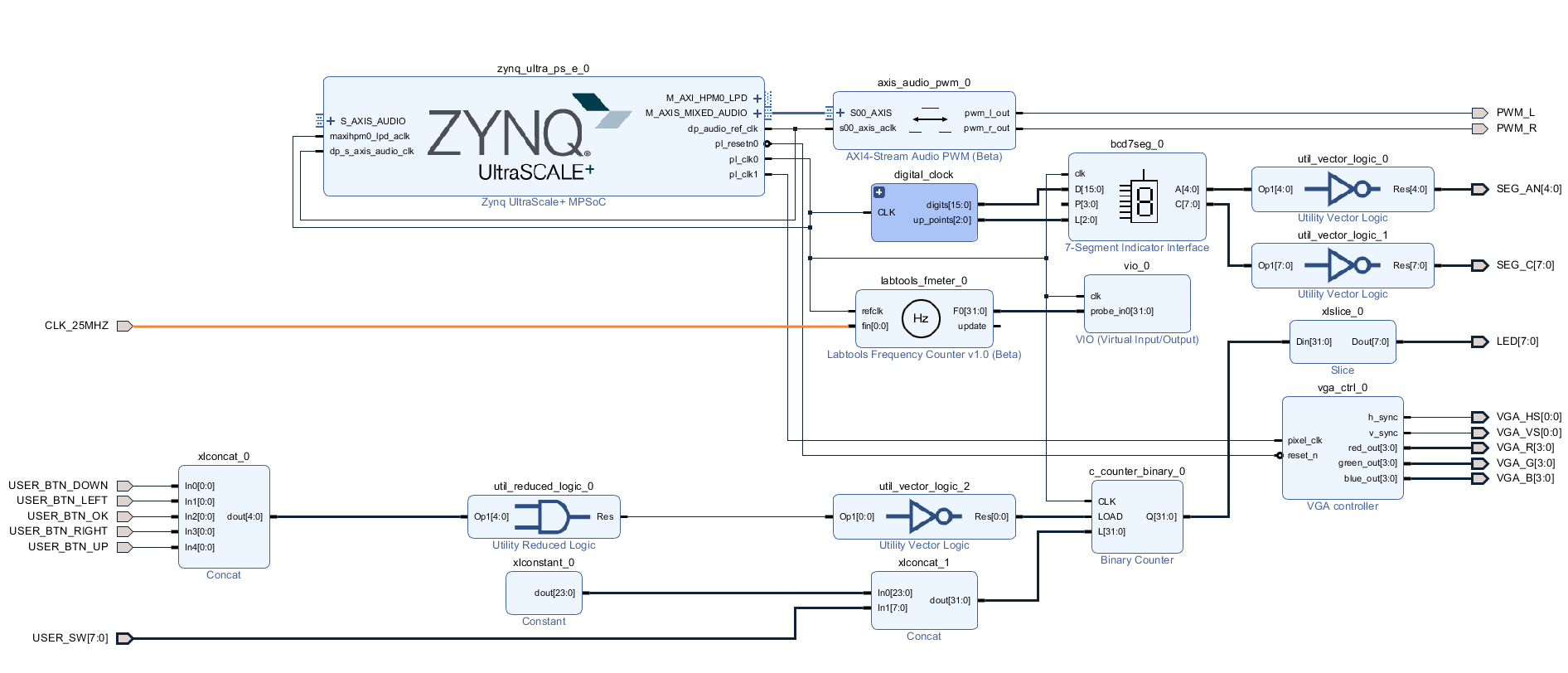

The provided reference design "TE0802 test board" we are introducing in this Getting started guide interacts with most of the peripheral on the module. It shows as an example how to connect the different parts of the module to simplify the development of your own application. You can use it for your own design but keep in mind the overall FPGA resources and power consumption before deployment. The most important steps to get it up and running from the scratch are explained on TE0802 Test Board. The Download is available here.

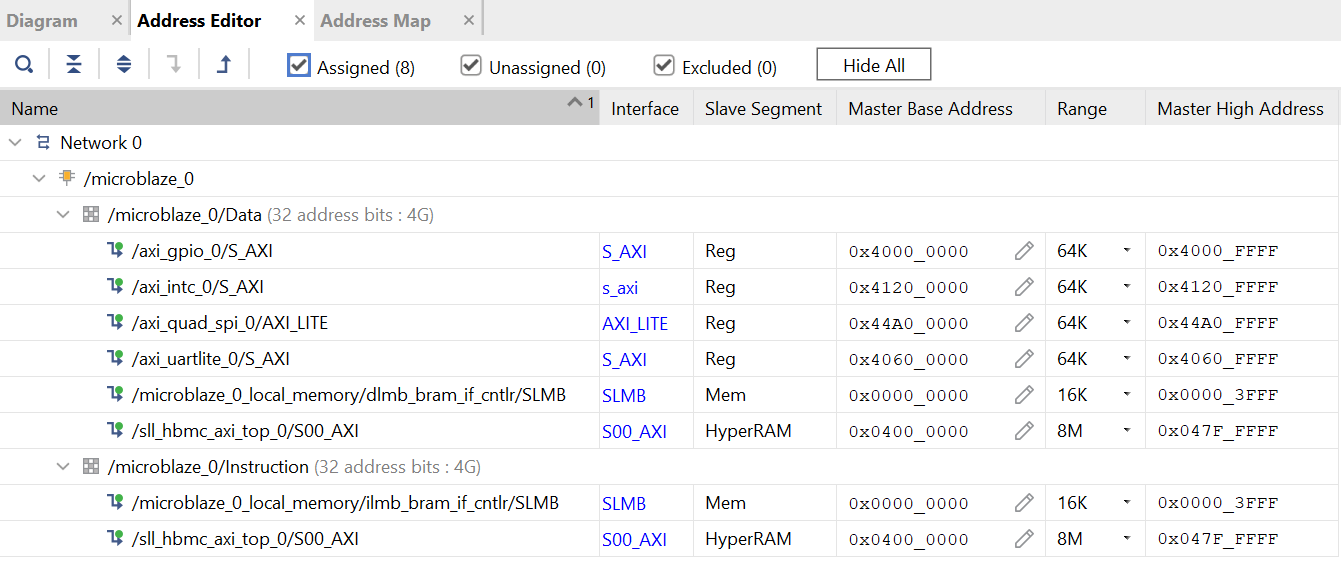

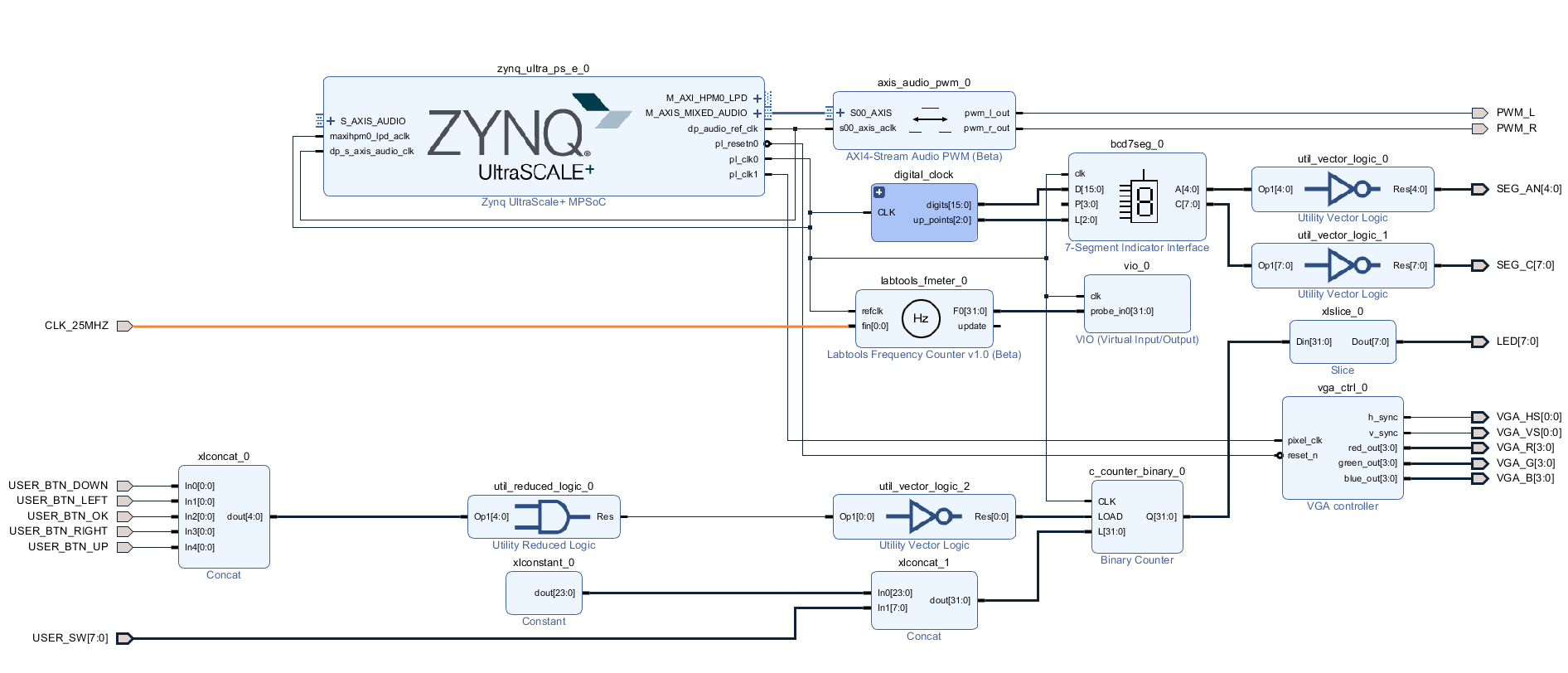

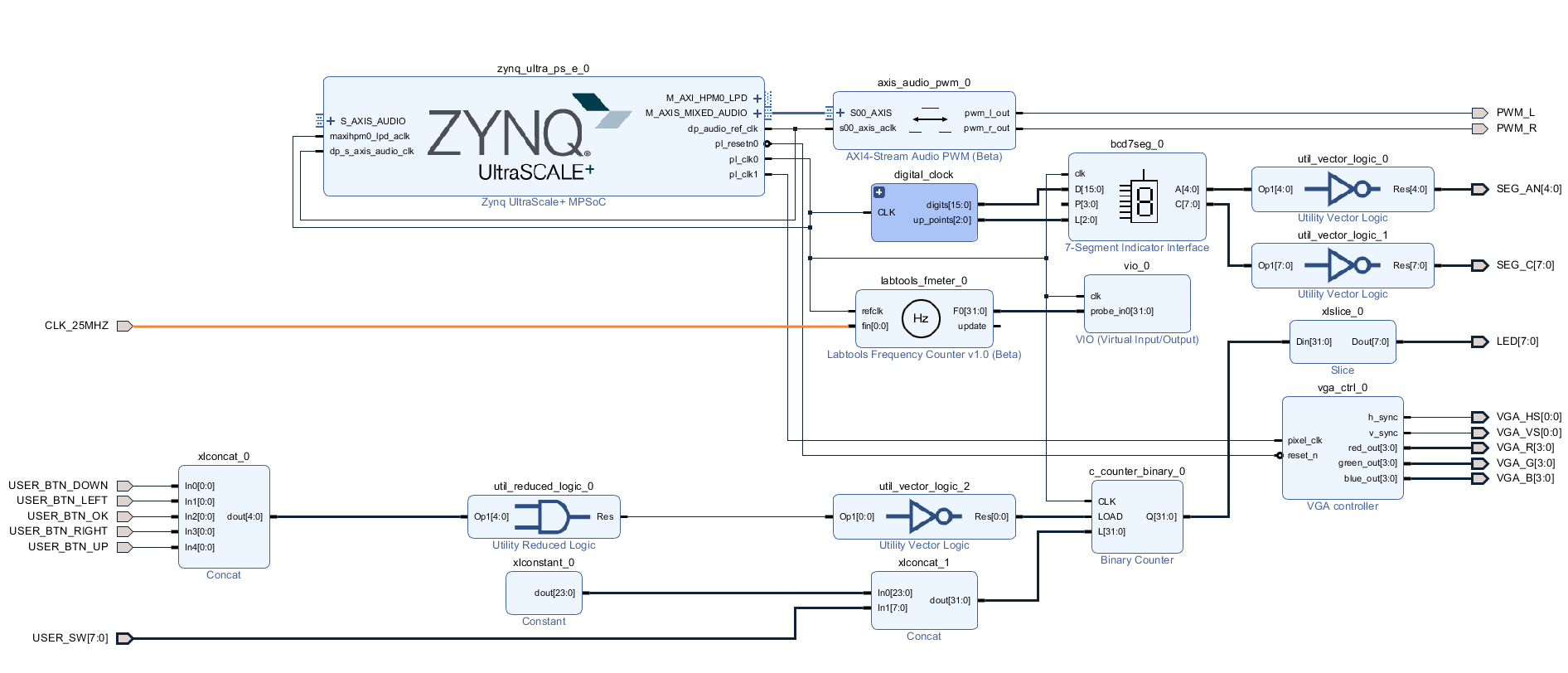

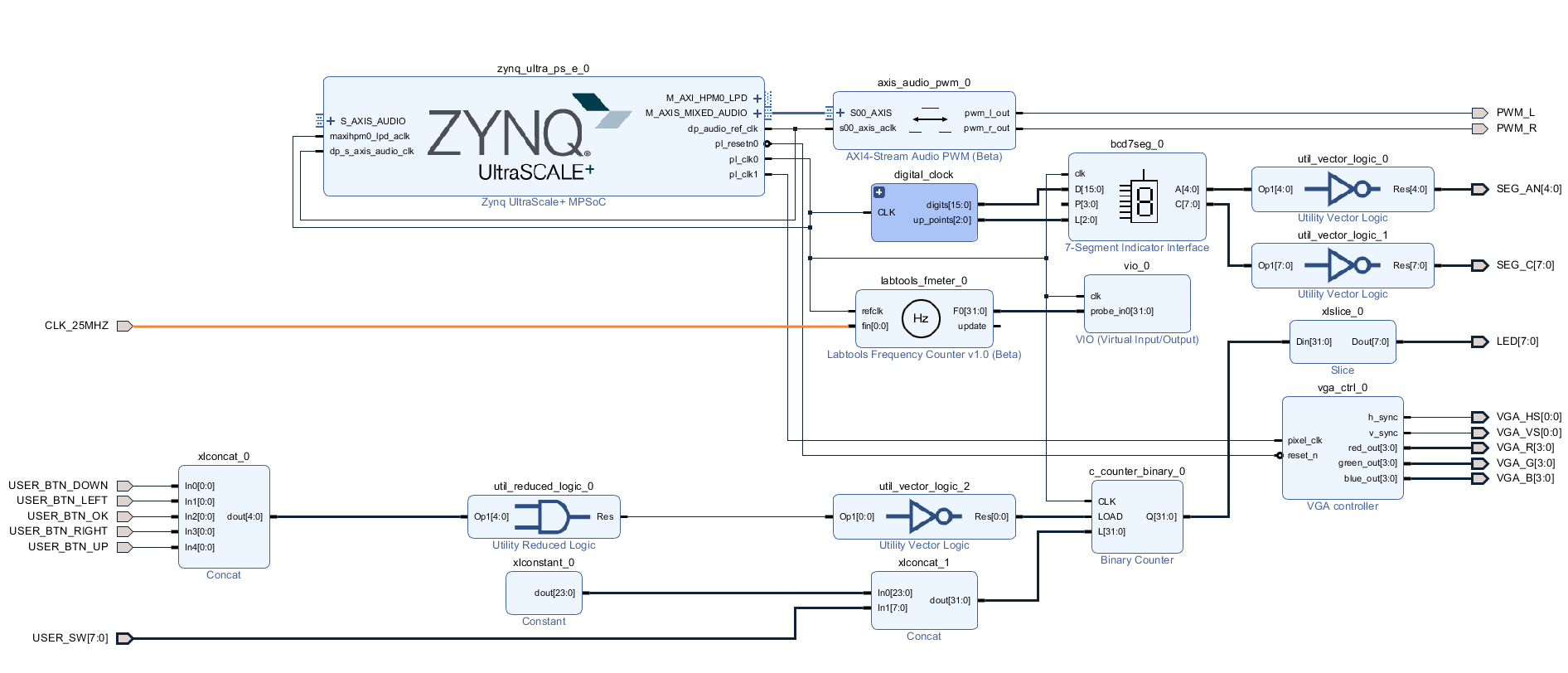

An overview of the components used in this reference design is illustrated in the following figure:

| Scroll Title |

|---|

| anchor | Figure_BD |

|---|

| title-alignment | center |

|---|

| title | Block Design |

|---|

|

Image Added Image Added |

Hardware Setup and Power up in QSPI-Boot mode

(simple Hello Trenz application)| Scroll Ignore |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

|

|

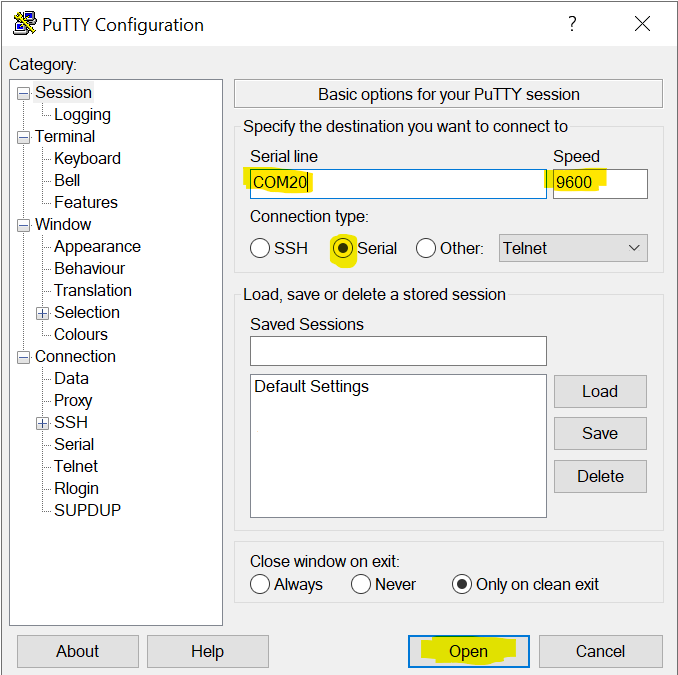

Preparations

- Download the source code and configuration files for "TE0802 test_board" reference design. Ensure that your download files match your Vivado version.

Check the settings from DIP-Switch S1 (JTAG):

| S1.1 | S1.2 | S1.3 | S1.4 |

|---|

| OFF | OFF | OFF | OFF |

- Connect the MicroUSB cable from your module board with your PC

- Connect the module board with the power supply (5V)

- Power on module board

Run _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

| Code Block |

|---|

| language | bash |

|---|

| theme | Midnight |

|---|

| title | _create_win_setup.cmd/_create_linux_setup.sh |

|---|

|

------------------------Set design paths----------------------------

-- Run Design with: _create_win_setup

-- Use Design Path: <absolute project path>

--------------------------------------------------------------------

-------------------------TE Reference Design---------------------------

--------------------------------------------------------------------

-- (0) Module selection guide, project creation...prebuilt export...

-- (1) Create minimum setup of CMD-Files and exit Batch

-- (2) Create maximum setup of CMD-Files and exit Batch

-- (3) (internal only) Dev

-- (4) (internal only) Prod

-- (c) Go to CMD-File Generation (Manual setup)

-- (d) Go to Documentation (Web Documentation)

-- (g) Install Board Files from Xilinx Board Store (beta)

-- (a) Start design with unsupported Vivado Version (beta)

-- (x) Exit Batch (nothing is done!)

----

Select (ex.:'0' for module selection guide): |

- Press '0' and enter to start "Module Selection Guide"

- Select your assembly version

- validate selection

- press '12' and enter to "create Vivado project" and "create and open delivery binary folder"

- Depending on the preferred application, continue with chapter "Linux in QSPI-Boot mode" or "'Hello Trenz' in QSPI-Boot mode"

Linux in QSPI-Boot mode

- Connect the MicroUSB cable from your module board with your PC

- Connect peripherals to devices

- VGA, display port → monitor

- USB → keyboard

- ...

- Connect the module board with the power supply (5V)

- Power on module board

Program 'u-bootProgram 'hello_te0802' application on QSPI flash

| Code Block |

|---|

| language | bash |

|---|

| theme | Midnight |

|---|

| title | run on Vivado TCL (Script programs BOOT.bin on QSPI flash) |

|---|

|

TE::pr_program_flash -swapp hello_te0802u-boot |

- Power off module board

- Copy image.ub, init.sh and boot.scr on SD card (e.g. <project folder>\test_board\_binaries_TE0802-02-2AEV2-A\boot_linux)

Switch the DIP-Switch S1 to QSPI-Boot mode

| S1.1 | S1.2 | S1.3 | S1.4 |

|---|

| ON | OFF | OFF | OFF |

- Insert the SD card into the module board

Power on Restart the module board

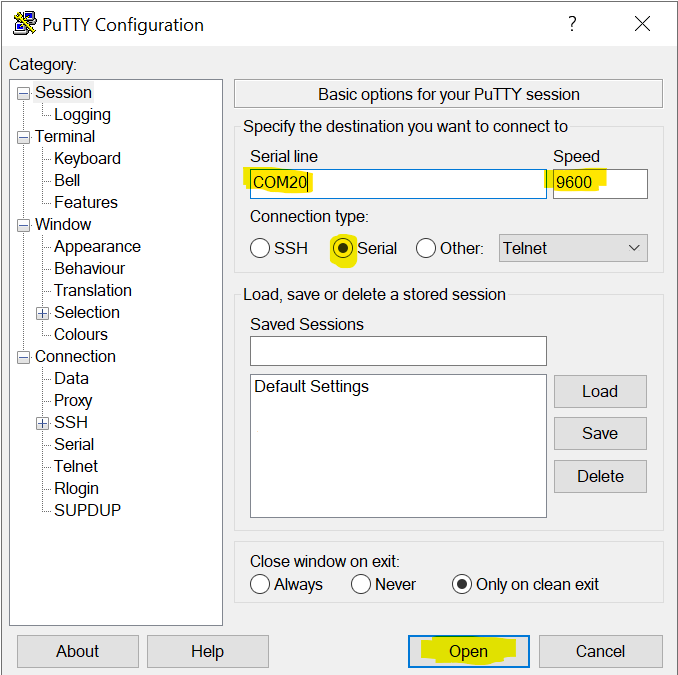

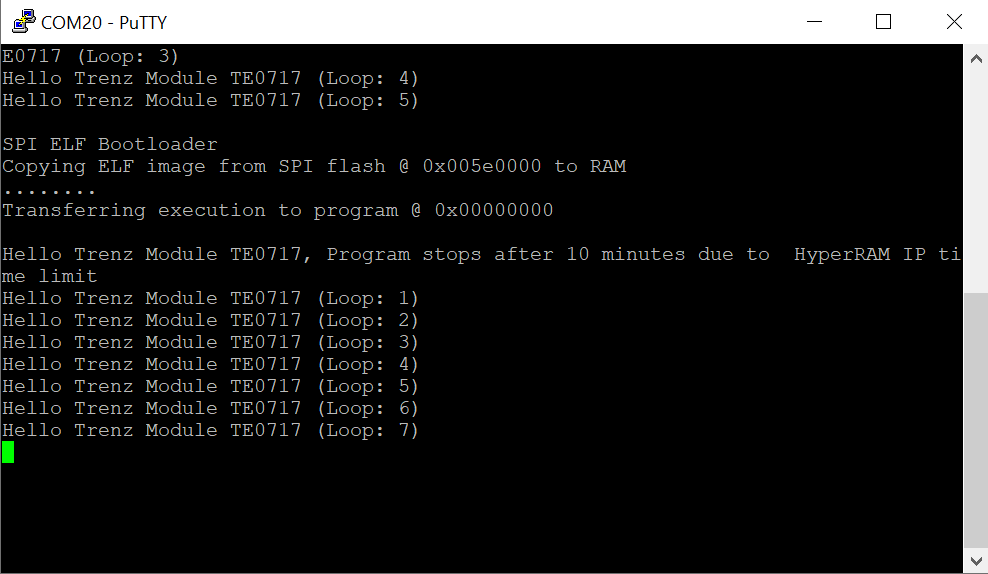

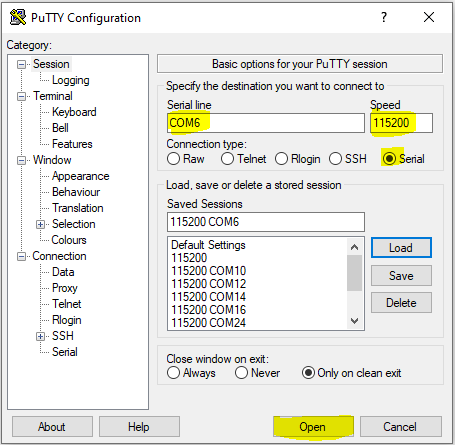

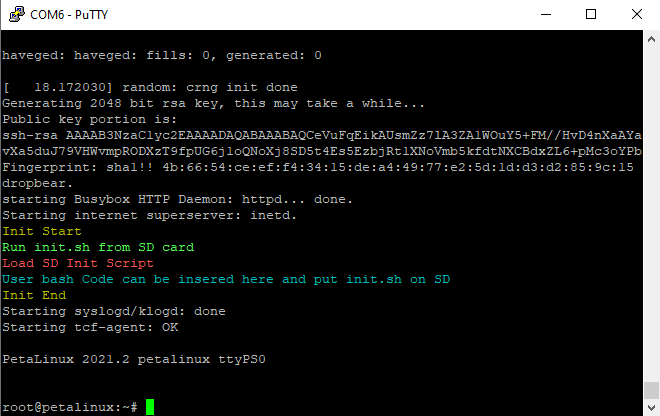

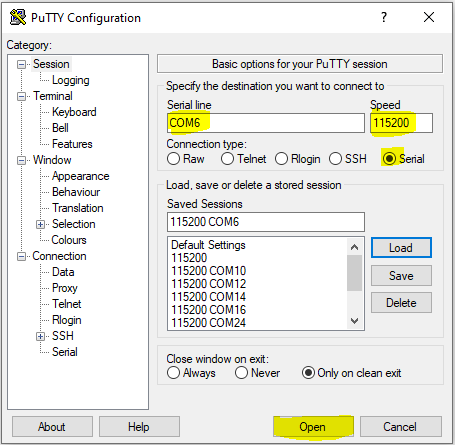

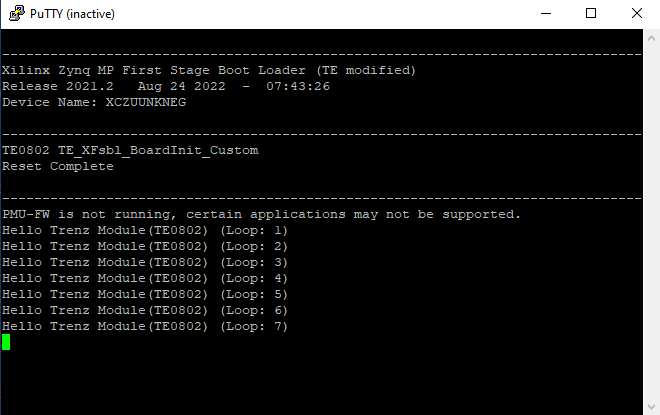

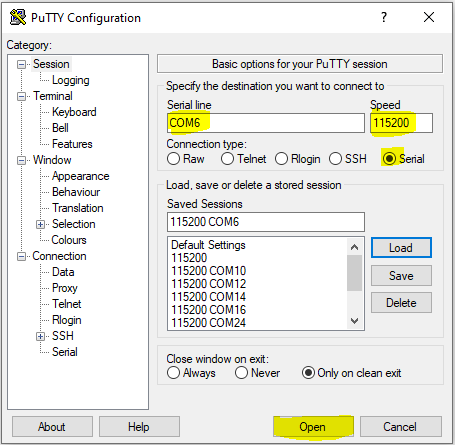

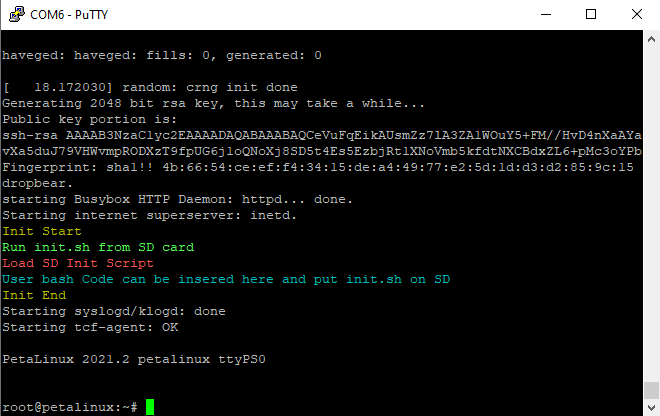

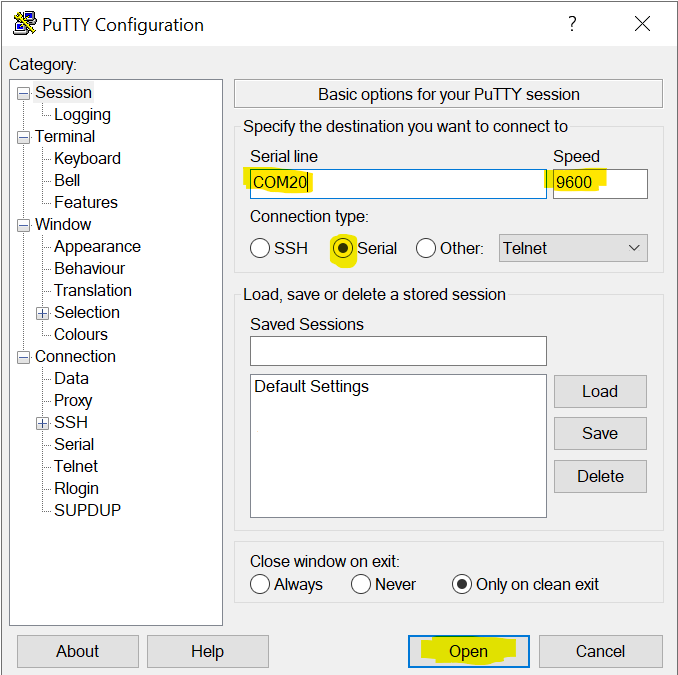

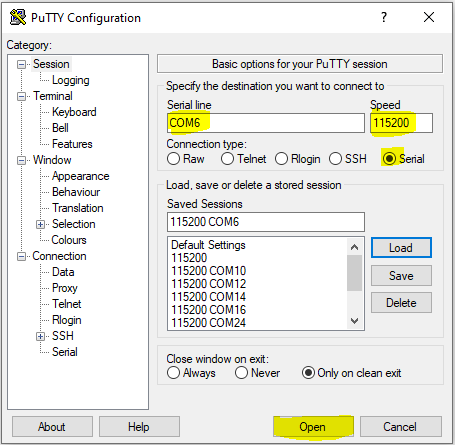

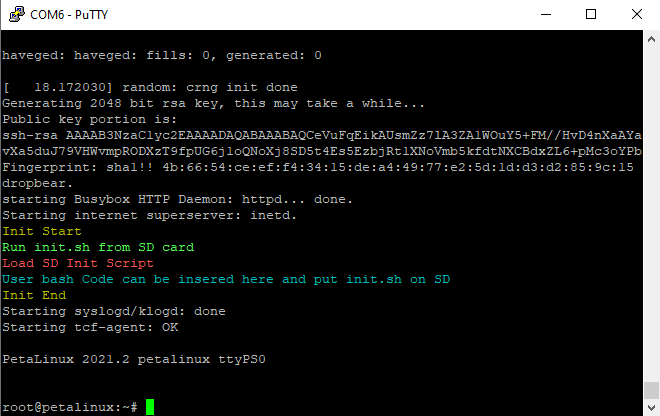

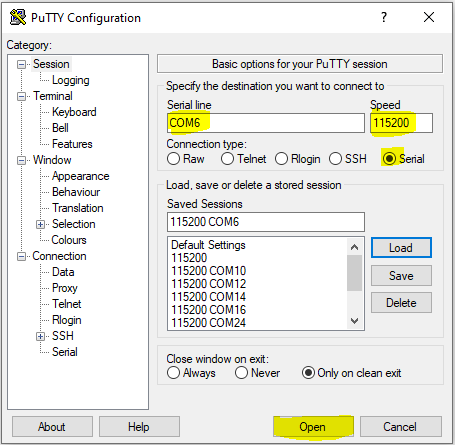

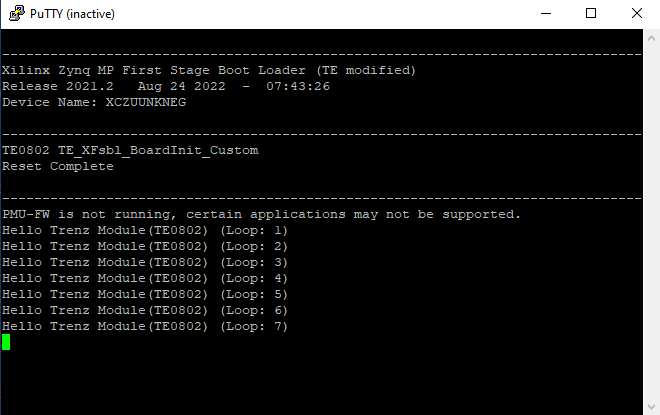

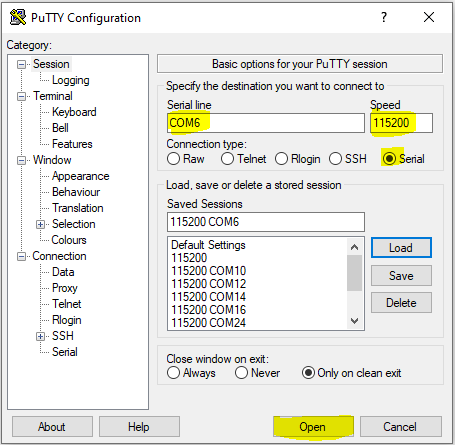

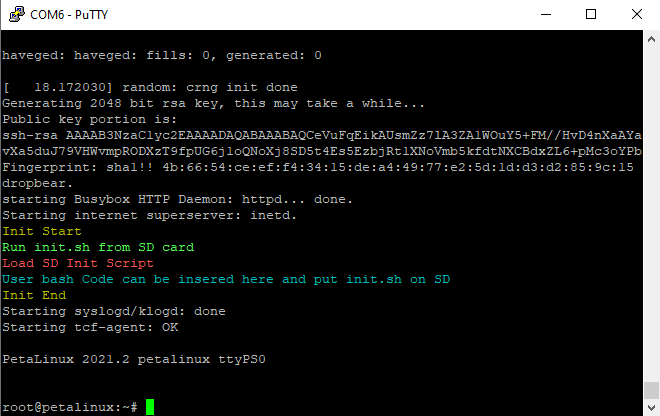

In case the QSPI Flash is loaded with the reference design, you can connect to the board with a program like PuTTY. Just open up a serial session with baudrate of 115200 and the right COM - port (visible in Device Manager).

| Scroll Title |

|---|

| anchor | Figure_VHM |

|---|

| title-alignment | center |

|---|

| title | Terminal example |

|---|

|

Image Removed Image Removed Image Removed Image Removed

|

2.2 TE0802 Hardware Setup and Power up in SD-Boot mode (Linux)

|

Image Added Image Added Image Added Image Added

|

Boot process

Zynq Boot ROM loads FSBL from QSPI into OCM,

- FSBL init PS, programs PL using the bitstream and loads U-boot from QSPI into DDR,

- U-boot loads Linux (image.ub) from SD into DDR

- For usage instructions please refer to chapter Linux application

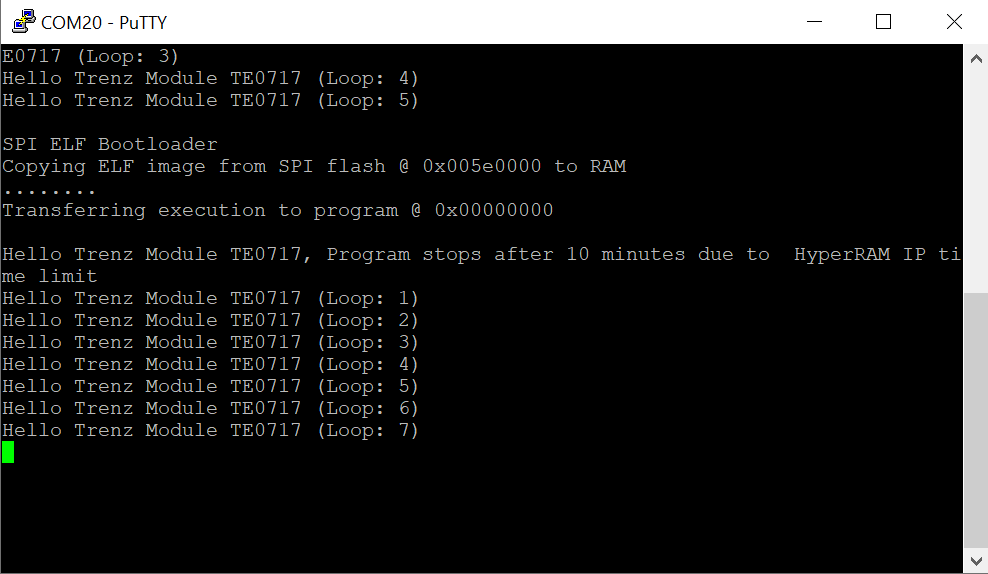

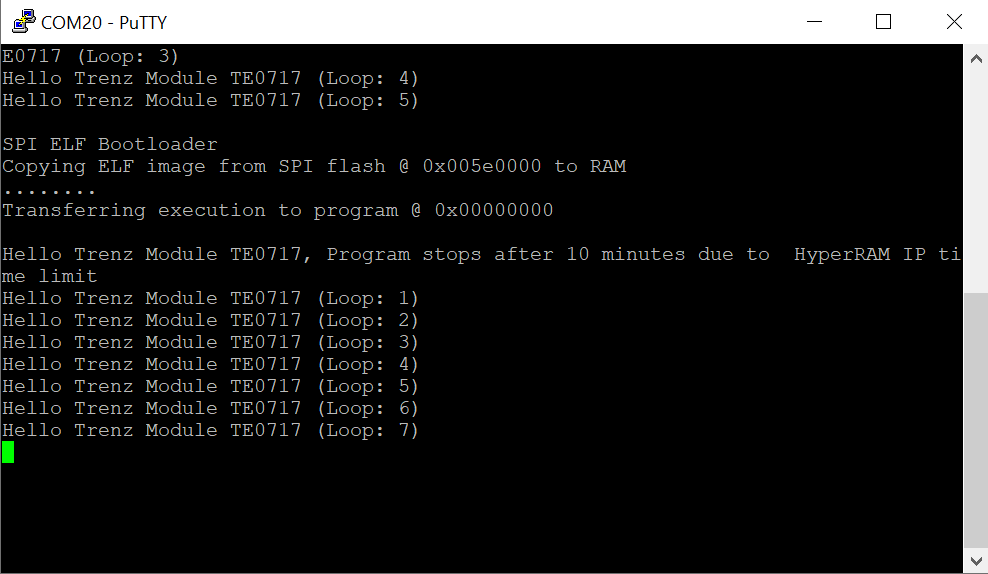

'Hello Trenz' in QSPI-Boot mode

- Connect the MicroUSB cable from your module board with your PC

Connect the module board with the power supply (5V)

Power on module board

Program 'hello_te0802' application on QSPI flash

| Code Block |

|---|

| language | bash |

|---|

| theme | Midnight |

|---|

| title | run on Vivado TCL (Script programs BOOT.bin on QSPI flash) |

|---|

|

TE::pr_program_flash -swapp hello_te0802 |

Switch the DIP-Switch S1 to QSPI-Boot mode:

| S1.1 | S1.2 | S1.3 | S1.4 |

|---|

| ON | OFF | OFF | OFF |

Restart the module board

| Scroll Title |

|---|

| anchor | Figure_VHM |

|---|

| title-alignment | center |

|---|

|

Image Removed Image Removed

|

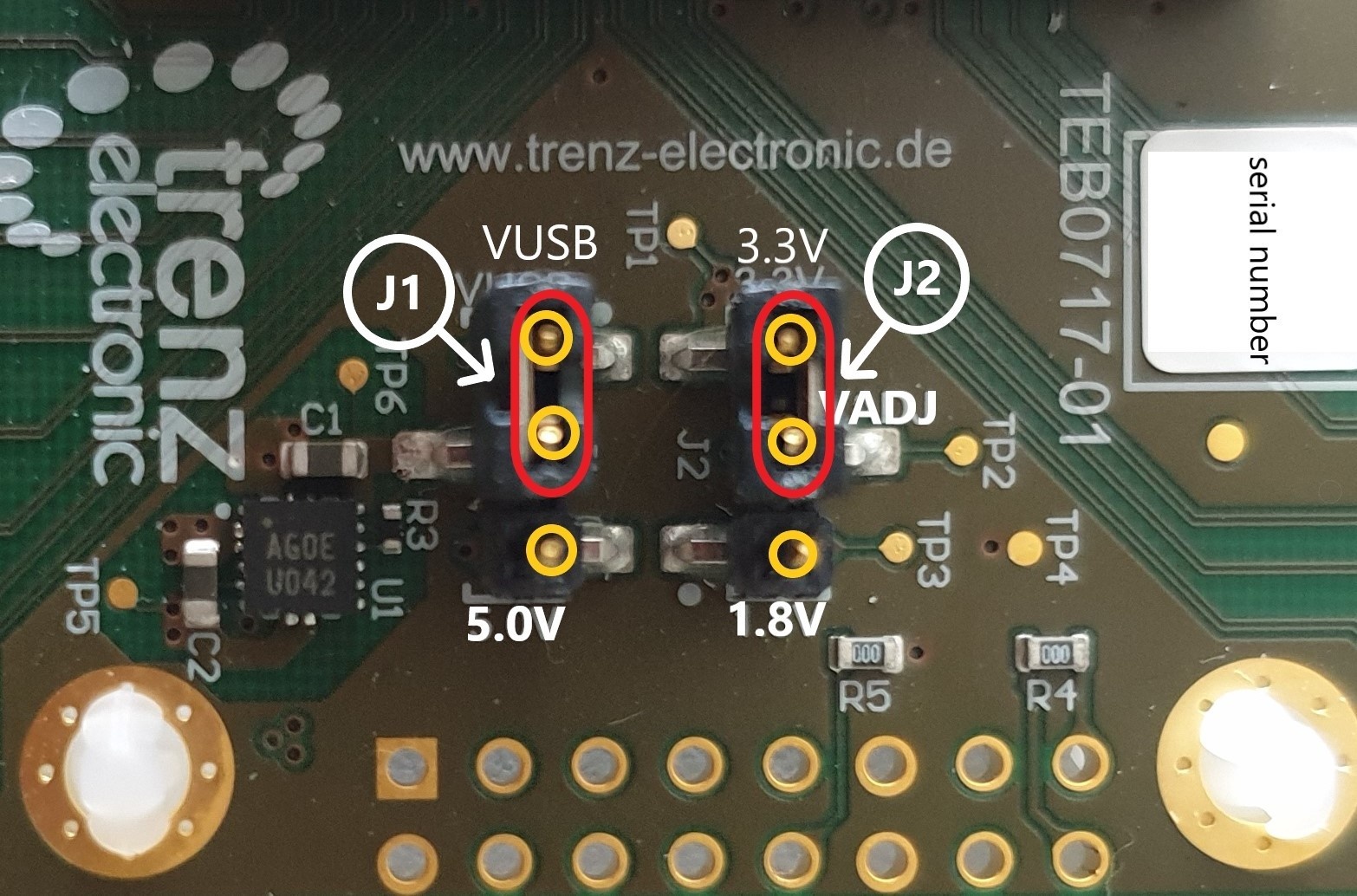

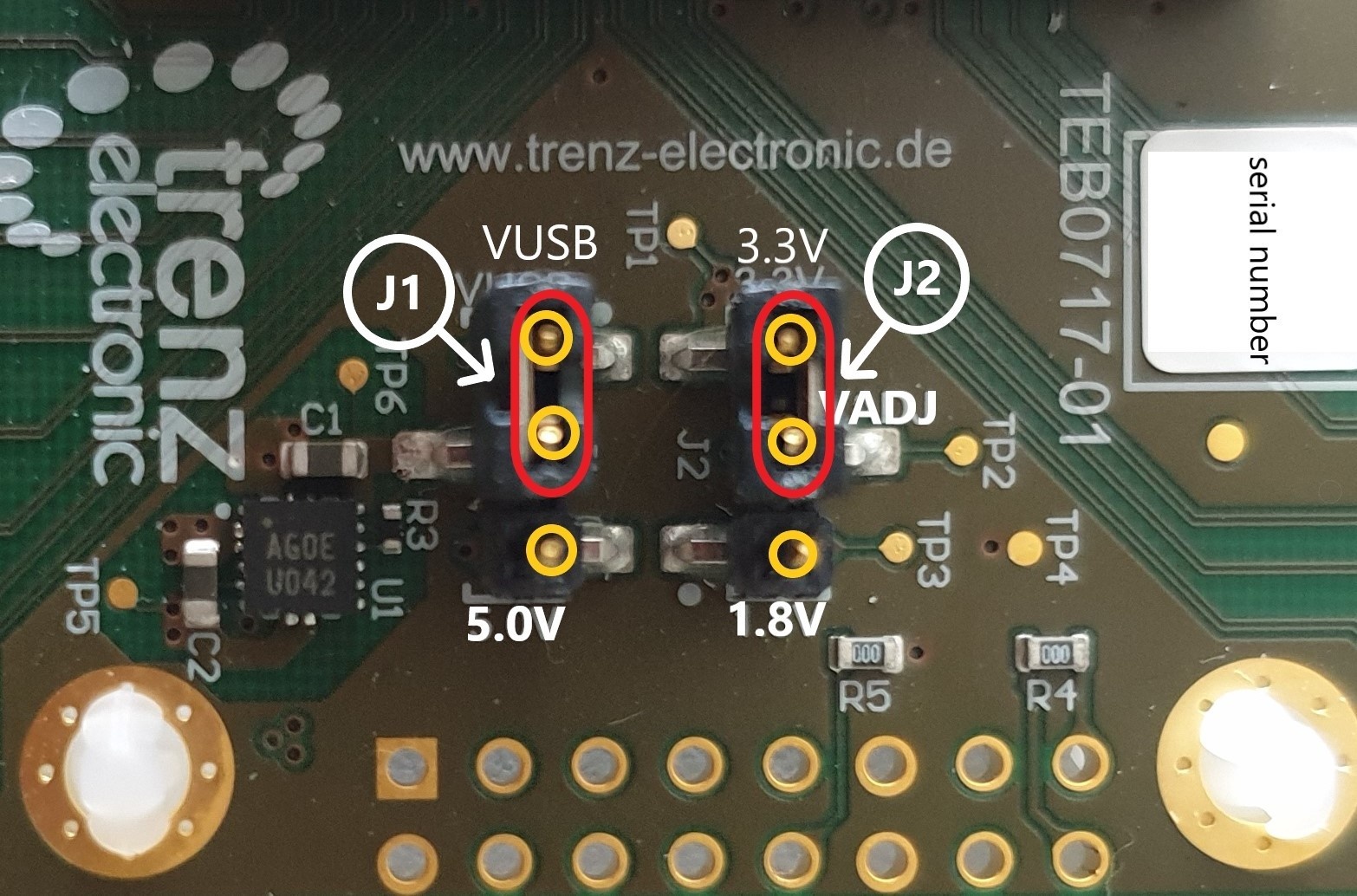

The Voltage set with Jumper J1 determines the source of the input voltage for the voltages regulator chip U1 to the left of J1. Either 5V from the MicroUSB port (VUSB) or 5V from pin header J4.

With the shown setting of Jumper J2 the voltage VADJ is set to 3.3V that comes from the carriers voltage regulator chip U1. The 1.8V comes from the module. The Voltage VADJ is wired to the module and is used as the BANK34 supply voltage.

- Use a MicroUSB cable to connect your board to the PC.cc

All the LEDs are simply routed to the FPGA, hence none of them should be turned on. If the qspi flash on the module is preloaded with a design though, it might be that some LEDs are blinking.

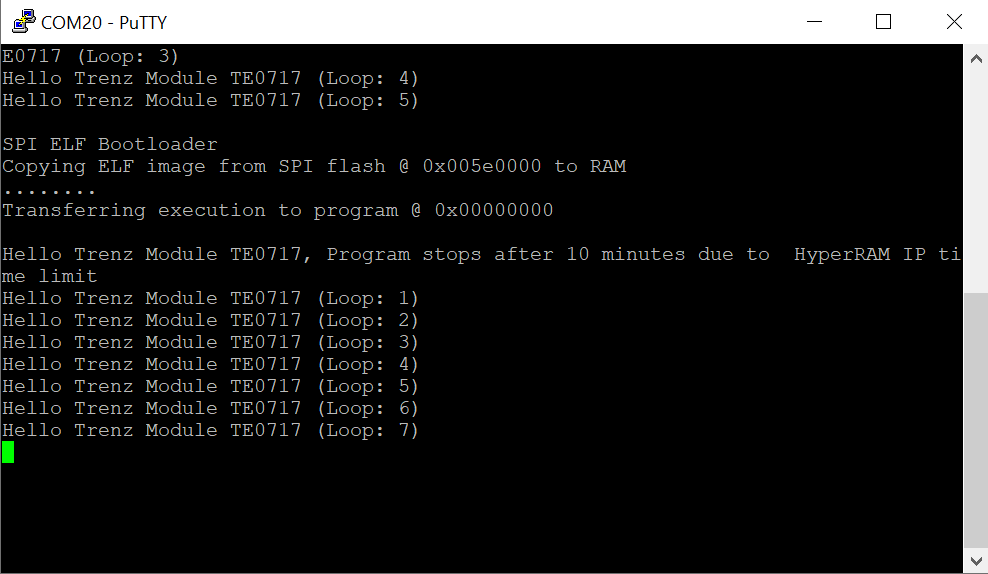

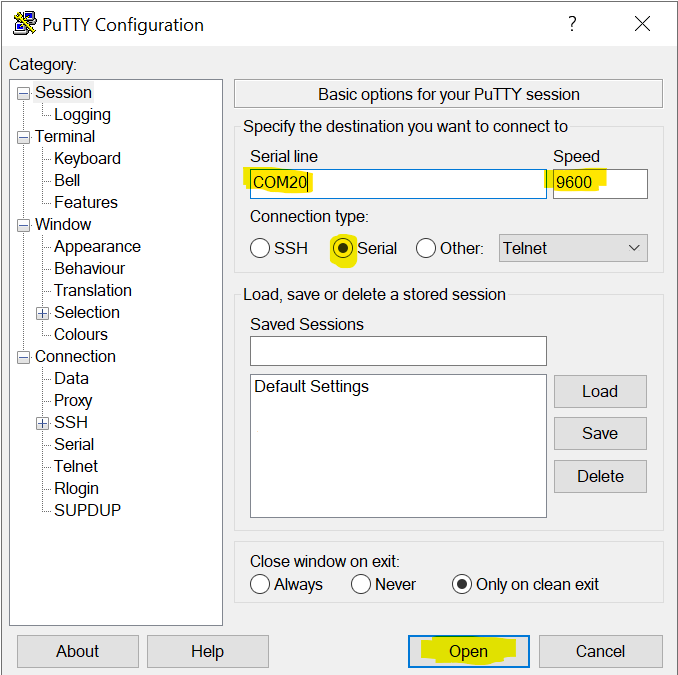

In case the QSPI Flash is loaded with the reference design, you can connect to the board with a program like PuTTY. Just open up a serial session with baud-rate baudrate of 9600 115200 and the right COM-port (visible in Device Manager).

You may need to press the RESET-button.

| Scroll Title |

|---|

| anchor | Figure_VHM |

|---|

| title-alignment | center |

|---|

|  Image Removed

Image Removed Image Removed

Image Removed |

Figure 4: Terminal(MicroBlaze output)

2.2 Reference Design - Introduction

| Page properties |

|---|

|

ACHTUNG!!! Hier soll noch entschieden werden, ob hier nur kurz auf das Referenzdesign eingegangen wird und die Inhalte im public doc - test board Beschreibung reingenommen werden bzw ... was hier überhaupt noch sinnvoll reingehört ? |

We provide a reference design that interacts with most of the peripheral on the module. The provided design "TE0802 test board" shows how to connect the different parts of the module to simplify the development of your own application. You can use it for your own design but keep in mind the overall FPGA resources and power consumption before deployment.

The reference design we are introducing in this guide is "TE0802 test board". The most important steps to get it up and running are explained on TE0802 Test Board. The Download is available here.

The reference design is only usable with the specified Vivado/Vitis version. Always use the same version of Xilinx Software for one Project. (e.g. use reference design 2021.2.1 with vitis installation 2021.2.1)

The components of the reference design are illustrated in the following figure: |

Image Added Image Added Image Added Image Added

|

Hardware Setup and Power up in SD-Boot mode

| Scroll Ignore |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

|

|

Linux in SD-Boot mode

- Download the source code and configuration files for "TE0802 test_board" reference design. Ensure that your download files match your Vivado version.

Run _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

| Code Block |

|---|

| language | bash |

|---|

| theme | Midnight |

|---|

| title | _create_win_setup.cmd/_create_linux_setup.sh |

|---|

|

------------------------Set design paths----------------------------

-- Run Design with: _create_win_setup

-- Use Design Path: <absolute project path>

--------------------------------------------------------------------

-------------------------TE Reference Design---------------------------

--------------------------------------------------------------------

-- (0) Module selection guide, project creation...prebuilt export...

-- (1) Create minimum setup of CMD-Files and exit Batch

-- (2) Create maximum setup of CMD-Files and exit Batch

-- (3) (internal only) Dev

-- (4) (internal only) Prod

-- (c) Go to CMD-File Generation (Manual setup)

-- (d) Go to Documentation (Web Documentation)

-- (g) Install Board Files from Xilinx Board Store (beta)

-- (a) Start design with unsupported Vivado Version (beta)

-- (x) Exit Batch (nothing is done!)

----

Select (ex.:'0' for module selection guide): |

- Press '0' and enter to start "Module Selection Guide"

- Select your assembly version

- validate selection

- press '1' and enter to "create and open delivery binary folder"

- Connect the MicroUSB cable from your module board with your PC

- Connect peripherals to devices

- VGA, display port → monitor

- USB → keyboard

- ...

- Connect the module board with the power supply (5V)

- Copy BOOT.bin, image.ub, init.sh and boot.scr on SD card (e.g. <project folder>\test_board\_binaries_TE0802-02-2AEV2-A\boot_linux)

Switch the DIP-Switch S1 to SD-Boot mode

| S1.1 | S1.2 | S1.3 | S1.4 |

|---|

| ON | ON | OFF | OFF |

- Insert the SD card into the module board

Power on the module board

You can connect to the board with a program like PuTTY. Just open up a serial session with baudrate of 115200 and the right COM port (visible in Device Manager).

BD| VHM | | title-alignment | center |

|---|

| title |

|---|

|

Block Design |  Image Removed Image Removed |

|

Image Added Image Added Image Added Image Added

|

Boot process

Zynq Boot ROM loads FSBL from SD into OCM,

- FSBL init PS, programs PL using the bitstream and loads U-boot from SD into DDR,

- U-boot loads Linux (image.ub) from SD into DDR

- For usage instructions please refer to chapter Linux application

Linux Application

| Scroll Ignore |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

|

|

After the Linux boot is complete, you can use the Linux shell and the connected peripherals

I2C

| Code Block |

|---|

| language | bash |

|---|

| theme | Midnight |

|---|

| title | use linux shell |

|---|

|

i2cdetect -l (Shows a list of the available I2C buses)

i2cdetect -y -r 1 (check I2C 1 Bus) |

Real Time Clock (RTC)

| Code Block |

|---|

| language | bash |

|---|

| theme | Midnight |

|---|

| title | use linux shell |

|---|

|

dmesg | grep rtc (RTC check)

hwclock --test |

Ethernet

| Code Block |

|---|

| language | bash |

|---|

| theme | Midnight |

|---|

| title | use linux shell |

|---|

|

udhcpc (ETH0 check)

ifconfig (shows the configuration of the network interface) |

USB

| Code Block |

|---|

| language | bash |

|---|

| theme | Midnight |

|---|

| title | use linux shell |

|---|

|

lsusb (USB check) |

PCIe (M.2 SSD)

| Code Block |

|---|

| language | bash |

|---|

| theme | Midnight |

|---|

| title | use linux shell |

|---|

|

lspci (PCIe check) |

Audio

| Code Block |

|---|

| language | bash |

|---|

| theme | Midnight |

|---|

| title | use linux shell |

|---|

|

aplay /<link to mounted sd card>/<filename>.wav (e.g. aplay /run/mount/sd/<filename>.wav) |

| Info |

|---|

Display Port must be connected to activate audio drivers. Use .wav or other aplay supported formate

|

VGA

- connect VGA to monitor and adjust source (it shows test pattern)

Display Port

- second linux console output will be shown on the monitor, when boot process is finished.

- connect keyboard to TE0802 USB, to interact with the second console

- petalinux login: root

- password: root

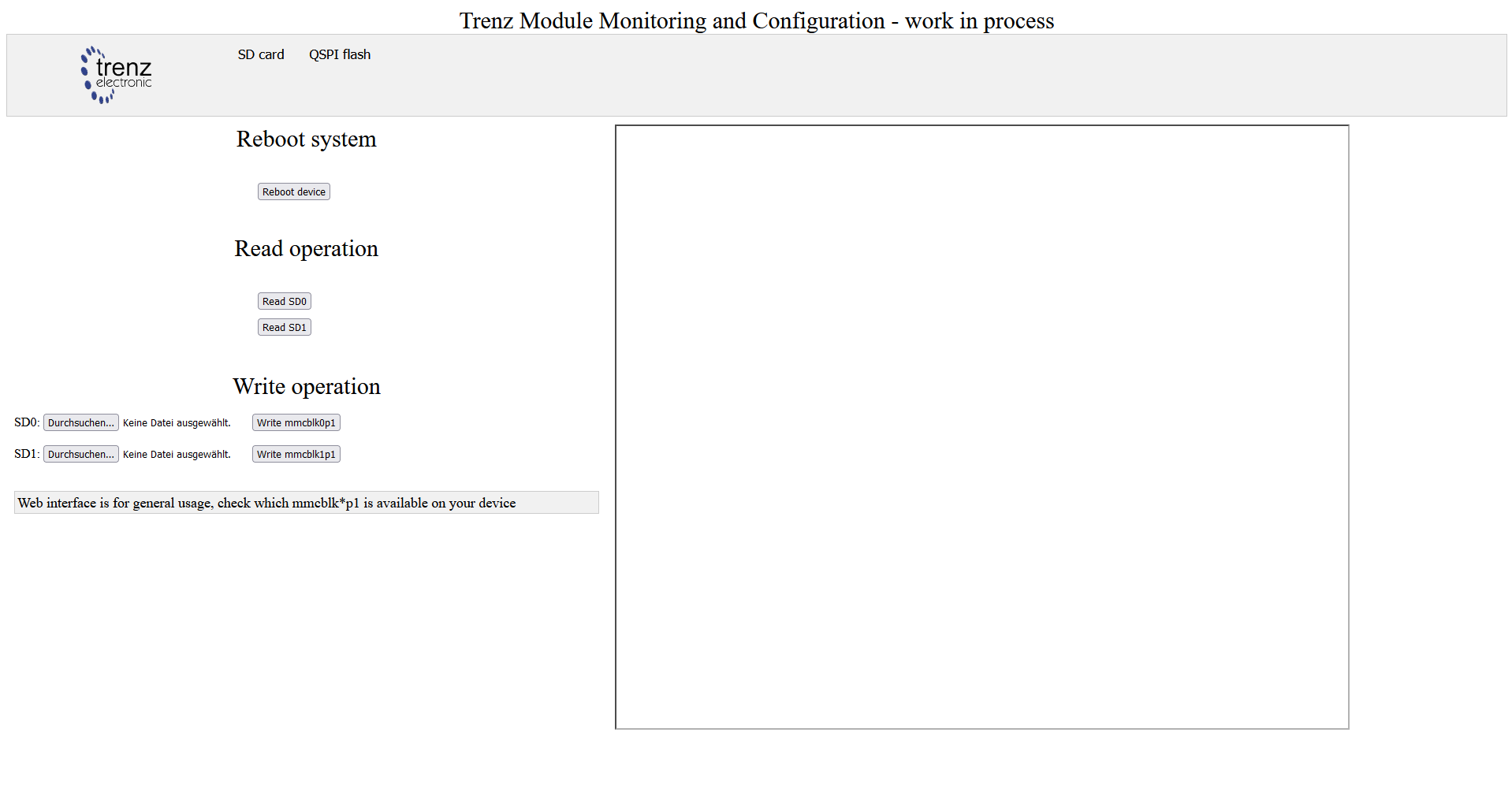

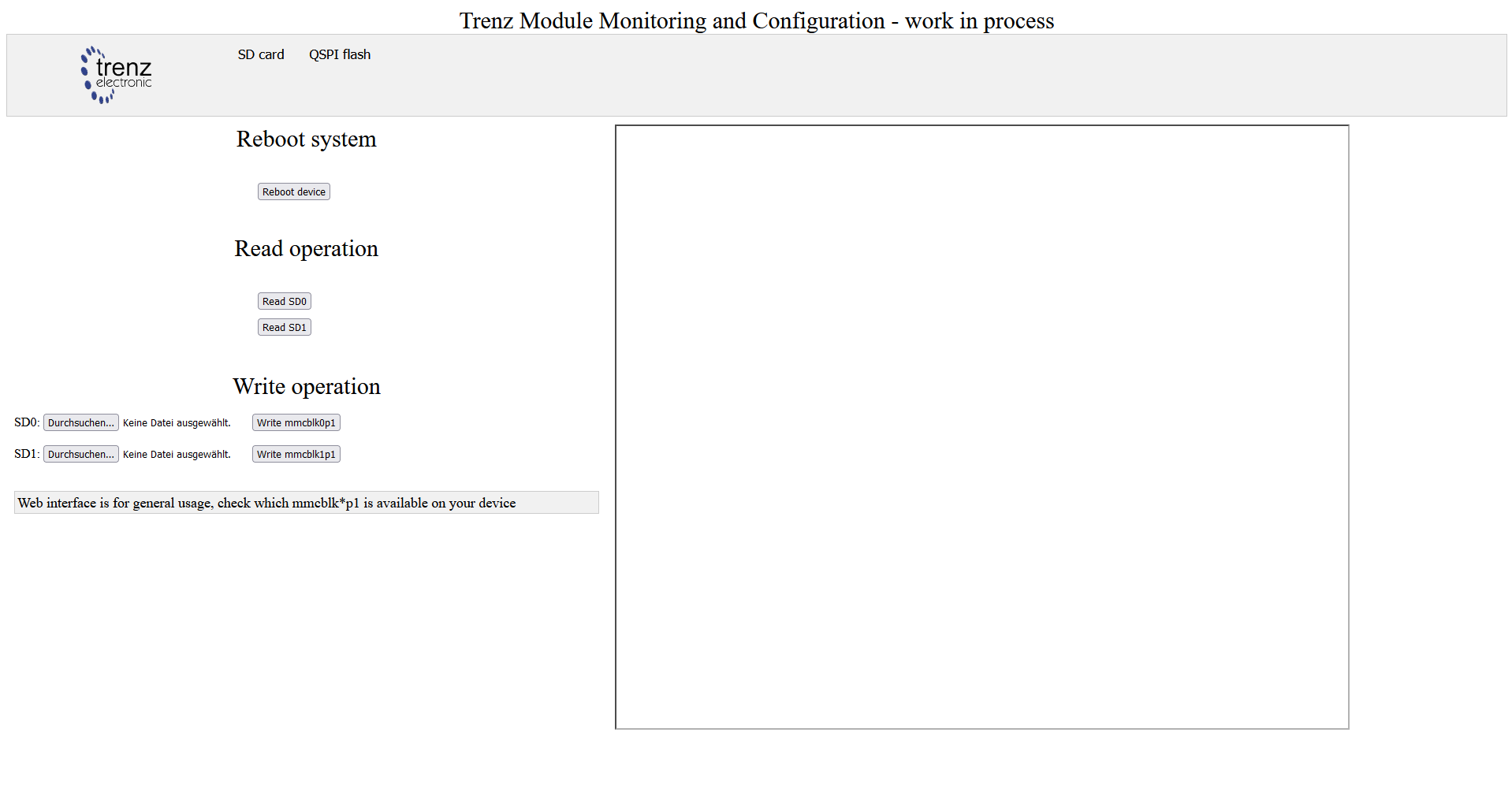

Webserver

| Expand |

|---|

| title | insert IP on web browser to start web interface |

|---|

|

Image Added Image Added |

Startup Script

- If there is a start script named 'init.sh' on the SD card, it is loaded and executed shortly before the Linux boot process is completed.

- User bash code can be inserted on 'init.sh'

userLEDs

- The user LEDs indicate a binary counter, which is reset by pressing one of the cross buttons

7-Segment LCD Display

- LCD is connected to counter

DIP-Switch

- Determines the reset start value from the binary counter of userLEDs

| Scroll Title |

|---|

| anchor | Figure_VHM |

|---|

| title-alignment | center |

|---|

|

Image Removed Image Removed

|

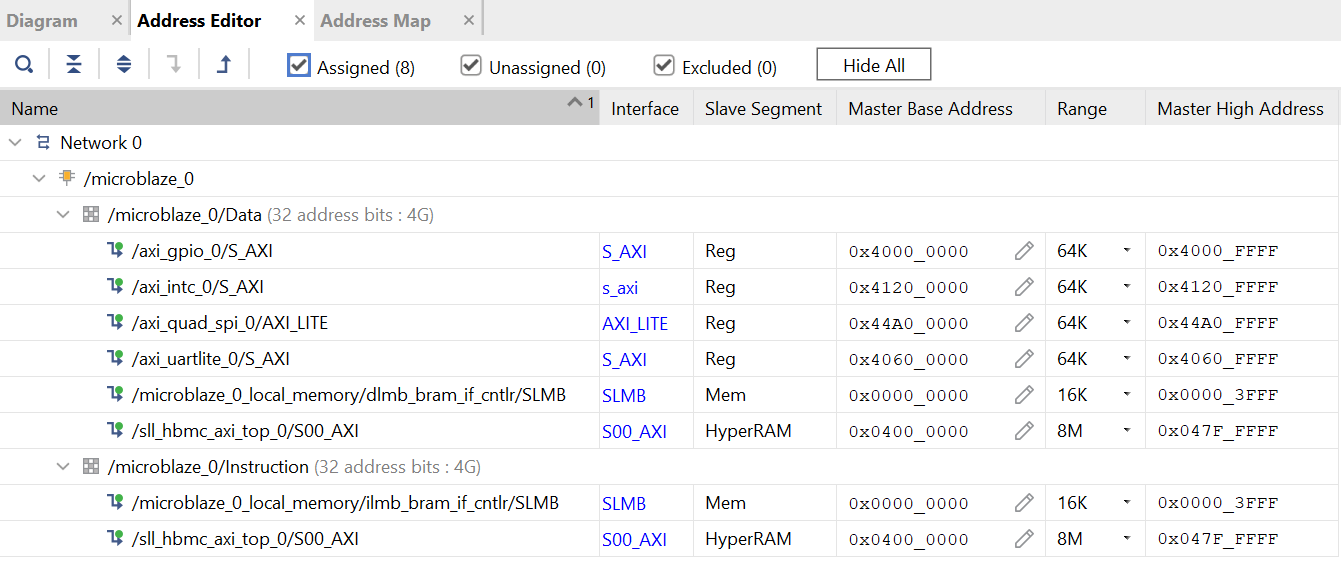

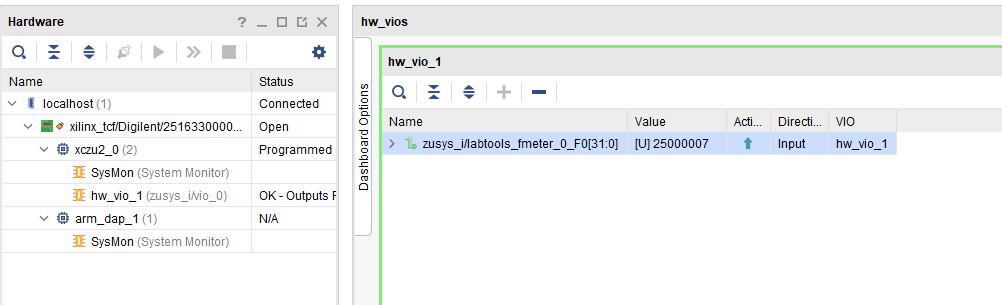

Figure 6: Vivado Address Editor - Address Mapping

For example the AXI GPIO IP Core which has a LED1 connected to it, can be controlled with software(C/C++) by raising the bits mapped to the address 0x4000 0000.

The VIO Core enables you to control connected IOs via the Vivado Hardware Manager(like LED2).

3 Notes

Document Revision History

| Expand |

|---|

|

| Scroll Title |

|---|

| anchor | Table_DRH |

|---|

| title-alignment | center |

|---|

| title | Revision history. |

|---|

| | Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| widths | 2*,*,3*,4* |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Version | Description | Authors |

|---|

| Page info |

|---|

| modified-date |

|---|

| modified-date |

|---|

| dateFormat | yyyy-MM-dd |

|---|

|

| | Page info |

|---|

| infoType | Current version |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| prefix | 1. |

|---|

| type | Flat |

|---|

|

| | | Page info |

|---|

| infoType | Modified by |

|---|

| type | Flat |

|---|

|

| | -- | all |

| | Page info |

|---|

| infoType | Modified users |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| type | Flat |

|---|

|

|

|

|

custom_table_size_100

Image Added

Image Added Image Removed

Image Removed Image Removed

Image Removed Image Added

Image Added Image Added

Image Added Image Removed

Image Removed Image Removed

Image Removed Image Added

Image Added Image Added

Image Added Image Removed

Image Removed Image Added

Image Added Image Added

Image Added Image Added

Image Added Image Added

Image Added