- Created by Manuela Strücker, last modified on 08 09, 2022

You are viewing an old version of this page. View the current version.

Compare with Current View Page History

« Previous Version 2 Next »

1 Overview

This guide shows the main components of the TE0802 module and introduces the first steps to get the provided reference design up and running.

This module TE00802 has a Xilinx Zynq Ultrascale+ and several hardware features onboard that allows you to create digital hardware and software designs. For communication and configuration the module board offers a JTAG/UART Interface.

1.1 Prerequisites

| Hardware | Software |

|---|---|

|

|

1.2 Documentation

- Official links to the shop:

- Technical Reference Manual:

- Resources & Reference Designs:

1.3 Hardware Features

| TE0802-02-1AEV2-A | TE0802-02-2AEV2-A | |

|---|---|---|

| MPSoC | Xilinx Zynq UltraScale+

| Xilinx Zynq UltraScale+

|

| Storage |

| |

| Display |

| |

| Audio |

| |

| Connectors |

| |

| Communication & Debug |

| |

| Input |

| |

Information on IO routing and FPGA pin connections can be found in the

2 Board Power-Up

2.1 TE0802 Hardware Setup and Power up in QSPI-Boot mode (simple Hello Trenz application)

- Download the source code and configuration files for "TE0802 test_board" reference design. Ensure that your download files match your Vivado version.

- Check the settings from DIP-Switch S1 (JTAG):

S1.1 S1.2 S1.3 S1.4 OFF OFF OFF OFF

- Connect the MicroUSB cable from your module board with your PC

- Connect the module board with the power supply (5V)

- Power on module board

Run _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

_create_win_setup.cmd/_create_linux_setup.sh------------------------Set design paths---------------------------- -- Run Design with: _create_win_setup -- Use Design Path: <absolute project path> -------------------------------------------------------------------- -------------------------TE Reference Design--------------------------- -------------------------------------------------------------------- -- (0) Module selection guide, project creation...prebuilt export... -- (1) Create minimum setup of CMD-Files and exit Batch -- (2) Create maximum setup of CMD-Files and exit Batch -- (3) (internal only) Dev -- (4) (internal only) Prod -- (c) Go to CMD-File Generation (Manual setup) -- (d) Go to Documentation (Web Documentation) -- (g) Install Board Files from Xilinx Board Store (beta) -- (a) Start design with unsupported Vivado Version (beta) -- (x) Exit Batch (nothing is done!) ---- Select (ex.:'0' for module selection guide):

- Press '0' and enter to start "Module Selection Guide"

- Select your assembly version

- validate selection

- press '1' and enter to "create Vivado project"

Program 'hello_te0802' application on QSPI flash

run on Vivado TCL (Script programs BOOT.bin on QSPI flash)TE::pr_program_flash -swapp hello_te0802

Restart the module board

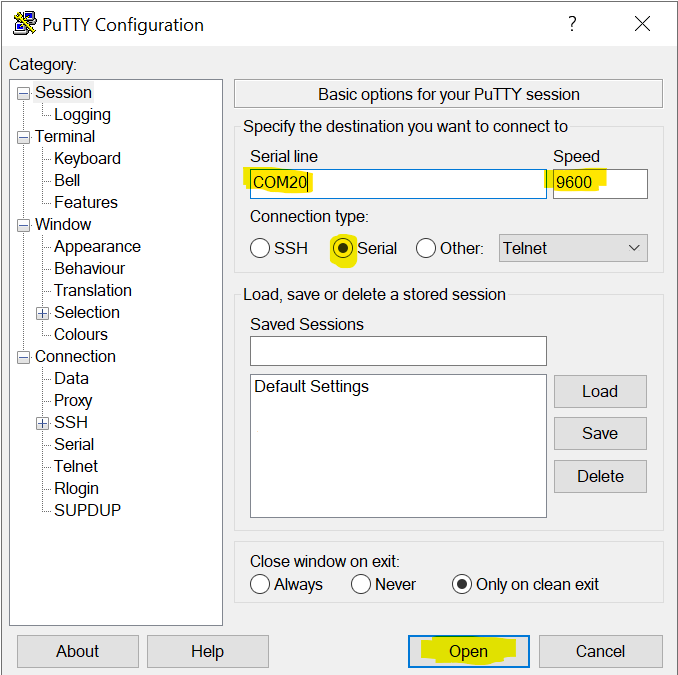

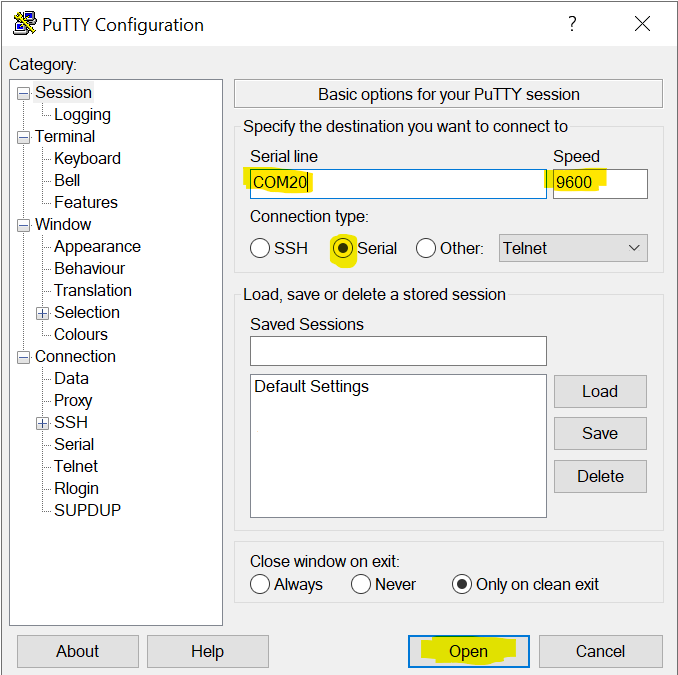

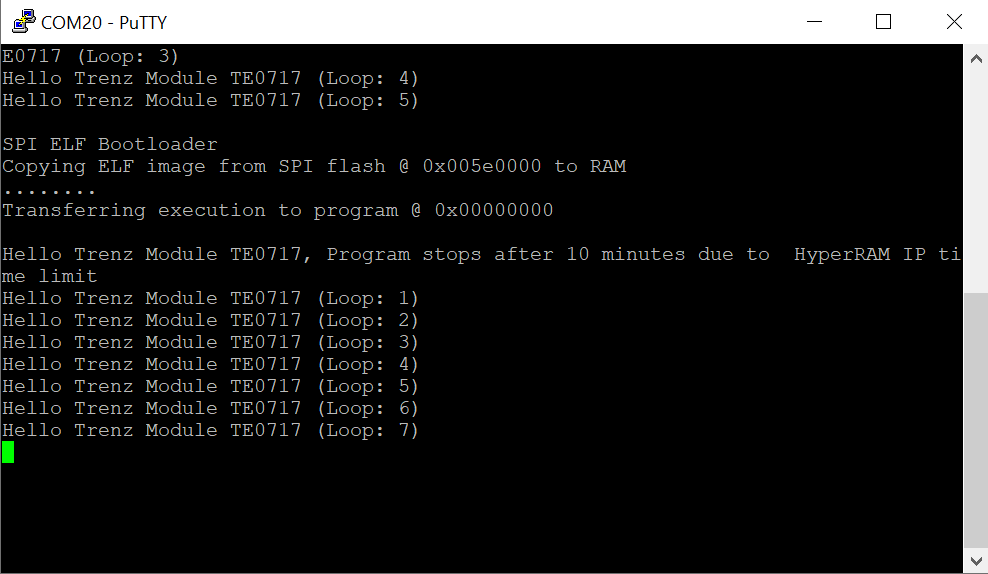

In case the QSPI Flash is loaded with the reference design, you can connect to the board with a program like PuTTY. Just open up a serial session with baudrate of 115200 and the right COM-port (visible in Device Manager).

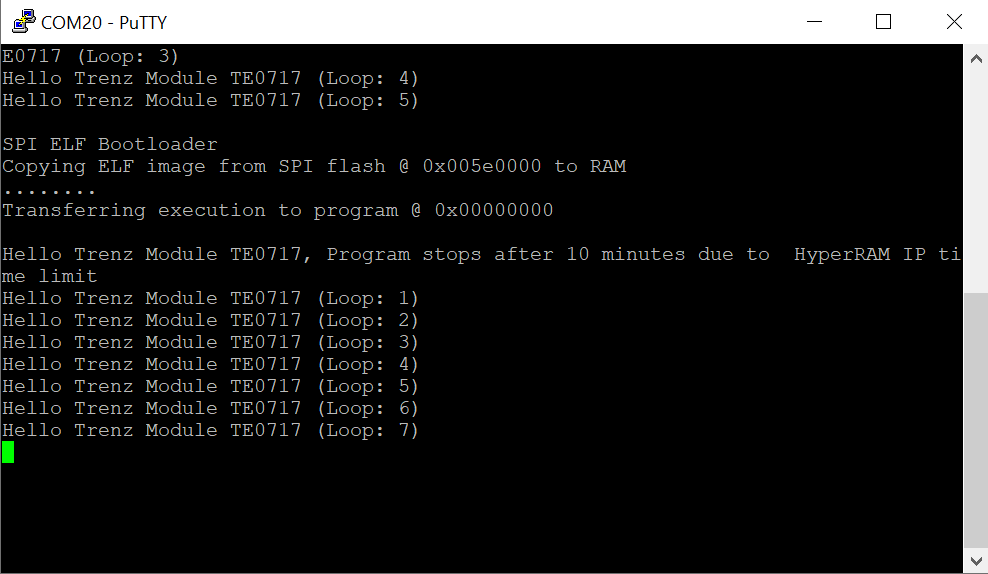

Terminal example

Terminal example

2.2 TE0802 Hardware Setup and Power up in SD-Boot mode (Linux)

Check the settings from DIP-Switch S1:

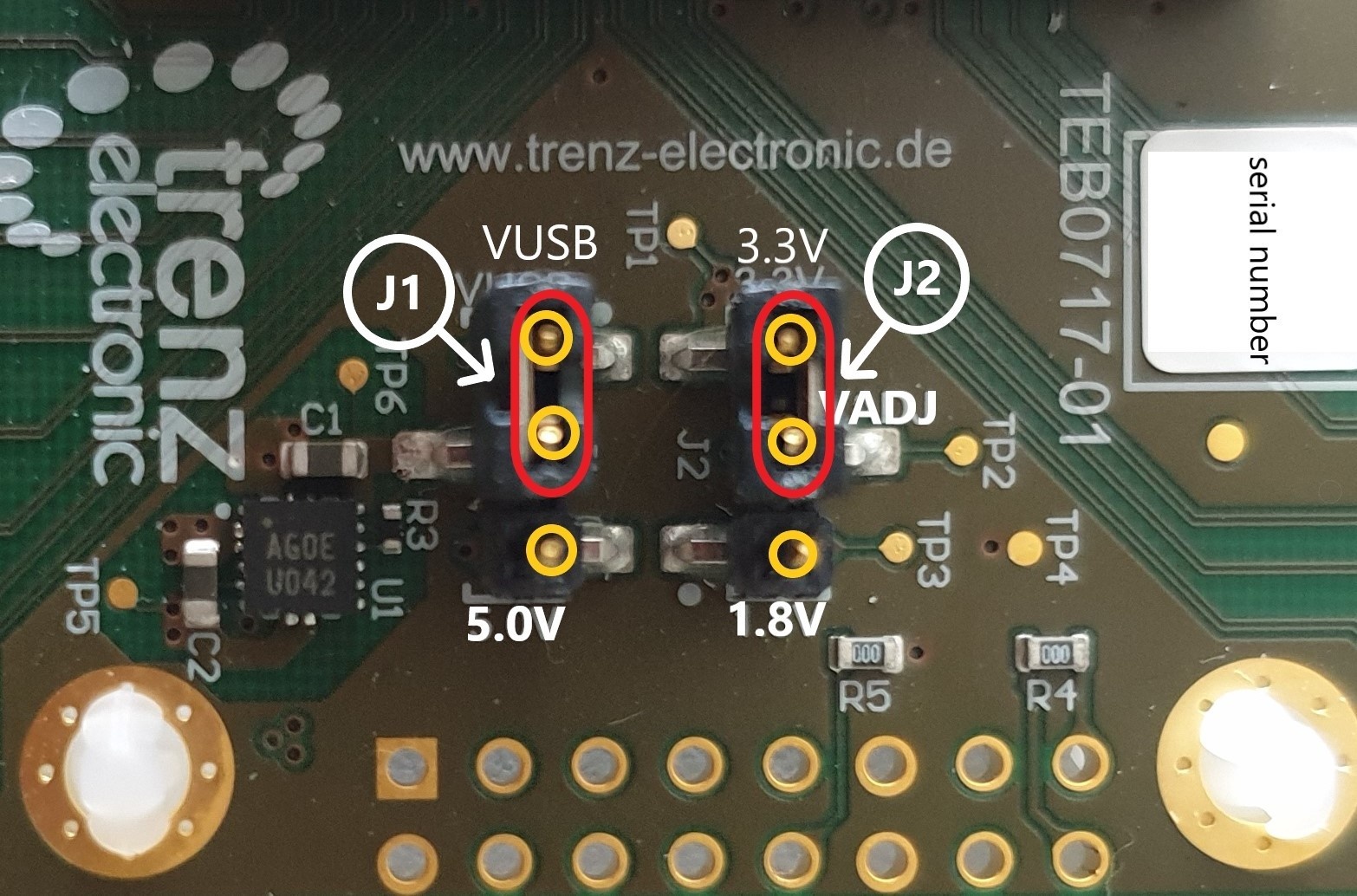

The Voltage set with Jumper J1 determines the source of the input voltage for the voltages regulator chip U1 to the left of J1. Either 5V from the MicroUSB port (VUSB) or 5V from pin header J4.

With the shown setting of Jumper J2 the voltage VADJ is set to 3.3V that comes from the carriers voltage regulator chip U1. The 1.8V comes from the module. The Voltage VADJ is wired to the module and is used as the BANK34 supply voltage.

- Use a MicroUSB cable to connect your board to the PC.cc

All the LEDs are simply routed to the FPGA, hence none of them should be turned on. If the qspi flash on the module is preloaded with a design though, it might be that some LEDs are blinking.

In case the QSPI Flash is loaded with the reference design, you can connect to the board with a program like PuTTY. Just open up a serial session with baud-rate of 9600 and the right COM-port (visible in Device Manager).

You may need to press the RESET-button.

Figure 4: Terminal(MicroBlaze output)

2.2 Reference Design - Introduction

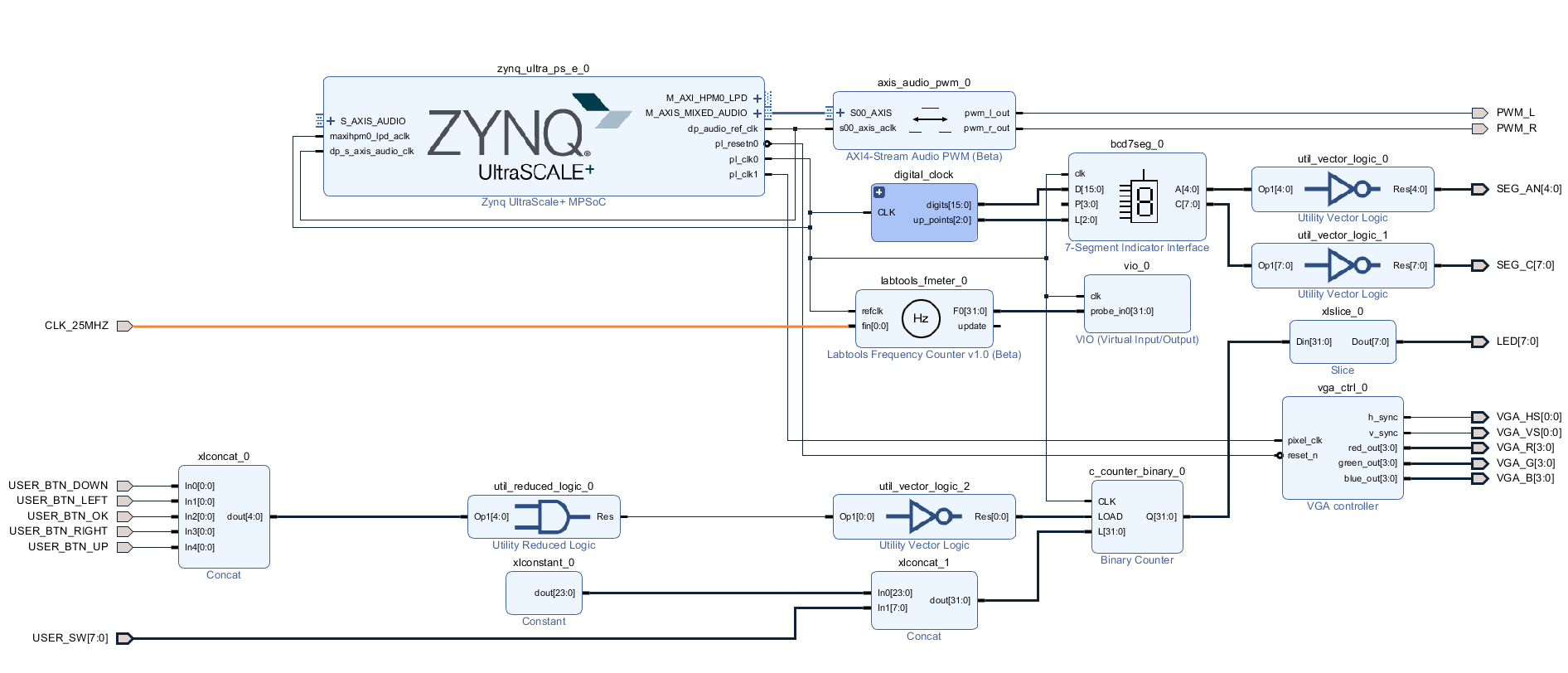

We provide a reference design that interacts with most of the peripheral on the module. The provided design "TE0802 test board" shows how to connect the different parts of the module to simplify the development of your own application. You can use it for your own design but keep in mind the overall FPGA resources and power consumption before deployment.

The reference design we are introducing in this guide is "TE0802 test board". The most important steps to get it up and running are explained on TE0802 Test Board. The Download is available here.

The reference design is only usable with the specified Vivado/Vitis version. Always use the same version of Xilinx Software for one Project. (e.g. use reference design 2021.2.1 with vitis installation 2021.2.1)

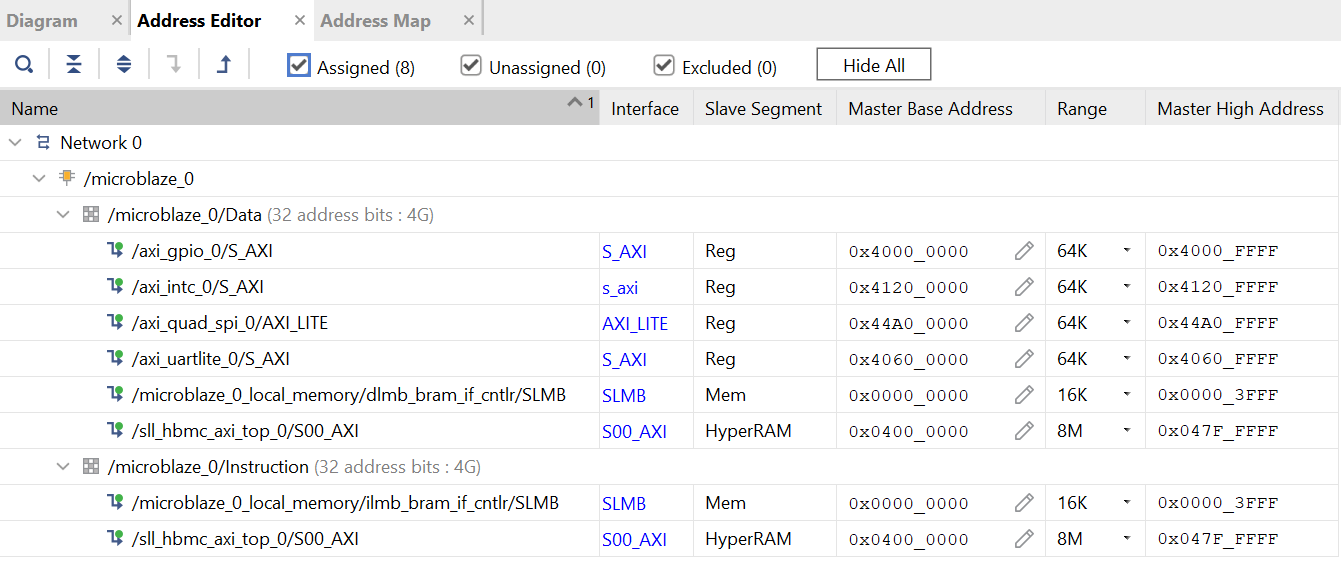

The components of the reference design are illustrated in the following figure:

Figure 6: Vivado Address Editor - Address Mapping

For example the AXI GPIO IP Core which has a LED1 connected to it, can be controlled with software(C/C++) by raising the bits mapped to the address 0x4000 0000.

The VIO Core enables you to control connected IOs via the Vivado Hardware Manager(like LED2).

3 Notes

Document Revision History

| Date | Version | Description | Authors |

|---|---|---|---|

Error rendering macro 'page-info' Ambiguous method overloading for method jdk.proxy241.$Proxy3497#hasContentLevelPermission. Cannot resolve which method to invoke for [null, class java.lang.String, class com.atlassian.confluence.pages.Page] due to overlapping prototypes between: [interface com.atlassian.confluence.user.ConfluenceUser, class java.lang.String, class com.atlassian.confluence.core.ContentEntityObject] [interface com.atlassian.user.User, class java.lang.String, class com.atlassian.confluence.core.ContentEntityObject] | Error rendering macro 'page-info' Ambiguous method overloading for method jdk.proxy241.$Proxy3497#hasContentLevelPermission. Cannot resolve which method to invoke for [null, class java.lang.String, class com.atlassian.confluence.pages.Page] due to overlapping prototypes between: [interface com.atlassian.confluence.user.ConfluenceUser, class java.lang.String, class com.atlassian.confluence.core.ContentEntityObject] [interface com.atlassian.user.User, class java.lang.String, class com.atlassian.confluence.core.ContentEntityObject] |

| Error rendering macro 'page-info' Ambiguous method overloading for method jdk.proxy241.$Proxy3497#hasContentLevelPermission. Cannot resolve which method to invoke for [null, class java.lang.String, class com.atlassian.confluence.pages.Page] due to overlapping prototypes between: [interface com.atlassian.confluence.user.ConfluenceUser, class java.lang.String, class com.atlassian.confluence.core.ContentEntityObject] [interface com.atlassian.user.User, class java.lang.String, class com.atlassian.confluence.core.ContentEntityObject] |

| -- | all | Error rendering macro 'page-info' Ambiguous method overloading for method jdk.proxy241.$Proxy3497#hasContentLevelPermission. Cannot resolve which method to invoke for [null, class java.lang.String, class com.atlassian.confluence.pages.Page] due to overlapping prototypes between: [interface com.atlassian.confluence.user.ConfluenceUser, class java.lang.String, class com.atlassian.confluence.core.ContentEntityObject] [interface com.atlassian.user.User, class java.lang.String, class com.atlassian.confluence.core.ContentEntityObject] |

Table of contents

- No labels