Page History

...

| HTML |

|---|

<!-- Template Revision 1.64 (HTML comments will be not displayed in the document, no need to remove them. For Template/Skeleton changes, increase Template Revision number. So we can check faster, if the TRM style is up to date). --> |

| Scroll Ignore |

|---|

| Scroll pdf ignore | |

|---|---|

Table of Contents

|

Overview

| Scroll Only (inline) |

|---|

Refer to https://wiki.trenz-electronic.de/display/PD/TE0715+TRM for online version of this manual and the rest of available documentation. |

The Trenz Electronic TE0715 is an industrial-grade SoM (System on Module) based on Xilinx Zynq-7000 SoC (XC7Z015 or XC7Z030) with 1GByte of DDR3 SDRAM, 32MBytes of SPI Flash memory, Gigabit Ethernet PHY transceiver, a USB PHY transceiver and powerful switching-mode power supplies for all on-board voltages. A large number of configurable I/Os is provided via rugged high-speed stacking strips.

...

Industrial-grade Xilinx Zynq-7000 SoC (XC7Z015, XC7Z030)

- Rugged for shock and high vibration

- 2 × ARM Cortex-A9

- 10/100/1000 Mbps Ethernet transceiver PHY

- MAC address EEPROM

- 32-bit wide 1GB DDR3 SDRAM

- 32 MByte quad SPI Flash memory

- Programmable clock generator

- Transceiver clock (default 125 MHz)

- Plug-on module with 2 × 100-pin and 1 × 60-pin high-speed hermaphroditic strips

- 132 FPGA I/Os (65 LVDS pairs possible) and 14 PS MIO available on B2B connectors

- 4 GTP/GTX (high-performance transceiver) lanes

- GTP/GTX (high-performance transceiver) clock input

- USB 2.0 high-speed ULPI transceiver

- On-board high-efficiency DC-DC converters

- 4 A x 1.0 V power rail

- 3 A x 1.0 V power rail

- 3 A x 1.2 V power rail

- 3 5 A x 1.5 35 V power rail

- 1.5 3 A x 1.8 V power rail

- System management

- eFUSE bit-stream encryption

- AES bit-stream encryption

- Temperature compensated RTC (real-time clock)

- User LED

- Evenly-spread supply pins for good signal integrity

...

Table 4: MGT lanes overview.

Below are listed MGT bank reference clock sources.

...

JTAG access to the Xilinx Zynq -7000 SoC is provided through B2B connector JM2.

...

Table 6: JTAG interface signals.

| Note |

|---|

| JTAGEN pin in B2B connector JM1 should be kept low or grounded for normal operation. |

...

| Source | Signal | Frequency | Destination | Pin Name | Notes | |

|---|---|---|---|---|---|---|

| U18 | CLK | 25.000000 MHz | U10 | IN3 | ||

| U9 | CLK | 25.000000 MHz | U7 | XTAL_IN | ||

| U11 | PS-CLK | 33.333333 MHz | U5 | PS_CLK_500 | Zynq SoC PS subsystem main clock. | |

| U15 | CLK | 52.000000 MHz | U6 | REFCLK | USB3320C PHY reference clock. |

...

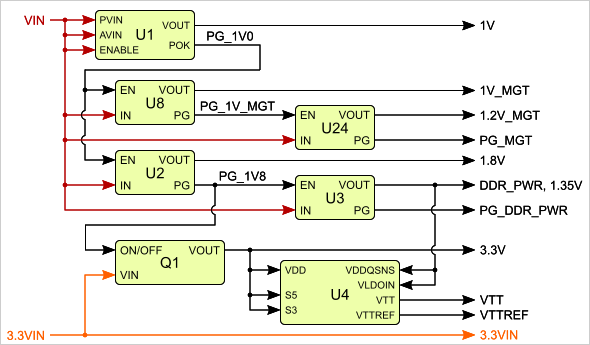

Figure 3: Module power distribution diagram.

Power-On Sequence

Figure 4: TE0820-02 power-on sequence diagram.

For highest efficiency of the on-board DC-DC regulators, it is recommended to use same 3.3V power source for both VIN and 3.3VIN power rails. Although VIN and 3.3VIN can be powered up in any order, it is recommended to power them up simultaneously.

It is important that all baseboard I/Os are 3-stated at power-on until System Controller CPLD sets PGOOD signal high (B2B connector JM1, pin 30), or 3.3V is present on B2B connector JM2 pins 10 and 12, meaning that all on-module voltages have become stable and module is properly powered up.

| Warning |

|---|

To avoid any damage to the module, check for stabilized on-board voltages should be carried out (3.3V (JM2-10, 12) or 1.8V(JM1-39) output) before powering up any FPGA's I/O bank voltages VCCO_x. All I/Os should be tri-stated during power-on sequence. |

See Xilinx datasheet DS187 (for XC7Z015) or DS191 (for XC7Z030) for See Xilinx datasheet DS187 (for XC7Z015) or DS191 (for XC7Z030) for additional information. User should also check related baseboard documentation when choosing baseboard design for TE0715 module.

...

B2B Name | B2B JM1 Pins | B2B JM2 Pins | Direction | Note | |

|---|---|---|---|---|---|

| VIN | 1, 3, 5 | 2, 4, 6, 8 | Input | Supply voltage. | |

| 3.3VIN | 13, 15 | - | Input | Supply voltage. | |

| VCCIO13 | 9, 11 | - | Input | High range bank voltage. | |

| VCCIO34 | - | 5 | Input | TE0715-xx-15: high range bank voltage. TE0715-xx-30: high performance bank voltage. | |

| VCCIO35 | - | 7, 9 | Input | TE0715-xx-15: high range bank voltage. TE0715-xx-30: high performance bank voltage. | |

| VBAT_IN | 79 | - | Input | RTC battery-buffer supply voltage. | |

| 3.3V | - | 10, 12 | Output | Internal 3.3V voltage level. | |

| 1.8V | 39 | - | Output | Internal 1.8V voltage level. | |

| DDR_PWR | - | 19 | Output | Internal 1.5V or 1.35V voltage level, depends on revision. | |

| VREF_JTAG | 91 | Output | JTAG reference voltage (3.3V). |

...

Board to Board Connectors

| Include Page | ||||||

|---|---|---|---|---|---|---|

|

Variants Currently in Production

...

Temperature

Range

...

B2B Connector

Height

...

Table 18: TE0715 variants currently in production.

Technical Specifications

Absolute Maximum Ratings

...

Parameter

...

Units

...

Notes

...

VIN supply voltage

...

-0.3

...

6.0

...

V

...

3.3VIN supply voltage

...

-0.4

...

3.6

...

V

...

PL IO bank supply voltage for HP I/O banks (VCCO)

...

Voltage on module JTAG pins

...

-0.4

...

V

...

Storage temperature

...

-40

...

+85

...

°C

...

| Trenz shop TE0715 overview page | |

|---|---|

| English page | German page |

Table 18: TE0715 variants currently in production.

Technical Specifications

Absolute Maximum Ratings

Parameter | Min | Max | Units | Notes |

|---|---|---|---|---|

VIN supply voltage | -0.3 | 6.0 | V | - |

3.3VIN supply voltage | -0.4 | 3.6 | V | - |

| VBAT supply voltage | -1 | 6.0 | V | - |

| PL IO bank supply voltage for HR I/O banks (VCCO) | -0.5 | 3.6 | V | - |

PL IO bank supply voltage for HP I/O banks (VCCO) | -0.5 | 2.0 | V | TE0715-xx-15 does not have HP banks. |

| I/O input voltage for HR I/O banks | -0.4 | VCCO + 0.55 | V | - |

| I/O input voltage for HP I/O banks | -0.55 | VCCO + 0.55 | V | TE0715-xx-15 does not have HP banks. |

| GT receiver (RXP/RXN) and transmitter (TXP/TXN) | -0.5 | 1.26 | V | - |

Voltage on module JTAG pins | -0.4 | VCCO_0 + 0.55 | V | VCCO_0 is 3.3V nominal. |

Storage temperature | -40 | +85 | °C | - |

| Storage temperature without the ISL12020MIRZ and 88E1512 | -55 | +100 | °C | - |

Table 19: TE0715 module absolute maximum ratings.

| Note |

|---|

| Assembly variants for higher storage temperature range are available on request. |

| Note |

|---|

| Please check Xilinx datasheet DS187 (for XC7Z015) or DS191 (for XC7Z030) for complete list of absolute maximum and recommended operating ratings. |

| Page break |

|---|

Recommended Operating Conditions

| Parameter | Min | Max | Units | Notes | Reference Document |

|---|---|---|---|---|---|

| VIN supply voltage | 2.5 | 5.5 | V | ||

| 3.3VIN supply voltage | 3.135 | 3.465 | V | ||

| VBAT_IN supply voltage | 2.7 | 5.5 | V | ||

PL I/O bank supply voltage for HR I/O banks (VCCO) | 1.14 | 3.465 | V | Xilinx datasheet DS191 | |

PL I/O bank supply voltage for HP I/O banks (VCCO) | 1.14 | 1.89 | V | TE0715-xx-15 does not have HP banks | Xilinx datasheet DS191 |

| I/O input voltage for HR I/O banks | (*) | (*) | V | (*) Check datasheet | Xilinx datasheet DS191 or DS187 |

| I/O input voltage for HP I/O banks | (*) | (*) | V | TE0715-xx-15 does not have HP banks (*) Check datasheet | Xilinx datasheet DS191 |

| Voltage on Module JTAG pins |

Table 19: TE0715 module absolute maximum ratings.

| Note |

|---|

| Assembly variants for higher storage temperature range are available on request. |

| Note |

|---|

| Please check Xilinx datasheet DS187 (for XC7Z015) or DS191 (for XC7Z030) for complete list of absolute maximum and recommended operating ratings. |

| Page break |

|---|

Recommended Operating Conditions

| Parameter | Min | Max | Units | Notes | Reference Document |

|---|---|---|---|---|---|

| VIN supply voltage | 2.5 | 5.5 | V | ||

| 3.3VIN supply voltage | 3.135 | 3.465 | V | ||

| VBAT_IN supply voltage | 2.7 | 5.5 | V | ||

PL I/O bank supply voltage for HR I/O banks (VCCO) | 1.14 | 3.465 | V | Xilinx datasheet DS191 | |

PL I/O bank supply voltage for HP I/O banks (VCCO) | 1.14 | 1.89 | V | TE0715-xx-15 does not have HP banks | Xilinx datasheet DS191 |

| I/O input voltage for HR I/O banks | (*) | (*) | V | (*) Check datasheet | Xilinx datasheet DS191 or DS187 |

| I/O input voltage for HP I/O banks | (*) | (*) | V | TE0715-xx-15 does not have HP banks (*) Check datasheet | Xilinx datasheet DS191 |

| Voltage on Module JTAG pins | 3.135 | 3.465 | V | VCCO_0 is 3.3 V nominal |

Table 20: TE0715 module recommended operating conditions.

Operating Temperature Ranges

Commercial grade: 0°C to +70°C.

Industrial and extended grade: -40°C to +85°C.

The module operating temperature range depends also on customer design and cooling solution. Please contact us for options.

| Page break |

|---|

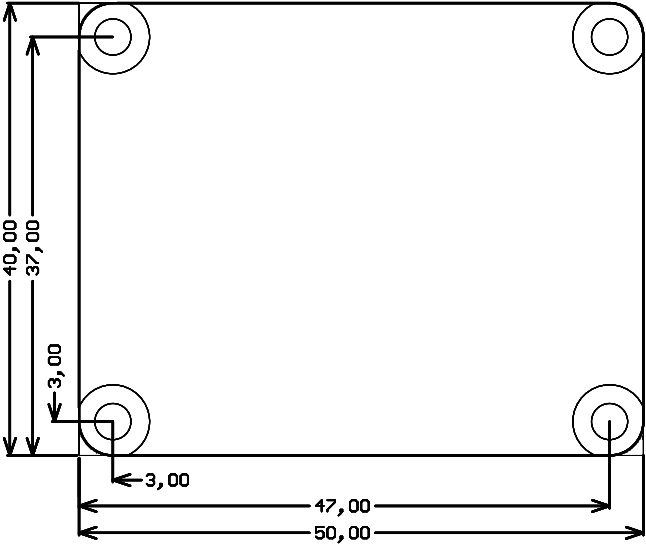

Physical Dimensions

Module size: 50 mm × 40 mm. Please download the assembly diagram for exact numbers

Mating height with standard connectors: 8mm

PCB thickness: 1.6mm

Highest part on PCB: approx. 2.5mm. Please download the step model for exact numbers

All dimensions are given in millimeters.

Figure 3: TE0715 physical dimensions.

Revision History

Hardware Revision History

...

Notes

...

01

...

Prototypes

...

| VCCO_0 is 3.3 V nominal |

Table 20: TE0715 module recommended operating conditions.

Operating Temperature Ranges

Commercial grade: 0°C to +70°C.

Industrial and extended grade: -40°C to +85°C.

The module operating temperature range depends also on customer design and cooling solution. Please contact us for options.

| Page break |

|---|

Physical Dimensions

Module size: 50 mm × 40 mm. Please download the assembly diagram for exact numbers

Mating height with standard connectors: 8mm

PCB thickness: 1.6mm

Highest part on PCB: approx. 2.5mm. Please download the step model for exact numbers

All dimensions are given in millimeters.

Figure 5: TE0715 physical dimensions.

Revision History

Hardware Revision History

| Date | Revision | Notes | Link to PCN | Documentation Link |

|---|---|---|---|---|

| 2022-12-21 | 05 | Third production release | TE0715-05 | |

| 2016-06-21 | 04 | Second production release | Click to see PCN | TE0715-04 |

| - | 03 | First production release | TE0715-03 | |

| - | 02 | Prototypes | TE0715-02 | |

| - | 01 | Prototypes |

Table 21: TE0715 module hardware revision history.

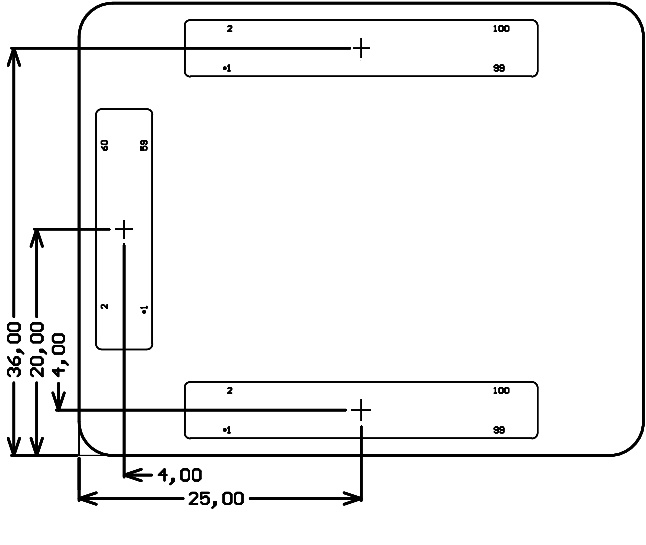

Hardware revision number is printed on the PCB board together with the module model number separated by the dash.

Figure 6: TE0715 hardware revision number.

Document Change History

Date | Revision | Contributors | Description | ||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

|

|

| ||||||||||||||||||||||||||

| 2021-06-21 | v.87 | John Hartfiel |

| ||||||||||||||||||||||||||

| 2018-07-06 | v.86 | John Hartfiel |

| ||||||||||||||||||||||||||

2017-11-14 | v.85 | John Hartfiel |

| ||||||||||||||||||||||||||

| 2017-09-10 | v.82 |

Table 21: TE0715 module hardware revision history.

Hardware revision number is printed on the PCB board together with the module model number separated by the dash.

Figure 4: TE0715 hardware revision number.

Document Change History

Date | Revision | Contributors | Description | |||

|---|---|---|---|---|---|---|

| Page info | | modified-date | modified-date | dateFormat | yyyy-MM-ddJan Kumann |

|

| 2017-06-07 | v.64 | Jan Kumann |

| |||

| 2017-03-02 | v.59 | Thorsten Trenz |

| |||

| 2017-02-10 | v.58 | Thorsten Trenz |

| |||

| 2017-01-25 | v.55

| Jan Kumann |

| |||

| 2017-01-14 | v.50 | Jan Kumann |

| |||

| 2016-11-15 | v.45 | Thorsten Trenz |

| |||

| 2016-10-18 | v.40 | Ali Naseri |

| |||

| 2016-06-28 | v.38 | Thorsten Trenz, Emmanuel Vassilakis, Jan Kumann |

| |||

| 2016-04-27 | v.33 | Thorsten Trenz, Emmanuel Vassilakis |

| |||

| 2016-03-31 | v.10 | Philipp Bernhardt, Antti Lukats |

|

Table 22: Document change history.

...