Page History

...

Vivado IPI Block Diagram for the f32c_demo. F32C is clocked at 100MHz, Memory configuration set to 128KByte or larger for all devices that have enough BRAM's, bit 0 of simple_out is connected to on-board LED. Optionally there may be FPGA debug IP Cores added, VIO and or ILA, in the example above is Logic Analyzer added on the UART (using UART_MON IP Core). Baud rate 115200.

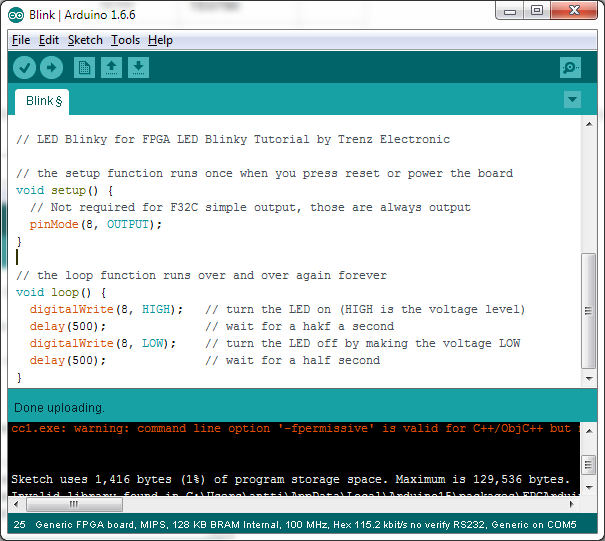

This is Arduino IDE screenshot after downloading LED Blinky sketch to F32C inside FPGA, selected generic FPGA board with 128K RAM and 100MHz Clock. After download the on-board LED on the FPGA/SoC SoM will blink.

...

Overview

Content Tools