Page History

...

If we do not know how to access the time/clock source or if we are not sure if the clock is enabled and running we have an potential problem and we can not proceed to the LED Blinky unless we have identified an active/enabled accessible clock source we can use for timing.

FPGA Devices

GT Clock

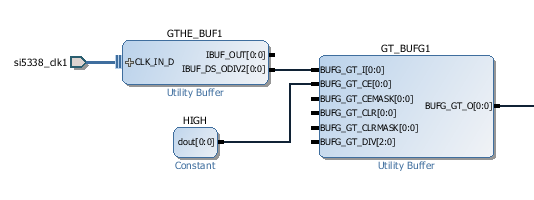

Gigabit Transceiver Clock may also be used as FPGA Fabric clock.

Clock buffers for GT Clock in Ultrascale Devices (example from TE0841 design)

ZYNQ Devices

In Zynq System the main System Clock is connected PS (Processing Subsystem) and is not directly available to the PL (Programmable Logic - FPGA) unless the PS has enabled it during FSBL boot process. So if we have a generic Zynq Board then we can not expect to have clocks available to the FPGA until the Processing system has provided them. There may be clocks available to the PL that are active when the PS is not booted but this not a requirement.

...