Versions Compared

Key

- This line was added.

- This line was removed.

- Formatting was changed.

| Custom_table_size_100 |

|---|

| Page properties | ||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||

Template Change history:

|

| Page properties | ||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||

Important General Note:

|

| Page properties | ||||

|---|---|---|---|---|

| ||||

----------------------------------------------------------------------- |

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note for Download Link of the Scroll ignore macro:

|

| Scroll Ignore |

|---|

Overview

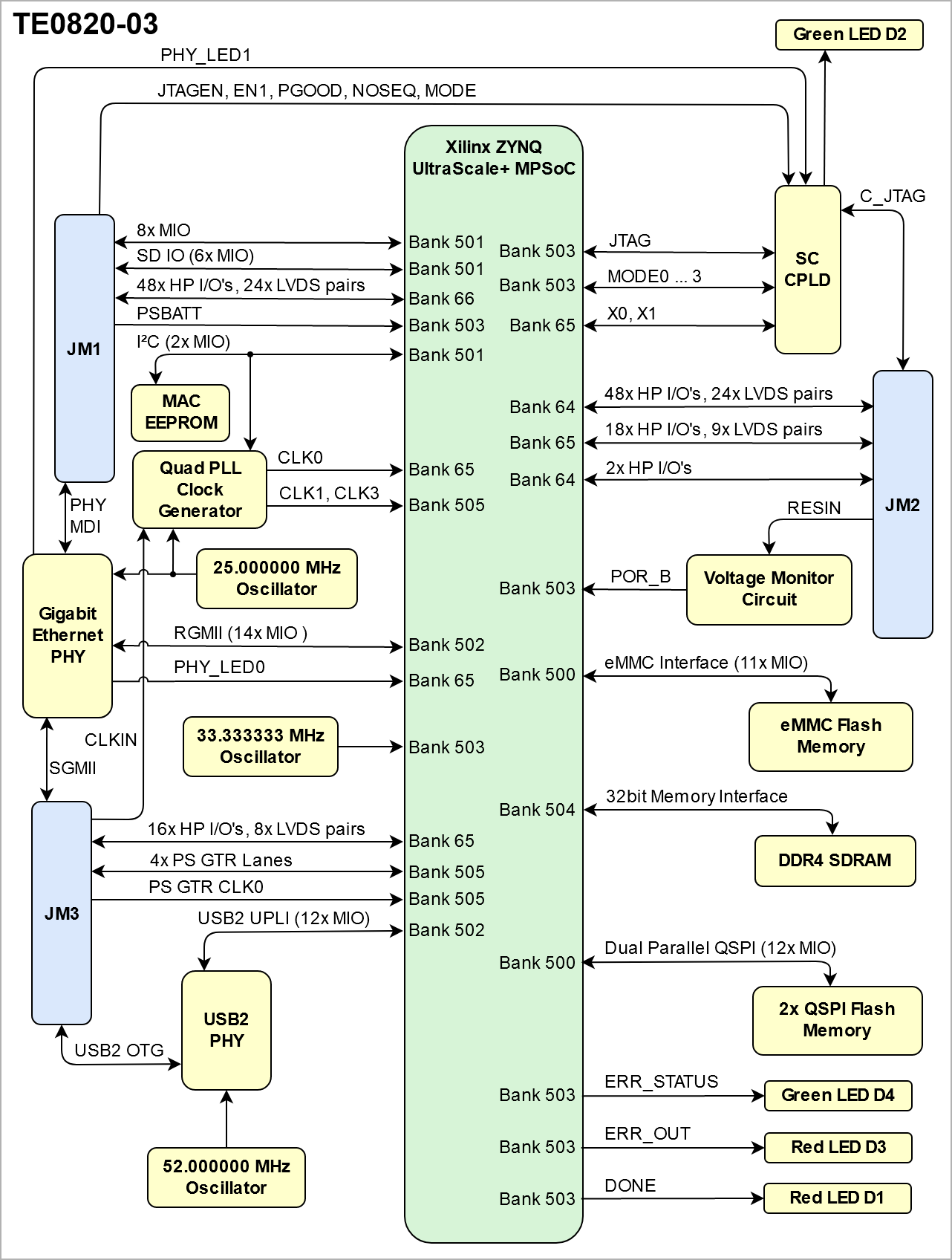

The Trenz Electronic TE0820 is a powerful 4 x 5 cm industrial/extended module integrated with a Xilinx Zynq UltraScale+ MPSoC. In addition, the module is equipped with 2x 8 Gb DDR4 SDRAM chip, up to 64 Gb eMMC chip, 2x 512 Mb flash memory for configuration and data storage, as well as powerful switching power supplies for all required voltages. The module is equipped with a Lattice Mach XO2 CPLD for system controlling. 3x Robust high-speed connectors provide a large number of inputs and outputs. Additionally the module provides Gigabit Ethernet and USB2.0 Transceivers.

The highly integrated modules are smaller than a credit card and are offered in several variants at an affordable price-performance ratio. Modules with a 4 x 5 cm form factor are completely mechanically and largely electrically compatible with each other.

All components cover at least the industrial temperature range. The temperature range in which the module can be used depends on the customer design and the selected cooling. Please contact us for special solutions.

Refer to http://trenz.org/te0820-info for the current online version of this manual and other available documentation.

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note: → See examples fro different types <Series Name> TRM Template section examples#%3CSeriesName%3ETRMTemplatesectionexamples-KeyFeatures |

Key Features

- SoC/FPGA

- Package: SFVC784

- Device: ZU2 ...ZU5, *

- Engine: EG, CG, EV, *

- Speed: -1, -1L, -2, -2L, 3, *, **

- Temperature: I, E, *, **

- RAM/Storage

- 2x DDR4 SDRAM,

- Data Width: 16 Bit

- Size: 8 Gb, *

- Speed: 2400 Mbps, ***

- 2x QSPI boot Flash in dual parallel mode

- Data Width: 8 Bit

- Size: 512 Mb Gb, *

- 1x e.MMC Memory

- Data Width: 16 Bit

- Size: 8 Gb, *

- MAC address serial EEPROM

- 2x DDR4 SDRAM,

- On Board

- Lattice MachXO2 CPLD

- Programmable Clock Generator

- Hi-speed USB2 ULPI Transceiver

- 4x LEDS

- Interface

- 1 Gbps RGMII Ethernet interface

- Hi-speed USB2 ULPI transceiver with full OTG support

- Graphic Processor Mali-400 MP2, *

- 132x High Performance (HP)

- 4 x serial PS GTR transceivers

- PCI Express interface

- SATA 3.1 interface

DisplayPort interface with video resolution up to 4k x 2k

- 2x USB 3.0 specification compliant interface implementing a 5 Gbit/s line rate

- Power

- All power regulators on board

- Dimension

- 40 x 50 mm

- Note

- * depends on assembly version

- ** also non low power assembly options possible

- *** depends on used U+ Zynq and DDR4 combination

- Rugged for shock and high vibration

Additional assembly options are available for cost or performance optimization upon request.

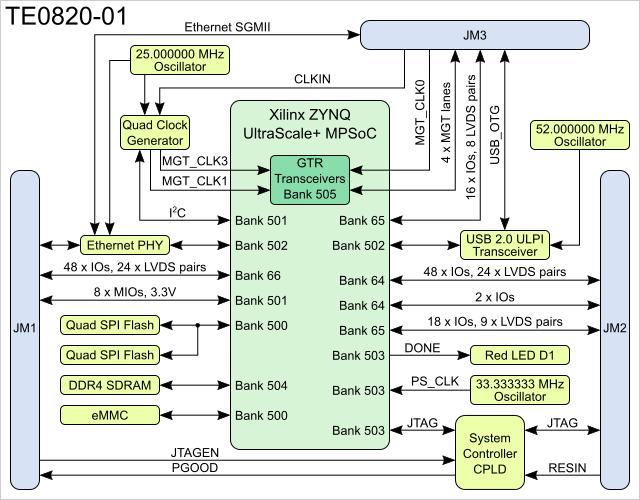

Block Diagram

| Page properties | ||||||

|---|---|---|---|---|---|---|

| ||||||

add drawIO object in Scroll Ignore section and add reference image in Scroll Only.

|

| Scroll Title | ||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||

|

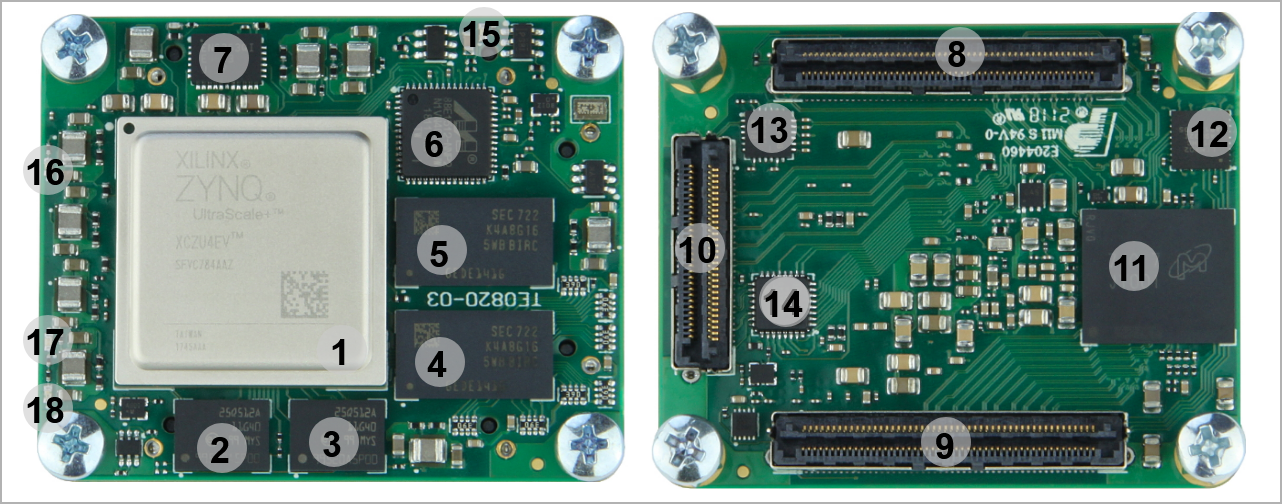

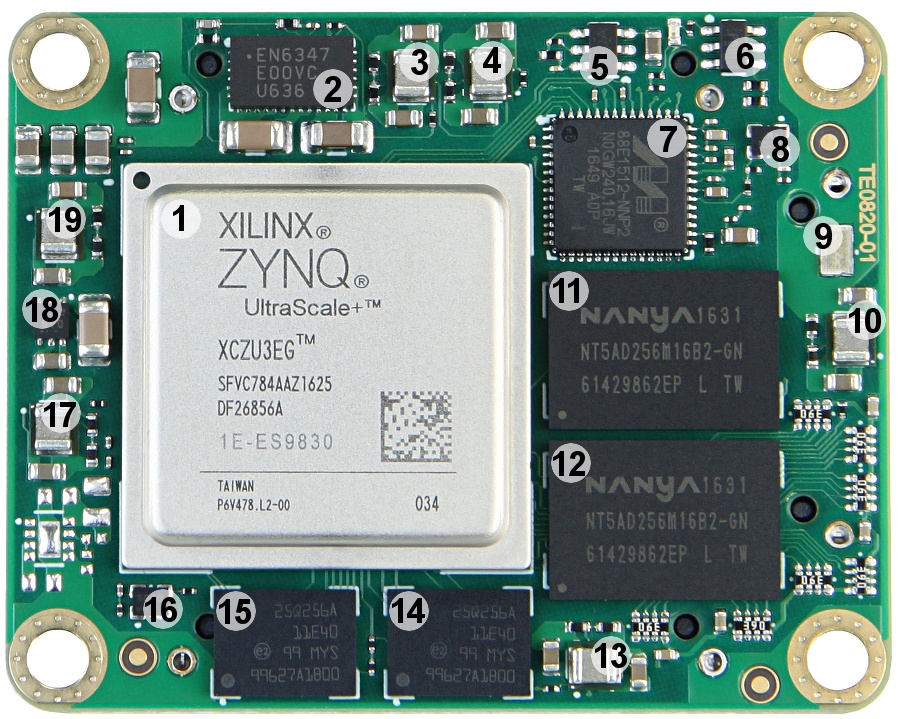

Main Components

| Scroll Title | ||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||

|

- Xilinx Zynq UltraScale+ MPSoC, U1

- 1.8V, 512 Mbit QSPI flash memory, U7

- 1.8V, 512 Mbit QSPI flash memory, U17

- 8 Gbit (512 x 16) DDR4 SDRAM, U2

- 8 Gbit (512 x 16) DDR4 SDRAM, U3

- Marvell Alaska 88E1512 integrated 10/100/1000 Mbps energy efficient ethernet transceiver, U8

- 6A PowerSoC DC-DC converter (PL_VCCINT, 0.85V), U5

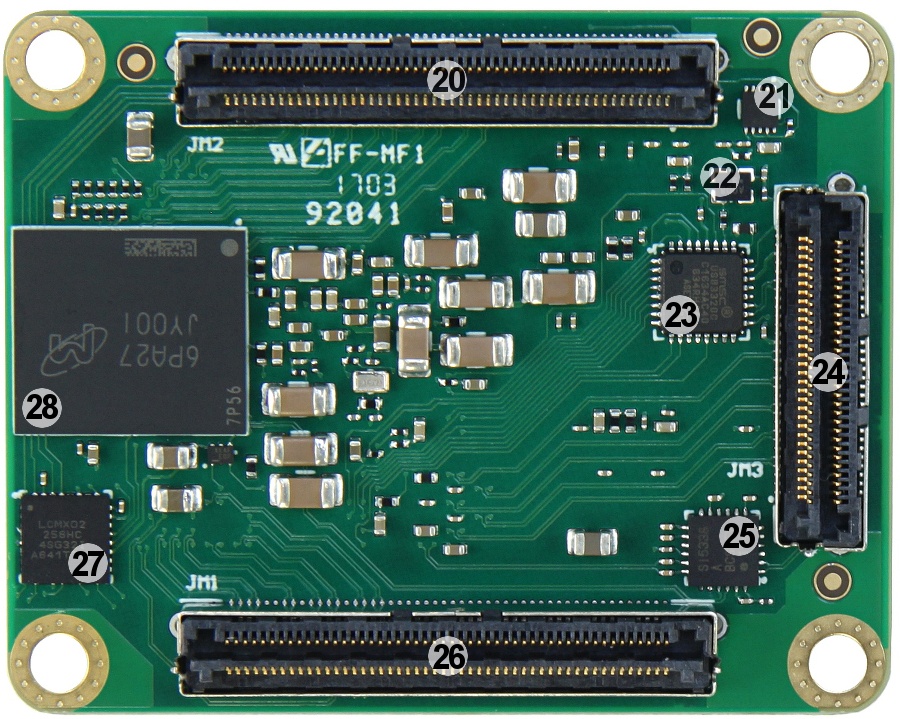

- B2B connector Samtec Razor Beam™ LSHM-150, JM1

- B2B connector Samtec Razor Beam™ LSHM-150, JM2

- B2B connector Samtec Razor Beam™ LSHM-130, JM3

- 8 GByte eMMC memory, U6

- Lattice Semiconductor MachXO2 System Controller CPLD, U21

- I2C programmable, any frequency , any output quad clock generator, U10

- Highly integrated full featured hi-speed USB 2.0 ULPItransceiver, U18

- LED D1(Red) Done Pin

- LED D2 (Green) CPLD Status, User LED

- LED D3 (Red) PS Error

- LED D4 (Green) PS Error Status

Initial Delivery State

| Page properties | ||||

|---|---|---|---|---|

| ||||

|

| Scroll Title | ||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||

|

Configuration Signals

| Page properties | ||||

|---|---|---|---|---|

| ||||

|

Two different firmware versions are available, one with the QSPI boot option and other with the SD Card boot option.

| Scroll Title | ||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||

*changable also with other CPLD Firmware: TE0820 CPLD |

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

Signals, Interfaces and Pins

| Page properties | ||||

|---|---|---|---|---|

| ||||

For subsection examples see: <Series Name> TRM Template section examples#%3CSeriesName%3ETRMTemplatesectionexamples-Signals,InterfacesandPins

|

Board to Board (B2B) I/Os

Zynq MPSoC's I/O banks signals connected to the B2B connectors:

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

For detailed information about the pin-out, please refer to the Pin-out table.

MGT Lanes

The Xilinx Zynq UltraScale+ device used on the TE0820 module has 4 GTR transceivers. All 4 are wired directly to B2B connector JM3. MGT (Multi Gigabit Transceiver) lane consists of one transmit and one receive (TX/RX) differential pairs, four signals total per one MGT lane. Following table lists lane number, FPGA bank number, transceiver type, signal schematic name, board-to-board pin connection and FPGA pins connection:

| Scroll Title | |||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||||||||||||

|

There are 3 clock sources for the GTR transceivers. B505_CLK0 is connected directly to B2B connector JM3, so the clock can be provided by the carrier board. Clocks B505_CLK1 and B505_CLK3 are provided by the on-board clock generator (U10). As there are no capacitive coupling of the data and clock lines that are connected to the connectors, these may be required on the user’s PCB depending on the application.

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

JTAG Interface

JTAG access to the Xilinx Zynq-7000 is provided through B2B connector JM2.

| Scroll Title | ||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||

|

Pin 89 JTAGEN of B2B connector JM1 is used to control which device is accessible via JTAG. If set to low or grounded, JTAG interface will be routed to the Xilinx Zynq MPSoC. If pulled high, JTAG interface will be routed to the System Controller CPLD.

I2C Addresses

On-board I2C devices are connected to MIO38 (SCL) and MIO39 (SDA) which are configured as I2C0 by default. Addresses for on-board I2C slave devices are listed in the table below:

| Scroll Title | |||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||

|

MIOs

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Test Points

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

On-board Peripherals

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes : In the on-board peripheral table "chip/Interface" must be linked to the corresponding chapter or subsection by assigning advance link using: #NameOfTheSection Example: #ClockSources, #CPLD, #QuadSPIFlash |

| Scroll Title | |||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||||||||||||||||||||

|

System Controller CPLD

The System Controller CPLD (U21) is provided by Lattice Semiconductor LCMXO2-256HC (MachXO2 product family). It is the central system management unit with module specific firmware installed to monitor and control various signals of the FPGA, on-board peripherals, I/O interfaces and module.

Special purpose pins are connected to System Controller CPLD and have following default configuration:

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||

|

Please check the entire information at TE0820 CPLD.

See also TE0820 System Controller CPLD page.

eMMC Memory

eMMC Flash memory device(U6) is connected to the ZynqMP PS MIO bank 500 pins MIO13..MIO23. eMMC chips IS21ES08G-JCLI (FLASH - NAND Speicher-IC (64 Gb x 1) MMC ) is used.

DDR4 Memory

The TE0820 SoM has dual 8 Gb volatile DDR4 SDRAM IC for storing user application code and data.

- Part number: K4A8G165WB-BIRC

- Supply voltage: 1.2V

- Speed: 2400 Mbps

- Temperature: -40 ~ 95 °C

Quad SPI Flash Memory

Two quad SPI compatible serial bus flash MT25QU512ABB8E12-0SIT memory chips are provided for FPGA configuration file storage. After configuration completes the remaining free memory can be used for application data storage. All four SPI data lines are connected to the FPGA allowing x1, x2 or x4 data bus widths to be used. The maximum data transfer rate depends on the bus width and clock frequency.

Gigabit Ethernet

On-board Gigabit Ethernet PHY (U8) is provided with Marvell Alaska 88E1512 IC (U8). The Ethernet PHY RGMII interface is connected to the ZynqMP Ethernet3 PS GEM3. I/O voltage is fixed at 1.8V for HSTL signaling. The reference clock input of the PHY is supplied from an on-board 25.000000 MHz oscillator (U11).

High-speed USB ULPI PHY

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

USB2.0 Transceiver

Hi-speed USB ULPI PHY (U18) is provided with USB3320 from Microchip. The ULPI interface is connected to the Zynq PS USB0 via MIO52..63, bank 502. The I/O voltage is fixed at 1.8V and PHY reference clock input is supplied from the on-board 52.00 MHz oscillator (U14).

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

EEPROM

There is a 2Kb EEPROM (U25) provided on the module TE0820.

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

Programmable Clock Generator

There is a Silicon Labs I2C programmable clock generator Si5338A (U10) chip on the module. It's output frequencies can be programmed using the I2C bus address 0x70 or 0x71. Default address is 0x70, IN4/I2C_LSB pin must be set to high for address 0x71.

A 25.000000 MHz oscillator is connected to the pin IN3 and is used to generate the output clocks. The oscillator has its output enable pin permanently connected to 1.8V power rail, thus making output frequency available as soon as 1.8V is present. Three of the Si5338 clock outputs are connected to the FPGA. One is connected to a logic bank and the other two are connected to the GTR banks.

Once running, the frequency and other parameters can be changed by programming the device using the I2C bus connected between the FPGA (master) and clock generator (slave). For this, proper I2C bus logic has to be implemented in FPGA.

| Scroll Title | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Clock Sources

| Scroll Title | ||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||

|

LEDs

| Scroll Title | |||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||||||||||||

|

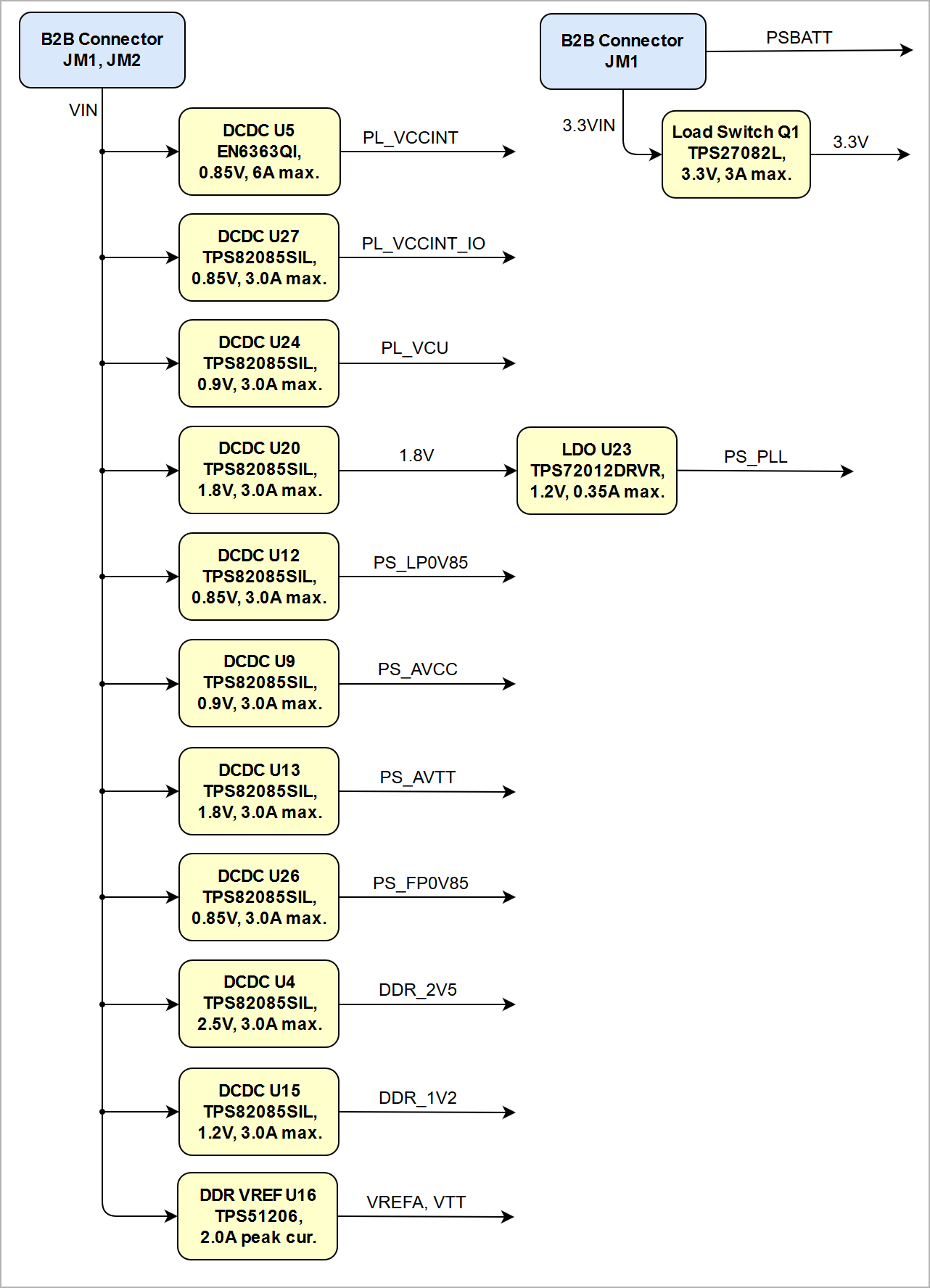

Power and Power-on Sequence

| Page properties | ||||

|---|---|---|---|---|

| ||||

In 'Power and Power-on Sequence' section there are three important digrams which must be drawn:

|

Power Supply

Power supply with minimum current capability of 3A for system startup is recommended.

Power Consumption

| Scroll Title | ||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||

|

* TBD - To Be Determined soon with reference design setup.

For the lowest power consumption and highest efficiency of the on-board DC-DC regulators it is recommended to power the module from one single 3.3V supply. All input power supplies should have a nominal value of 3.3V. Although the input power supplies can be powered up in any order, it is recommended to power them up simultaneously.

| Warning |

|---|

| To avoid any damage to the module, check for stabilized on-board voltages should be carried out (i.e. power good and enable signals) before powering up any Zynq's I/O bank voltages VCCO_x. All I/Os should be tri-stated during power-on sequence. |

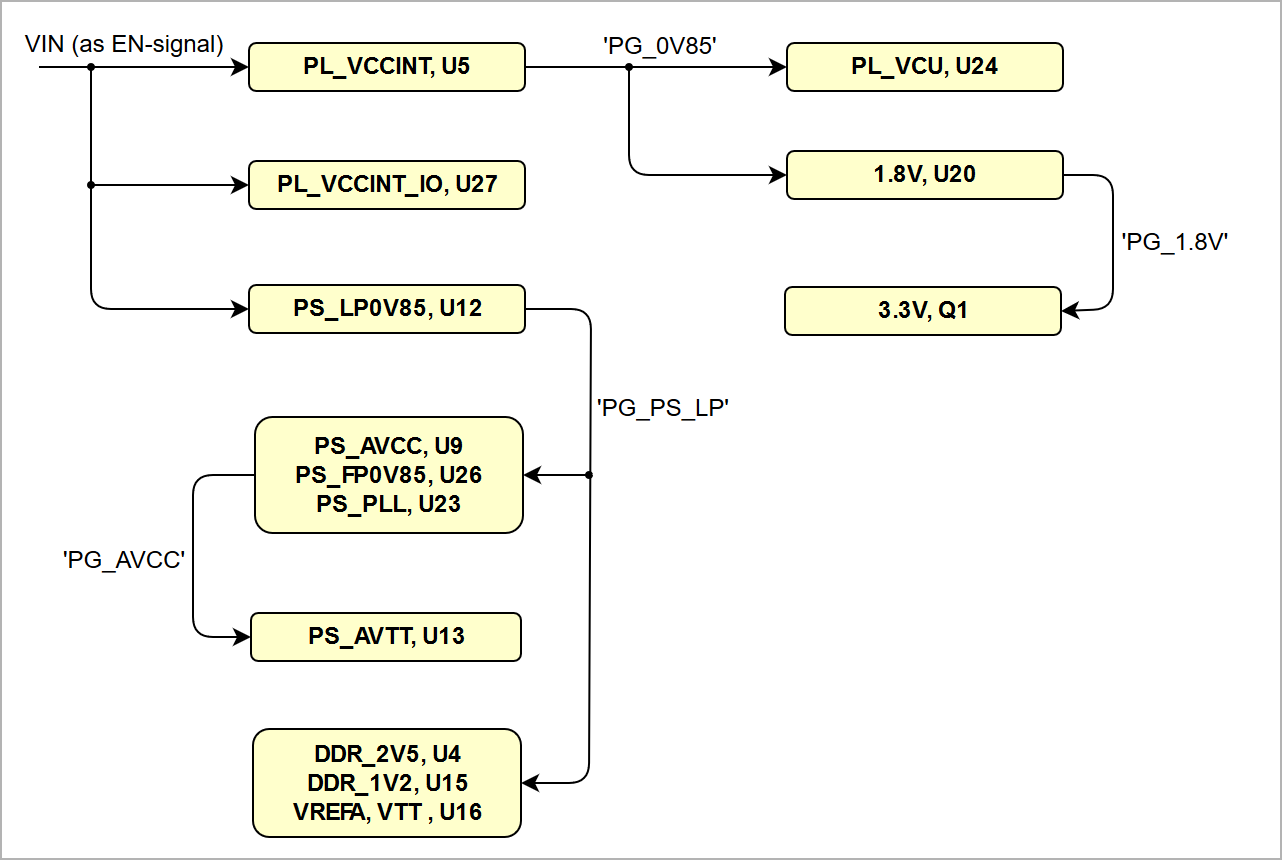

Power Distribution Dependencies

| Scroll Title | ||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||

|

See also Xilinx datasheet DS925 for additional information. User should also check related base board documentation when intending base board design for TE0820 module.

Power-On Sequence

The TE0820 SoM keeping a specific sequence of enabling the on-board DC-DC converters dedicated to the particular functional units of the Zynq chip and powering up the on-board voltages.

Following diagram clarifies the sequence of enabling the particular on-board voltages, which will power-up in descending order as listed in the blocks of the diagram:

| Scroll Title | ||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||

|

For highest efficiency of the on-board DC-DC regulators, it is recommended to use one 3.3V power source for both VIN and 3.3VIN power rails. Although VIN and 3.3VIN can be powered up in any order, it is recommended to power them up simultaneously.

It is important that all carrier board I/Os are 3-stated at power-on until 3.3V_out or 1.8V_out is present on B2B connector JM2 pins 10 and 12, indicating that all on-module voltages have become stable and module is properly powered up.

See Xilinx datasheet DS925 for additional information. User should also check related carrier board documentation when choosing carrier board design for TE0715 module.

Power Rails

| Scroll Title | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Bank Voltages

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Board to Board Connectors

| Page properties | ||||||

|---|---|---|---|---|---|---|

| ||||||

|

| Include Page | ||||

|---|---|---|---|---|

|

Technical Specifications

Absolute Maximum Ratings

| Scroll Title | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Recommended Operating Conditions

| Scroll Title | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

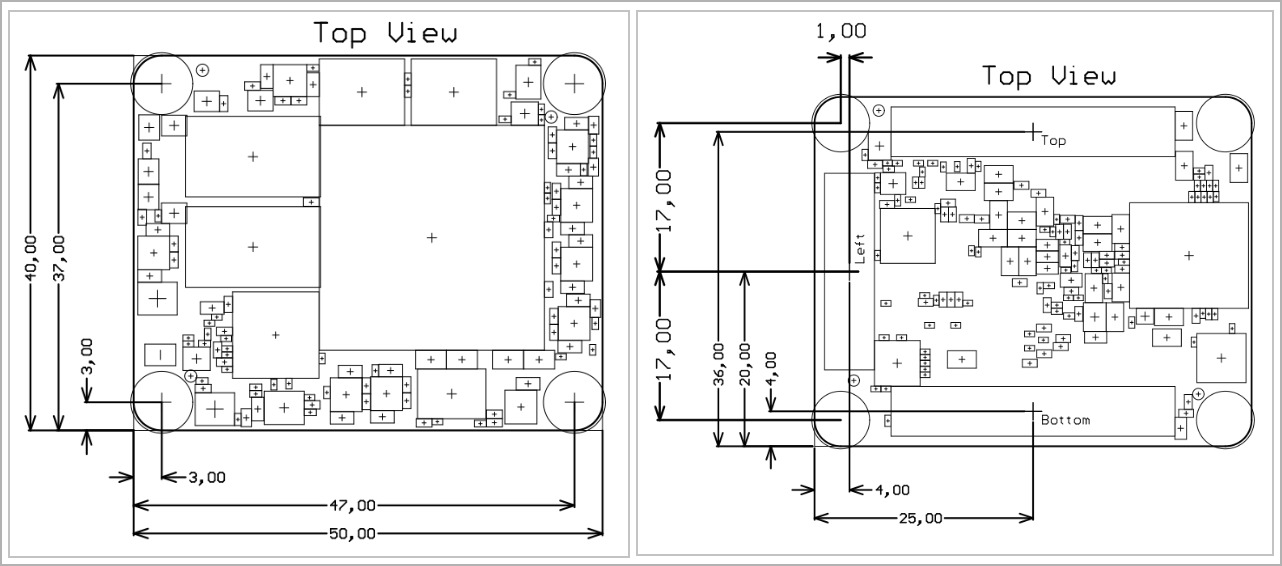

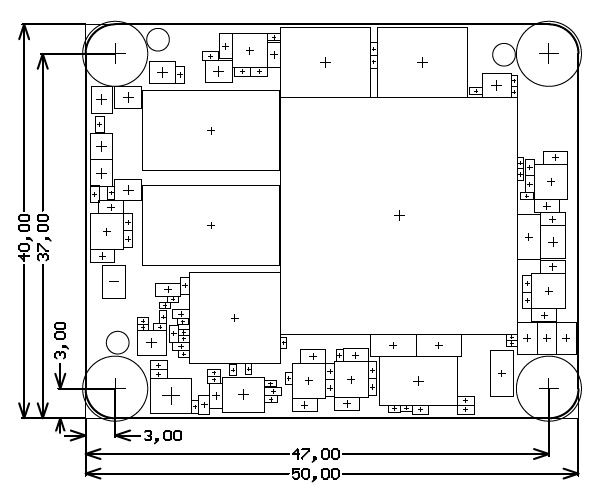

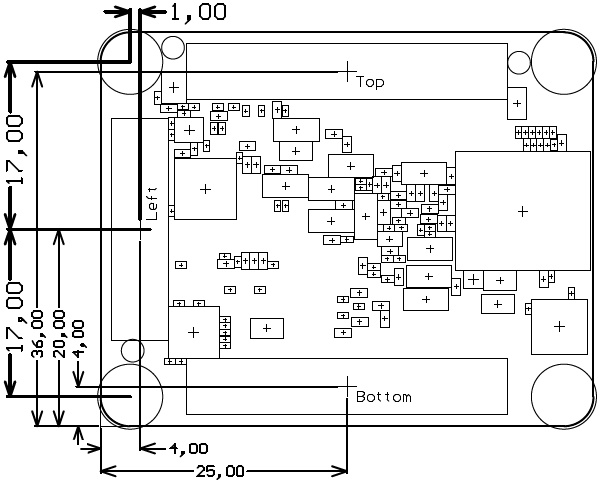

Physical Dimensions

| Page properties | ||||

|---|---|---|---|---|

| ||||

In 'Physical Dimension' section, top and bottom view of module must be inserted, information regarding physical dimensions can be obtained through webpage for product in Shop.Trenz, (Download> Documents> Assembly part) for every SoM. For Example: for Module TE0728, Physical Dimension information can be captured by snipping tools from the link below:

|

Module size: 50 mm × 40 mm. Please download the assembly diagram for exact numbers.

Mating height with standard connectors: 8 mm

PCB thickness: 1.6 mm

Highest part on PCB: approximately 5 mm. Please download the step model for exact numbers.

All dimensions are shown in millimeters.

| Scroll Title | |||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||||||||||||

|

Currently Offered Variants

| Page properties | ||||

|---|---|---|---|---|

| ||||

Set correct link to the shop page overview table of the product on English and German. Example for TE0706: ENG Page: https://shop.trenz-electronic.de/en/search?sSearch=TE0706 DEU Page: https://shop.trenz-electronic.de/de/search?sSearch=TE0706 |

| Scroll Title | ||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||

| ||||||||||||||||||||||

Revision History

Hardware Revision History

| Page properties | ||||||||

|---|---|---|---|---|---|---|---|---|

| ||||||||

Set correct links to download Carrier, e.g. TE0706 REV02: TE0706-02 -> https://shop.trenz-electronic.de/Download/?path=Trenz_Electronic/Modules_and_Module_Carriers/4x5/4x5_Carriers/TE0706/REV02/Documents Note:

|

| Scroll Title | |||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||||||||||||

|

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Document Change History

| Page properties | ||||

|---|---|---|---|---|

| ||||

|

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Table 21: Document change history

Disclaimer

| Include Page | ||||

|---|---|---|---|---|

|

| Scroll Only | ||

|---|---|---|

|

| Scroll pdf ignore | ||||||

|---|---|---|---|---|---|---|

|

...

Download PDF version of this document.

| Scroll pdf ignore | |

|---|---|

Table of Contents

|

Overview

| Scroll Only (inline) |

|---|

Refer to https://shop.trenz-electronic.de/de/Download/?path=Trenz_Electronic/TE0820 for downloadable version of this manual and additional technical documentation of the product.

|

All this on a tiny footprint, smaller than a credit card, at the most competitive price.

All Trenz Electronic SoMs in 4 x 5 cm form factor are mechanically compatible.

Block Diagram

Image Removed

Image Removed

Main Components

Image Removed

Image Removed  Image Removed

Image Removed

- Xilinx Zynq UltraScale+ ZU3EG MPSoC, U1

- 4A power system on a chip (PowerSoC) DC-DC converter, U5

- 3A High efficiency step-down converter MicroSiP™ with integrated inductor (0.9V), U9

- 3A High efficiency step-down converter MicroSiP™ with integrated inductor (1.8V), U13

3A PFET load switch with configurable slew rate, fast transient isolation and hysteresis control, Q1

- Ultralow supply-current voltage monitor with optional watchdog, U19

- Marvell Alaska 88E1512 integrated 10/100/1000 Mbps energy efficient ethernet transceiver, U8

- Low power programmable oscillator @ 12.000000 MHz, U11

- Miniature traceability S/N pad for low-cost, unique product identification

- 3A High efficiency step-down converter MicroSiP™ with integrated inductor (2.5V), U4

- 4 Gbit (256 x 16) DDR4 SDRAM, U3

- 4 Gbit (256 x 16) DDR4 SDRAM, U2

- 3A High efficiency step-down converter MicroSiP™ with integrated inductor (1.2V), U15

- 1.8V, 256 Mbit multiple I/O serial flash memory, U17

- 1.8V, 256 Mbit multiple I/O serial flash memory, U7

- Low power programmable oscillator @ 33.333333 MHz, U32

- 3A High efficiency step-down converter MicroSiP™ with integrated inductor (0.85V), U12

- 350 mA, ultra-low VIN, RF low-dropout linear regulator with bias pin, U23

- 3A High efficiency step-down converter MicroSiP™ with integrated inductor (1.8V), U20

- B2B connector Samtec Razor Beam™ LSHM-150, JM2

- 2A peak sink / source DDR termination regulator with VTTREF buffered reference for DDR2, DDR3, DDR3L, and DDR4, U16

- Low power programmable oscillator @ 52.000000 MHz, U14

- Highly integrated full featured hi-speed USB 2.0 ULPI transceiver, U18

- B2B connector Samtec Razor Beam™ LSHM-130, JM3

- I2C programmable, any frequency , any output quad clock generator, U10

- B2B connector Samtec Razor Beam™ LSHM-150, JM1

- Lattice Semiconductor MachXO2 System Controller CPLD, U21

- 4 GByte eMMC memory, U6

Key features

- Xilinx Zynq UltraScale+ MPSoC 784 pin package (ZU3EG, option ZU5EV)

- Memory:

- 32-Bit DDR4 - 4 GByte max

- SPI Boot Flash dual parallel - 512 MByte max

- 4 GByte eMMC (up to 64 GByte)

- B2B connectors:

Plug-on module with 2 x 100-pin and 1 x 60-pin high-speed hermaphroditic strips- 14 x MIO, 132 I/O's x HP (3 banks)

- 4 x serial PS GTR transceivers

- GT Reference clock input

- PLL for GT clocks (optional external reference)

- 1 Gbit Ethernet PHY

- USB 2.0 OTG PHY

- Real Time Clock

- Size: 40 x 50 mm

- All power supplies on board.

Initial delivery state

Signals Interfaces and Pins

Board to Board (B2B) I/Os

I/O signals connected to the MPSoC's I/O bank and B2B connector:

...

B2B

Connector

...

I/O Signal

Count

...

64

...

HP

...

JM2

...

48

...

User

...

64

...

HP

...

JM2

...

2

...

User

...

HP

...

JM2

...

18

...

User

...

65

...

HP

...

JM3

...

12

...

User

...

66

...

HP

...

JM1

...

48

...

User

...

501

...

MIO

...

JM1

...

6

...

1.8V

...

505

...

GTR

...

JM3

...

4 lanes

...

N/A

...

505

...

GTR CLK

...

JM3

...

2 differential inputs

...

N/A

...

-

For detailed information about the pin out, please refer to the Pin-out Table.

JTAG Interface

System Controller I/O Pins

On-board LEDs

Default MIO Mapping

Gigabit Ethernet

USB Interface

I2C Interface

Boot Modes

On-board Peripherals

Processing System (PS) Peripherals

Clocking

Power and Power-on sequence

Power Supply

Power-on sequence

Power Rails

Bank Voltages

Board to Board Connectors

Technical Specifications

Absolute Maximum Ratings

...

Parameter

...

Units

...

Notes

...

VIN supply voltage

...

-0.1

...

3.6

...

V

...

Voltage on module JTAG pins

...

-0.4

...

V

...

Storage temperature

...

-40

...

+85

...

°C

...

Recommended Operating Conditions

...

| Note |

|---|

| Please check Xilinx datasheet DS181 for complete list of absolute maximum and recommended operating ratings for the Artix-7. |

Physical Dimensions

Module size: 50 mm × 40 mm. Please download the assembly diagram for exact numbers.

Mating height with standard connectors: 8 mm

PCB thickness: 1.6 mm

Highest part on PCB: approximately 5 mm. Please download the step model for exact numbers.

All dimensions are shown in mm. Additional sketches, drawings and schematics can be found here.

...

Image Removed

Image Removed

...

Image Removed

Image Removed

...

Operating Temperature Ranges

Commercial grade modules

All parts are at least commercial temperature range of 0 °C to +70 °C. The module operating temperature range depends on customer design and cooling solution. Please contact us for options.

Industrial grade modules

All parts are at least industrial temperature range of -40 °C to +85 °C. The module operating temperature range depends on customer design and cooling solution. Please contact us for options.

Weight

...

Revision History

Hardware Revision History

...

Notes

...

Hardware revision number is printed on the PCB board next to the module model number separated by the dash.

Image Removed

Image Removed

Document Change History

...

Date

...

Revision

...

Authors

...

Description

...

Disclaimer

...