Page History

| Scroll Ignore |

|---|

Download PDF Version of this Documentdocument. |

| Scroll pdf ignore | ||||

|---|---|---|---|---|

Table of Contents

|

Overview

| Scroll Only (inline) |

|---|

Refer to https://shop.trenz-electronic.de/en/Download/?path=Trenz_Electronic/carrier_boards/TE0701 for downloadable version of this manual and additional technical documentation of the product. |

The Trenz Electronic TE0701 Carrier Board is a base-board baseboard for 4 x 5 SoMs, which exposes the module's B2B - connector - pins to accessible connectors and provides a whole range of on-board components to test and evaluate TE 4 x 5 SoMs.

See page "4 x 5 cm carriers" to get information about the SoMs supported by the TE0701 Carrier Boardcarrier board.

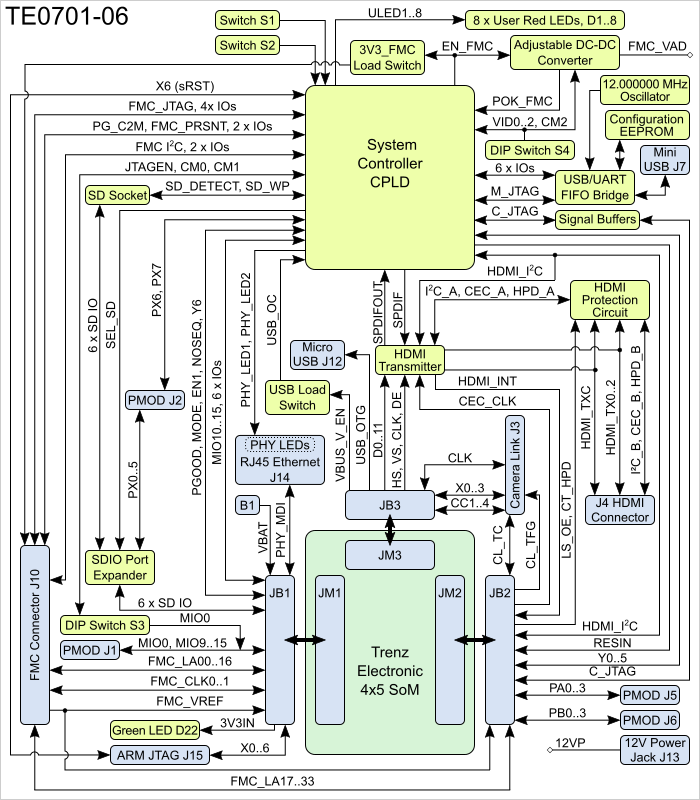

Block Diagram

Figure 1: TE0701-06 Block Diagramblock diagram.

Main Components

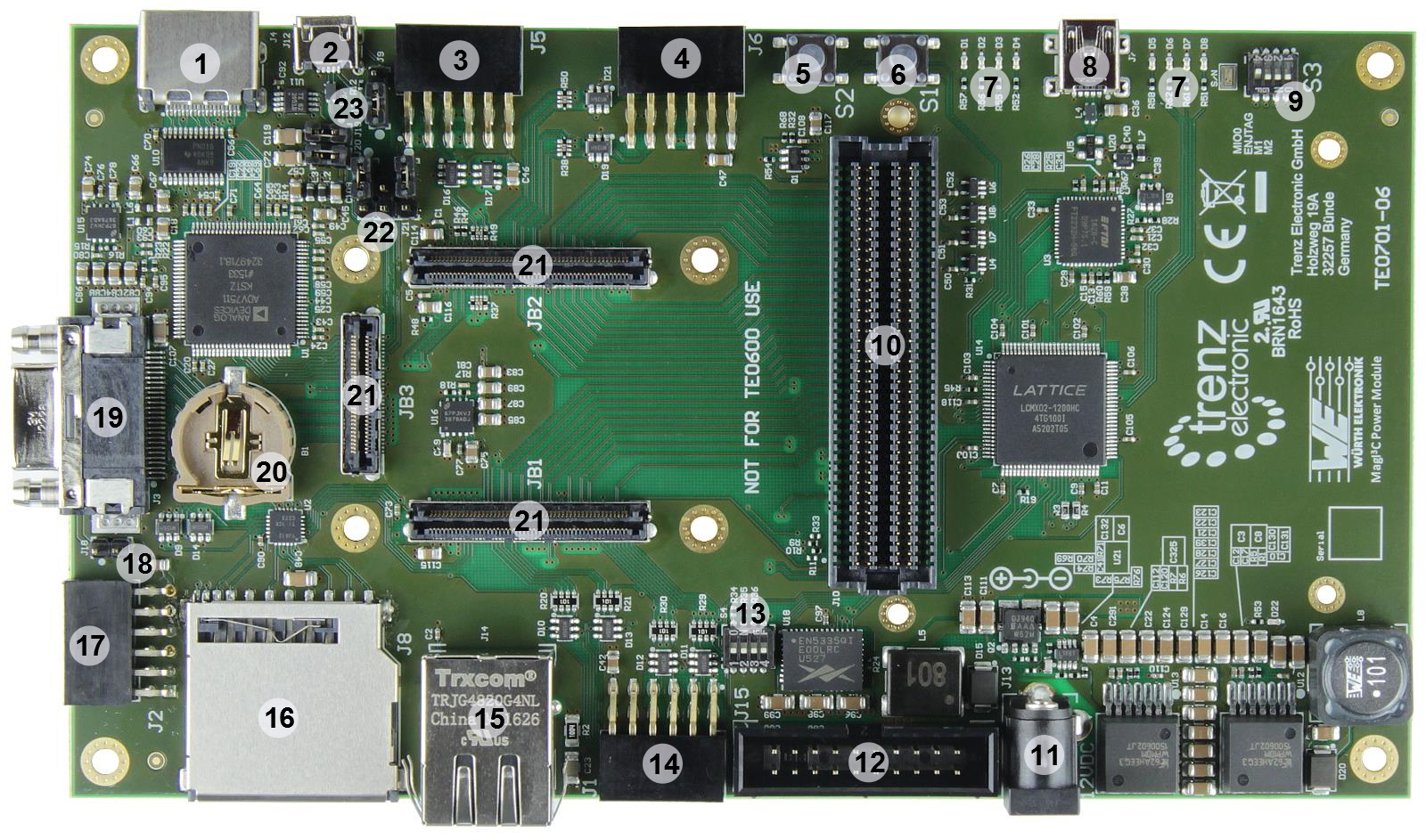

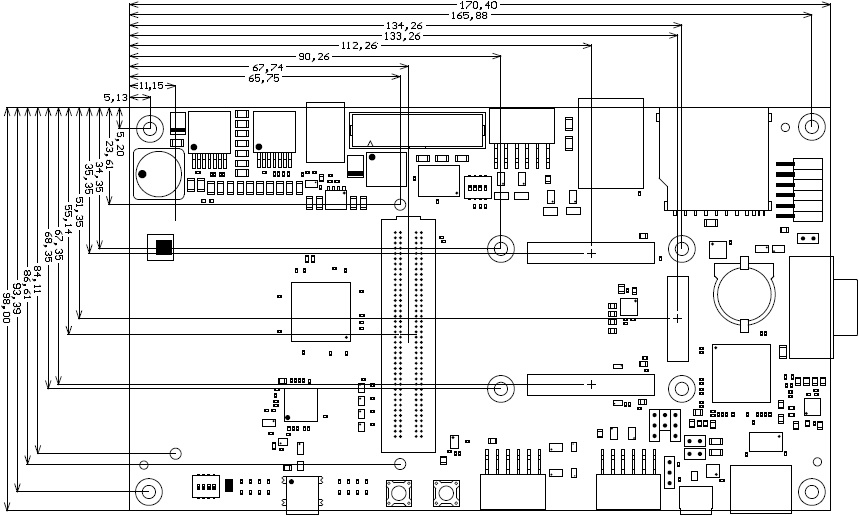

Figure 2: 4 x 5 SoM carrier board TE0701-06.

TE0701-06:

- HDMI Connector connector (1.4 HEAC Supportsupport)

- Micro-USB Connector connector (Devicedevice, Host host or OTG Modesmodes)

Pmod Connector connector for access to Zynq - module's PL IO-bank pins (4 LVDS - pairs, max. VCCIO - voltage: VIOTA)

- Pmod Connector for connector for access to Zynq - module's PL IO-bank pins (4 LVDS - pairs, max. VCCIO - voltage: FMC_VADJ)

- User Push Button push-button S2 ("RESTART" button by default)

- User Push Button push-button S1 ("RESET" button by default)

- User LEDs (function mapping depends on firmware of System - Controller - CPLD)

- Mini-USB Connector connector (USB JTAG and UART Interfaceinterface)

- User 4-bit DIP Switchswitch

- VITA 57.1 compliant FMC LPC Connector connector with digitally programmable FMC VADJ Power Supplypower supply

- Barrel jack for 12V Power Supplypower supply

- ARM JTAG Connector connector (DS-5 D-Stream) - PJTAG to EMIO multiplexing needed

- User 4-bit DIP Switch switch (provides the functionality to set adjust voltage of FMC_VADJ)

- Pmod Connector connector (J1, max. VCCIO - voltage: 3.3V): mapped to 8 Zynq PS MIO0 - bank - pins (MIO0, MIO9 to MIO15), 6 pins (MIO10 to MIO15) are additionally connected to TE0701 System - Controller - CPLD

- RJ45 GbE ConnectorGigabit Ethernet connector

- SD Card Connector - Zynq SDIO0 Bootable SD portconnector, Zynq SDIO0 controller, can be used to boot system

- Pmod connector Pmod Connector (J2, max. VCCIO - voltage: 3.3V): 6 pins (PX0 to PX5) can be multiplexed by Texas Instruments TXS02612RTWR SDIO Port Expander to MIO - pins of Zynq - module, 2 pins are connected to TE0701 System - Controller - CPLD (PX6 and PX7)

- Jumper J18

- Mini CameraLink ConnectorCamera Link connector

- Battery holder for CR1220 (RTC backup voltage)

- Trenz Electronic 4 x 5 module Socket modules high-speed connector strips (3x Samtec LSHM Series Connectorsseries connectors)

- Jumper J16, J17, J21

- Jumper J9, J19, J20

...

- Overvoltage-, undervoltage- and reversed- supply-voltage-protection

- Barrel jack for 12V power supply

- Carrier Board board System - Controller - CPLD Lattice MachXO2 1200HC, programable by programmable via Mini-USB JTAG - Interface J7

- Zynq - module programable by programmable via ARM -JTAG-Interface-Connector JTAG interface connector (J15) or by System - Controller - CPLD via Mini-USB JTAG -Interface interface J7 or JTAG -Interface interface on FMC -Connector connector J10

- Mini CameraLinkCamera Link

- RJ45 Gigabit Ethernet MagJack with 2 integrated LEDs.

- FPGA Mezzanine Card (FMC) Connector J10 for acces access to Zynq -Modulemodule's LVDS - pairs, operable with adjustable IO - voltage FMC_VADJ

- USB JTAG - and UART -Interface interface (FTDI FT2232HQ) with Mini-USB -Connector connector J7

- ADV7511 HDMI Transmitter transmitter with HDMI -Connector connector J4

- 8 x red user LEDs routed to System - Controller - CPLD, 8 x red

- 2 x user push-2 x user-push button routed to System - Controller - CPLD; by . By default configured as system "RESET" and "RESTART" button (depends on CPLD -Firmwarefirmware)

- 2 x 4-bit DIP -Switch for base-board-switch for baseboard configuration (3 switches routed to System - Controller - CPLD, 3 switches to set voltage of FMC_VADJ, 1 switch routed to Zynq - module (MIO0), 1 switch enables Mini-USB JTAG -Interface interface J7)

- PMOD-Connectors Pmod connectors to access Zynq - Module's LVDS - pairs and MIO -Pinspins

- Micro SD card socket, can be used to boot system

- Micro-USB -Interface interface (J12) connected to Zynq - module (Devicedevice, Host host or OTG modes)

- Trenz Electronic 4 x 5 module Socket (3 x modules high-speed connector strips (3x Samtec LSHM series connectors)

Interfaces and Pins

Micro SD Card Socket

Micro SD Card socket is not directly wired to the B2B connector pins, but through a Texas Instruments TXS02612 SDIO Port Expander, which is needed for voltage translation due to different voltage levels of the Micro SD Card and MIO-bank of the Xilinx Zynq - module. The Micro SD Card has 3.3V signal voltage level, but the MIO-bank on the Xilinx Zynq - module has VCCIO of 1.8V.The MIO-bank-pins, of the Zynq-module, which are dedicated to SDIO-interface, are also accessible by PMOD-Connector J2, which is configurable by the "SEL_SD"-signal of the System-Controller-CPLD. Connector J2 has max. VCCIO-voltage 3.3V.

With SD_SEL signal connected to the Texas Instruments TXS02612 SDIO Port Expander user can choose which port is accessible. Port B0 is connected to the Micro SD Card connector and B1 is connected to the Pmod J2 connector. SD_SEL signal can be controlled by the System Controller CPLD firmware.

Dual channel USB to UART/FIFO

The TE0701 Carrier Board carrier board has on-board high-speed USB 2.0 High Speed to UART/FIFO IC FT2232HQ from FTDI. Channel A can be used as JTAG -Interface interface (MPSSE) to program the System - Controller - CPLD, . Channel B can be used as UART -Interface interface routed to CPLD. There are also Also 6 additionally additional bus-lanes are connected to the System Controller CPLD and available for user-specific use.

There is also a standard 256 Byte -byte serial EEPROM connected to the FT2232HQ-chip available to store custom configuration setting.FT2232H chip pre-programmed with license code to support Xilinx programming tools.

| Warning |

|---|

Do not access the FT2232H EEPROM using FTDI programming tools, doing so will erase normally invisible user EEPROM content and invalidate stored Xilinx JTAG license. Without this license the on-board JTAG will not be accessible any more with any Xilinx tools. Software tools from FTDI website do not warn or ask for confirmation before erasing user EEPROM content |

| Note |

Warning: By using FTDI software tools, the 256 Byte user EEPROM may be deleted without confirmation. As a consequence, the Digilent license stored in that EEPROM will also be deleted. |

USB Interface

The TE0701 Carrier Board carrier board has two physical USB - connectors:

- J7 as miniMini-USB - connector J7 wired to on-board FTDI FT2232HQ chip.

- J12 as microMicro-USB - connector J12 wired to B2B connector JB3 (there is usually an USB-transceiver on the SoMsmost of the TE 4 x 5 cm SoMs have USB transceiver on-board).

JTAG Interface

JTAG access to the System Controller CPLD and Xilinx Zynq - module is provided via Minimini-USB JTAG Interface interface J7 (FTDI FT2232H) and controlled by DIP switch S3-3.

The JTAG port of the System Controller CPLD is enabled by setting switch S3-3 labeled as " ENJTAG " to the OFF - position.

LEDs

There are eight LEDs (L1 ULED1 to L8ULED8) available to the user. All LEDs are red colored and connected to the on-board System - Controller - CPLD. Their functions are function ls programmable and depend on the firmware of the System - Controller - CPLD. For detailed information, please refer to the documentation of the TE0701 Sytem-System Controller - CPLD.

| Note |

|---|

LED5 (L5D5) to LED8 (L8D8) are operating only when the corresponding power supply VIOTB (i.e., bank 1 of the on-board System Controller CPLD) is switched on. This can be accomplished on the one hand by connecting the FMC power supply FMC_VADJ to VIOTB (J21: 1,2-3), which is the default option, or on the other hand by connecting either 2.5V (J17: 1,2-3) or 3.3V (J17: 1-2,3) to VIOTB (J21: 1-2,3). Please note that for the first default option, the FMC power supply voltage must be set by the user. For detailed information how to set the voltage FMC_VADJ via I2CI2C, please refer to the documentation of the TE0701 Sytem-System Controller - CPLD. |

One green Green LED D22 shows the availability indicates presence of the 3.3V supply voltage of the TE0701 Carrier Boardpower from the SoM attached.

4-bit DIP-switch

...

S3

There Additionally, on the TE0701 Carrier Board there is a 4-bit DIP-switch (S3; see (9) in Figure 1) available. The default S3 switch mapping is as followsS3 with following default settings:

| Switch | Functionality |

|---|---|

| S3-1 | CM1: Mode pin 1 (routed to Carrier System Controller CPLD). |

| S3-2 | CM0: Mode pin 0 (routed to Carrier System Controller CPLD). |

| S3-3 | JTAGEN: Set to ON for normal JTAG operation. Must Has to be moved set to OFF position for TE0701 System - Controller - CPLD update onlyJTAG access. |

| S3-4 | MIO0: Readable input signal by System - Controller - CPLD and mounted TE07xx Modulemodule. |

Table 1: Configuration of DIP-switch S3 settings.

User Push-

...

buttons

On the TE0701 Carrier Board there are two push-buttons (S1 and S2) and are routed to the System - Controller - CPLD and available to the user. The default mapping of the push-buttons is as follows:

| Name | Default Mapping: |

|---|---|

| S1 | If S1 is pushed, the active-low RESet IN (RESIN) signal will be asserted. Note: This reset can also be forced by the FTDI USB - to - JTAG interface. |

| S2 | If S2 is pushed, the active-high Power ON (PON) signal (that is internally pulled-up) will be deassertedde-asserted, which can be considered as a "RESTART" button to switch off (push button) and on (release button) function as all on-module power supplies will be switched off (except 3.3VIN) . Note: The capability the switch to be enabled the first time will become active shortly after Power on Reset (POR). infoon button push and back on again on button release. The active-high PON signal is directly mapped to the active-high EN1 signal which is routed to the module's SC-System Controller CPLD (e.g., on the TE0720) and directly used (after deglitching)as a mandatory active-high enable signal to the power FET switch (3.3VIN ->, enabling on-module 3.3V )power supply output as well as theall other DC-DC converters (VIN -> 1.0V, 1.5V, 1.8V).on the module. |

Table 2: Description of the standard functionalitys default functions of user push-buttons S1 and S2.

The functionality function of the push-buttons depends depend on the System Controller CPLD - firmware. For detailed information of the function of the push-buttons, please refer to the documentation of the TE0701 System - Controller - CPLD.

Ethernet

The TE0701 Carrier Board has a RJ45 Gigabit Ethernet MagJack (J14) with two LEDs. On-board Ethernet MagJack J14 pins are routed to B2B connector JB1 via MDI. The center tap of the Magnetics magnetics is not connected to module's B2B connector. PHY LEDs are not connected directly to the module's B2B connectors as the 4 x 5 module have no dedicated PHY LED pins assigned. PHY LED's LEDs are connected to the TE0701 System - Controller - CPLD , that can route those LED's and can be routed to some of the module's I/O Pins. In that case the CPLD has to map the PHY LEDs to corresponding pinspins with firmware.

See documentation of the TE0701 System - Controller - CPLD to get information of the function of the PHY LEDs.

...

J5 and J6 Pmod signal routing is done as differential pairs for pins 1-2, 3-4, 7-8 , and 9-10.

Please use Master Pinout Pin-out Table table as primary reference for the pin mapping information.

...

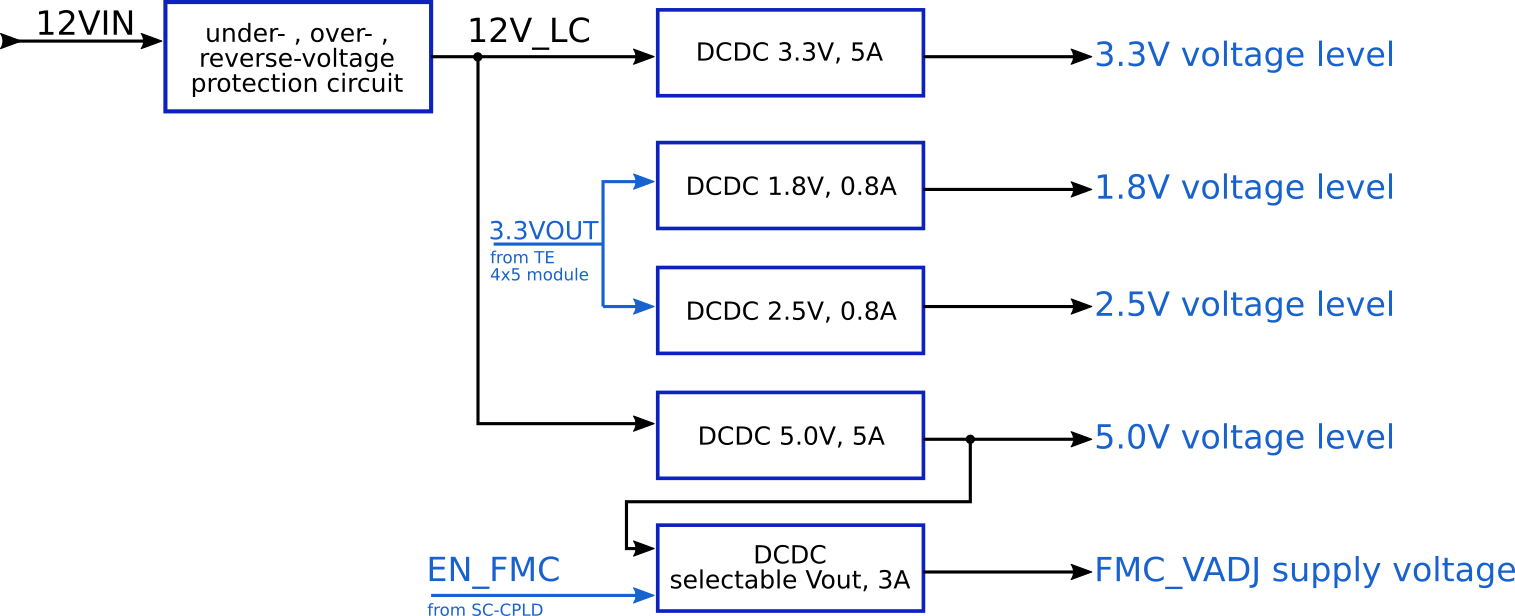

The on-board voltages 3.3V and 5.0V of the carrier board will be powered-brought up simultaneously after one singlewhen 12V power - supply with a nominal voltage of 12V is connected to the barrel jack J10.

The on-board voltages 1.8V and 2.5V will be powered brought up after the when module's 3.3V voltage - level has reached become stable state and 3.3VOUT is available on the B2B - connector JB2 , pins 9 and 11.

The PL IO-bank supply voltage FMC_VADJ will be available after the output of the 5.0V DC-DCDC-DC converter is active and the pin EN_FMC of the SC-System Controller CPLD is asserted.

Figure 3: TE0701-06 Powerpower-Up up sequence diagram.

TE0701 jumper and DIP switch overview

On the TE0701 carrier board different VCCIO configurations can be chosen by 7 jumpers and one dedicated 4-bit DIP-switch S4. The purpose Settings of the jumpers and the DIP-switch S4 of the Carrier Board will be explained in the following sectionsare explained below.

Configuring VCCIO

...

voltage for PL IO-bank of mounted 4 x 5 SoM

The base-board baseboard supply - voltages for the PL IO-banks of the SoM are selectable by the jumpers J16, J17 and J21. The DIP-switch S4 sets the adjustable base-board baseboard supply-voltage FMC_VADJ.

| Info |

|---|

The supply-voltage FMC_VADJ is user programmable via I2C.The setting I2C. Configuration of the adjustable voltage FMC_VADJ is done by the dedicated I2C-Bus with the lines "over dedicated I2C bus (lines HDMI_SCL " and " HDMI_SDA"). Therefore, a A control - byte has to be send sent to the 8-bit control register of the I2CI2C-to-GPIO - module of the System - Controller - CPLD. This module has the I2C-Address modules I2C address is 0x22. To enable FMC_VADJ on TE0701, bit 7 of the control - register should be set to 1. Note that the I2C-Bus I2C bus is shared with the I2C-Interface I2C interface of the HDMI - Controller. For detailed information how to set the voltage FMC_VADJ via I2CI2C, please refer to the documentation of the TE0701 Sytem-System Controller - CPLD. |

| Note |

|---|

There is also the possibility option to select fixed voltage of FMC_VADJ voltages by the with DIP-switch S4. Therefore, In this case there is no need to configure any bits on the 8-bit control register of the I2Cthe I2C-to-GPIO-module of the System - Controller - CPLD. Note: Switch S4 is also routed to the System - Controller - CPLD, hence the VCCIO - configuration can be registered by the CPLD. Switch S4-4 is not dedicated for FMC_VADJ setting, the functionality function of this switch depends on the SC-System Controller CPLD - firmware. |

Table 3

...

below describes switch S4 settings for different FMC_VADJ

...

voltages.

| S4-1 | S4-2 | S4-3 | FMC_VADJ Value |

|---|---|---|---|

| ON | ON | ON | 3.3V |

| OFF | ON | ON | 2.5V |

| ON | OFF | ON | 1.8V |

| OFF | OFF | ON | 1.5V |

| ON | ON | OFF | 1.25V |

Table 3: Switch S4 positions for fixed values of the FMC_VADJ voltage.

Configuring 12V Power Supply Pin on the CameraLink Camera Link Connector

Finally, a 12V power supply can be connected to pin 26 of the CameraLink by closing J18. However, this option is disabled by default (J18: OPEN).

Configuring Power Supply of the Micro-USB Connector (

...

device,

...

host or OTG

...

modes)

The TE0701 carrier board can be configured as a USB host. Hence, it must provide from 5.25V to 4.75V to the board side of the downstream connection (micro-USB port on J12; 13). To provide sufficient power, a TPS2051 power distribution switch is located on the carrier board in between the 5V power supply and the Vbus VBUS signal of the USB downstream port interface. If the output load exceeds the current-limit threshold, the TPS2051 limits the output current and pulls the overcurrent over-current logic output (OC_n) low, which is routed to the on-board CPLD. The TPS2051 is put into operation by setting J19 CLOSED. J20 provides an extra 100µF decoupling capacitor (in addition to 10µF) to further stabilize the output signal. Moreover, a series terminating resistor of either 1K (J9: 1-2, 3) or 10K (J9: 1, 2-3) is selectable on the "USB-VBUS" signal. Both signals, USB-VBUS and VBUS_V_EN (that enables the TPS2051 on "high") are routed (as well as the corresponding D+/- data lines) via the on-board connector directly to the USB 2.0 high-speed transceiver PHY on the mounted SoM, which is, in turn, connected to the Zynq FPGA. In summary, the default jumper settings are the following: J9: 1-2, 3 (1K series terminating resistor); J19: CLOSED (TPS2051 in operation); J20: CLOSED (100 µF added).

Additionally, the TE0701 carrier board is equipped with a second mini-USB port (J7; see (8) in Figure 1) that ) which is connected to a " USB to multi-purpose UART/FIFO IC " from FTDI (FT2232HQ) and provides a USB - to - JTAG interface between a host PC and the TE0701 carrier board and the Zynq - module, respectively. Because it acts as a USB function device, no power switch is required (and only a ESD protection must be provided) in this case.

Summary of VCCIO

...

configuration via jumpers

There are two base board baseboard supply - voltages VIOTA and VIOTB connected to the 4 x 5 SoM's PL IO-banksbank. The supply-voltages have following pin assignments on B2B-connectors:

base-board Baseboard supply - voltages | base-board Baseboard B2B connector-pins | standard Standard assignment of PL IO-bank supply - voltages on TE 4 x 5 module's B2B connectors | base-board Baseboard voltages and signals connected with |

|---|---|---|---|

| VIOTA | JB2-2, JB2-4, JB2-6 | VCCIOB (JM2-1, JM2-3) / VCCIOC (JM2-5) | HDMI_SCL, HDMI_SDA, HDMI_INT, J5 VCCIO |

| VIOTB | JB1-10, JB1-12, JB2-8, JB2-10 | VCCIOA (JM1-9, JM1-11) / VCCIOD (JM2-7, JM2-9) | VCCIO1 (System - Controller - CPLD pin 55, 73) |

Table 4: base-board Baseboard supply-voltages VIOTA and VIOTB

| Note |

|---|

Note: The corresponding PL IO-voltage supply voltages of the 4 x 5 SoM to the selectable base-board baseboard voltages VIOTA and VIOTB are depending on the mounted 4 x 5 SoM and varying in order of the used model. Refer to SoM's schematic to get schematics for more information about the specific pin assignment on module's B2B-connectors regarding PL IO-bank supply voltages and to the 4 x 5 Module integration Guide for VCCIO voltage options. |

Following table describes how to configure the base-board baseboard supply - voltages by with jumpers:.

base-board Baseboard supply voltages vs voltage - levels | VIOTA | VIOTB | USB-VBUS | 12V0_CL |

|---|---|---|---|---|

| 3V3 | J17:1-2, 3 & J16: open | J17: 1-2, 3 & J16: open & J21:1-2, 3 | - | - |

| 2V5 | J17:1, 2-3 & J16: open | J17:1, 2-3 & J16: open & J21: 1-2, 3 | - | - |

| FMC_VADJ | J17: open & J16: 1-2 | J21:1, 2-3 | - | - |

| 5V0 intern | - | - | J9:1-2, 3 & J19: 1-2 (J20: 1-2: additional decoupling-capacitor 100 µF) | - |

| Vbus VBUS extern | - | - | J9: 1, 2-3 & J19: open | - |

| 12V_LC | - | - | - | J18: 1-2 |

Table 5: Configuration of base-board baseboard supply-voltages via jumpers. Jumper-Notification: 'Jx: 1-2, 3' means pins 1 and 2 are connectedclosed, pin 3 is open. 'Jx: 1, 2-3' means pins 2 and 3 are connectedclosed, pin 1 is open.

| Note |

|---|

| It is recommended to set and measure the PL IO-bank supply - voltages before mounting of TE 4 x 5 module to avoid failures and damages to the functionality of the mounted SoM. |

Technical Specifications

Absolute Maximum Ratings

| Parameter | Min | Max | Units | Notes |

|---|---|---|---|---|

Vin VIN supply voltage | 11.4 | 12.6 | V | ANSI/VITA 57.1 FPGA Mezzazine Mezzanine Card (FMC) Standardstandard |

Storage Temperaturetemperature | -55 | 125 | °C | - |

Recommended Operating Conditions

| Parameter | Min | Max | Units | Notes |

|---|---|---|---|---|

| Vin VIN supply voltage | 11.4 | 12.6 | V | - |

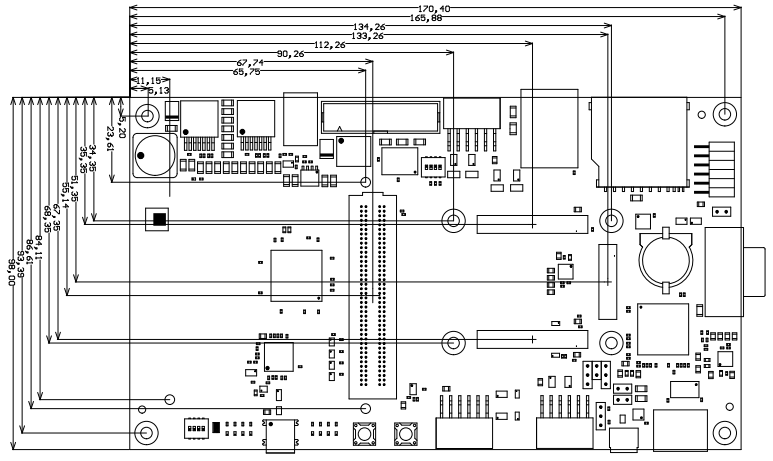

Physical Dimensions

Board size: PCB 170.4 mm × 98 mm. Notice that some parts the are hanging slightly over the edge of the PCB like the mini-USB - jacks (ca. 1.4 mm), the Ethernet RJ-45 jack (ca 2.2 mm) and the mini CameraLink connector (ca. 7 mm), which determine the total physical dimensions of the carrier board. Please download the assembly diagram for exact numbers.

Mating height of the module with standard connectors : is 8mm.

PCB thickness: ca. 1.65mm.

Highest part on the PCB is the Ethernet RJ-45 jack, which has an approximately 17 mm overall hightheight. Please download the step model for exact numbers.

All dimensions are given in mmmillimeters.

Figure 4: Physical Dimensions dimensions of the TE0701-06 carrier board.

Operating Temperature Ranges

...

Board operating temperature range depends also on customer design and cooling solution. Please contact us for options.

Weight

ca. 188 g - Plain board

Document Change History

g - Plain board.

Document Change History

| Date | Revision | Authors | Description | ||||

|---|---|---|---|---|---|---|---|

| 2017-05-20 | Jan Kumann | New physical dimensions drawing of the board. | |||||

| 2017-05-16 | V51 | Jan Kumann | A few overall improvements and corrections, new block diagram. | date | revision | authors | description|

| 2017-04-11 |

| Ali Naseri | added block diagram | ||||

| 2017-02-15 | V45

| Ali Naseri | added warning concerning the use of FTDI - tools | ||||

| 2017-02-15 | V40 | Ali Naseri | added power-on sequence diagram | ||||

| 2017-01-19 | V35 | Ali Naseri | correction of table 3 (switch-positions to adjust FMC_VADJ) inserted hint to set and measure the PL IO-bank supply-voltages

| ||||

| 2017-01-13 | V20 | Ali Naseri | added section for base-board baseboard supply - voltage configuration | ||||

| 2016-11-29 | V10

| Ali Naseri | TRM update due to new revision 06 of the carrier board. | ||||

| 2016-11-28 | V4 | Ali Naseri | TRM adjustment to the newest revision (05) of TE0701 Carrier Board. | ||||

| 2014-02-18 | 0.2 | Sven-Ole Voigt | TE0701-03 (REV3) updated | ||||

| 2014-01-05 | 0.1 | Sven-Ole Voigt | Initial release | ||||

| All | Sven-Ole Voigt, Ali Naseri |

Hardware Revision History

| Date | Revision | Notes | PCN | Documentation link |

|---|---|---|---|---|

| - | 06 | additional Additional Jumper J16 and switch S4 for setting VCCIO FMC_VADJ. | PCN-20161128 | |

| - | 05 | improved Improved manufacturing | TRM-TE0701-05 | |

| - | 04 | |||

| - | 03 | changed Changed DC/DC converters | ||

| - | 02 | Prototype | ||

| - | 01 | Prototype |

Figure 5: Hardware revision Numbernumber.

Hardware revision number is printed on the PCB board next to the module model number separated by the dash.

...

| Include Page | ||||

|---|---|---|---|---|

|