Page History

...

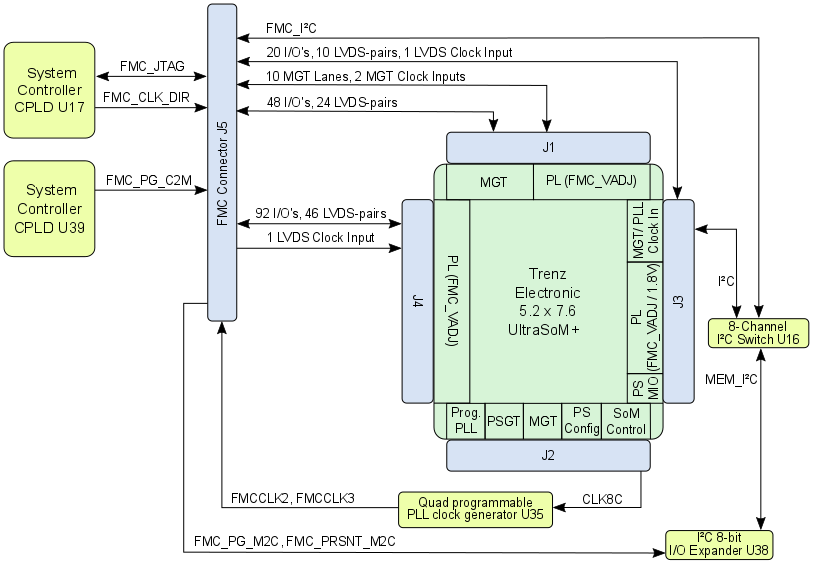

The I/O signals are routed from the FPGA banks as LVDS-pairs to the connector.

Figure 23: FMC HPC Connector

| FPGA Bank | I/O Signal Count | LVDS-pairs count | VCCO bank Voltage | Reference Clock Input from FMC Connector | Notes |

|---|---|---|---|---|---|

| Bank 48 | 20 | 10 | FMC_VADJ | 1 reference clock signal from FMC connector | - |

| Bank 64 | 46 | 23 | FMC_VADJ | 1 reference clock signal from FMC connector | bank's VREF-pin connected to FMC connector pin J5-H1 (VREF_A_M2C) |

| Bank 65 | 46 | 23 | FMC_VADJ | - | bank's VREF-pin connected to FMC connector pin J5-H1 (VREF_A_M2C) |

| Bank 66 | 48 | 24 | FMC_VADJ | - | bank's VREF-pin connected to FMC connector pin J5-H1 (VREF_A_M2C) |

...

| MGT Bank | Type | Count of MGT Lanes | Schematic Names / Connector Pins | MGT Bank's Reference Clock Inputs from FMC Connector |

|---|---|---|---|---|

| 228 | GTH | 4 GTH lanes | B228_RX3_P, B228_RX3_N, pins J5-A10, J5-A11 B228_RX2_P, B228_RX2_N, pins J5-A6, J5-A7 B228_RX1_P, B228_RX1_N, pins J5-A2, J5-A3 B228_RX0_P, B228_RX0_N, pins J5-C6, J5-C7 | 1 reference clock signal (B228_CLK0) from FMC connector Si5345 CLK3 of prog. PLL on mounted SoM internally on-module |

| 229 | GTH | 4 GTH lanes | B229_RX3_P, B229_RX3_N, pins J5-B12, J5-B13 B229_RX2_P, B229_RX2_N, pins J5-B16, J5-B17 B229_RX1_P, B229_RX1_N, pins J5-A18, J5-A19 B229_RX0_P, B229_RX0_N, pins J5-A14, J5-A15 | 1 reference clock signal (B229_CLK0) from FMC connector Si5345 CLK2 of prog. PLL on mounted SoM internally on-module |

| 230 | GTH | 2 GTH lanes | B230_RX1_P, B230_RX1_N, pins J5-B4, J5-B5 B230_RX0_P, B230_RX0_N, pins J5-B8, J5-B9 | Si5345 CLK1 of prog. PLL on mounted SoM internally on-module |

Table 23: FMC connector pin-outs of available MGT-lanes of the MPSoC

...

| Clock Signal Schematic Name | FMC Connector Pins | Direction | Clock Source | Notes |

|---|---|---|---|---|

| B228_CLK0 | J5-D4 / J5-D5 | in | FMC Connector J5 | clock signal to MGT bank 228 |

| B229_CLK0 | J5-B20 / J5-B21 | in | FMC Connector J5 | clock signal to MGT bank 229 |

| FMCCLK2 | J5-K4 / J5-K5 | out | Carrier Board PLL SI5338A U35, CLK2 | - |

| FMCCLK3 | J5-J2 / J5-J3 | out | Carrier Board PLL SI5338A U35, CLK3 | - |

| B64_L14_P / B64_L14_N | J5-H4 / J5-H5 | in | FMC Connector J5 | bank 64 clock capable pin-pair |

| B48_L6_P / B48_L6_N | J5-G2 / J5-G3 | in | FMC Connector J5 | bank 48 clock capable pin-pair |

Table 34: FMC connector pin-outs for reference clock output

...

| Interfaces | I/O Signal Count | Pin schematic Names / FMC Pins | Connected to | Notes |

|---|---|---|---|---|

| JTAG | 5 | FMC_TCK, pin J5-D29 FMC_TMS, pin J5-D33 FMC_TDI, pin J5-D30 FMC_TDO, pin J5- D31 | SC CPLD U17, bank 1 | VCCIO: 3V3SB TRST_L, pin J5-D34 pulled-up to 3V3_PER |

| I²C | 2 | FMC_SCL, pin J5-C30 FMC_SDA, pin J5-C31 | I²C Switch U16 | I²C-lines pulled-up to 3V3_PER |

| Control Lines | 3 | FMC_PRSNT_M2C, pin J5-H2 FMC_PG_C2M, pin J5-D1 (3V3_PER pull-up) FMC_PG_M2C, pin J5-F1 (3V3_PER pull-up) FMC_CLK_DIR, pin J5-B1 (pulled-down to GND) | I²C I/O Expander U38 SC CPLD U39, bank 0 I²C I/O Expander U38 SC CPLD U17, bank 1 | 'PG' = 'Power Good'-signal 'C2M' = carrier to (mezzanine) module 'M2C' = (mezzanine) module to carrier |

Table 45: FMC connector pin-outs of available interfaces to the System Controller CPLD

...

| VCCIO Schematic Name | FMC Connector J5 Pins | Notes |

|---|---|---|

| 12V | C35/C37 | extern 12V power supply |

| 3V3_PER | D32/D36/D38/D40/C39 | 3.3V peripheral supply voltage |

| FMC_VADJ | H40/G39/F40/E39 | adjustable FMC VCCIO voltage, supplied by DC-DC converter U8 |

Table 56: Available VCCIO voltages on FMC connector

...

| MIO | Configured as | System Controller CPLD | Notes |

|---|---|---|---|

| 0..12 | Dual QSPI | - | Dual Flash Memory on TE0808 SoM; Bootable |

| 13..23 | SD0: eMMC | - | eMMC Memory U2; Bootable |

| 24, 25 | - | CPLD (U39) MUXED | - |

| 26..29 | - | CPLD (U17 MUXED | Bootable JTAG (PJTAG0) possible |

| 30 | force reboot after FSBL-PLL config for PCIe | CPLD (U39) MUXED | - |

| 31 | PCIe reset | CPLD (U39) MUXED | - |

| 32 | - | CPLD (U39) MUXED | - |

| 33 | - | CPLD (U39) MUXED | - |

| 34..37 | - | CPLD (U39) MUXED | - |

| 38, 39 | I2C0 | - | - |

| 40 | forwarded to PWRLED_P / LED_P | CPLD (U39) MUXED | - |

| 41 | - | - | - |

| 42, 43 | UART0 | CPLD (U39) MUXED | - |

| 44 | SD_WP to FPGA | CPLD (U39) MUXED | - |

| 45..51 | SD1: SD | - | Bootable MikroSD / MMC Card |

| 52..63 | USB0 | - | - |

| 64..75 | GEM3 | - | Ethernet RGMII |

| 76, 77 | MDC / MDIO | - | Ethernet RGMII |

Table 57: MIO Assignment

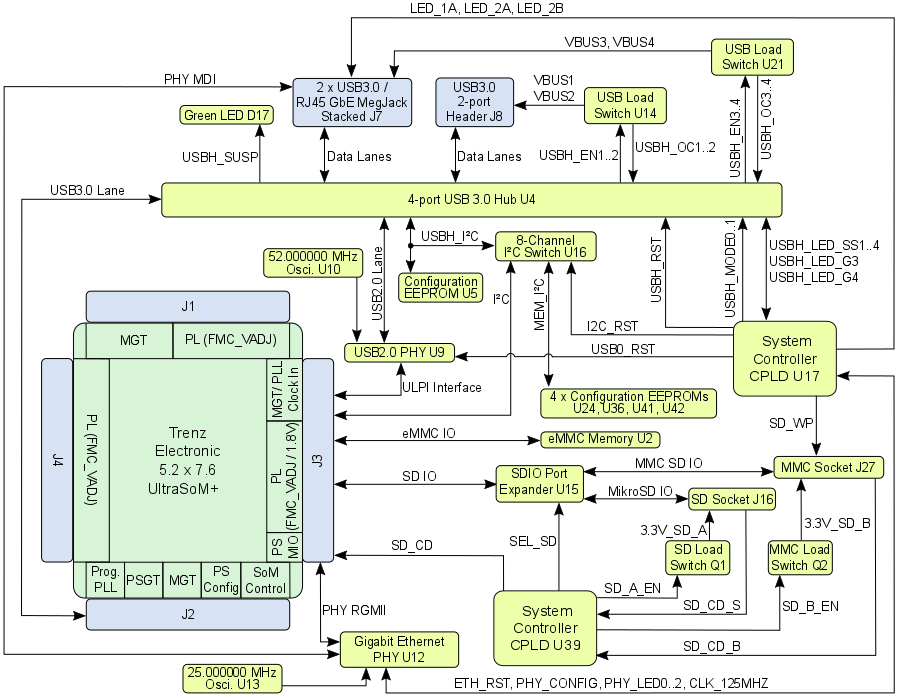

On the carrier board there are up to

Following interfaces are provided by the MIO bank of the Zynq Ultrascale+ MPSoC:

- 4 USB3.0

...

- Superspeed ports (downward compatible to USB2.0

...

- Highspeed)

- SDIO port with muxed MikroSD and MMC Card Socket

- Gigabit Ethernet interface connected per RGMII

- eMMC interface

- Master I²C interface to on-board peripherals

The block-diagram below visualizes the interfaces of the MIO bank at the Zynq Ultrascale+ MPSoC and their associated on-board peripherals.

Figure 4: TEBF0808 MIO Interfaces

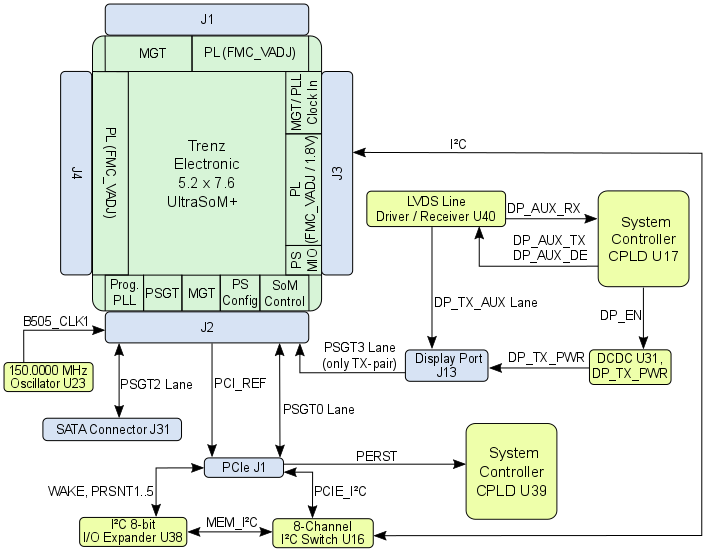

MPSoC's PS GT Bank 505 Interfaces

On the PS GT Bank 505 provides beside the USB3.0 Lane also following interfaces:

- SATA (PS GT bank 505, MGT2 Lane)

- Display-Port (PS GT bank 505, MGT3 Lane, only TX-pair routed)

- PCI Express (PS GT bank 505, MGT0 Lane)

| Function | MGT Lane | Required Ref Clock | Clock Source | Comment |

|---|---|---|---|---|

| PCIe | PS 0 | 100 MHz | Si5345 CLK0 of prog. PLL on mounted |

On the Upstream-side, this chip is connected to the MGT1 lane of MPSoC's PG GT bank 505 to establish the USB3.0 data lane. For the USB2.0 interface, the USB3.0 HUB U4 is connected to the on-board USB2.0 PHY U9. The USB2.0 PHY U9 is connected per ULPI interface (MIO pins 52..63) to MPSoC's MIO bank 501.

Further interfaces of the MIO bank:

- SDIO port with muxed MikroSD and MMC Socket

- Gigabit Ethernet connected per RGMII

- eMMC Memory

- 4 x user configuration EEPROMs with I²C interface

Following block-diagram visualizes the interfaces of the MIO bank at the Zynq Ultrascale+ MPSoC and their associated on-board peripherals.

Figure 3: TEBF0808 MIO Interfaces

MPSoC's PS GT Bank 505 Interfaces

On the PS GT Bank 505 provides beside the USB3.0 Lane also following interfaces:

...

| Function | MGT Lane | Required Ref Clock | Clock Source | Comment |

|---|---|---|---|---|

| PCIe | PS 0 | 100 MHz | Si5345 CLK0 of prog. PLL on mounted SoM | wired on carrier board to PCIe connector J1 |

| USB3 | PS 1 | 100 MHz | Si5345 CLK4 of prog. PLL on mounted SoM | internally on-module wired, |

| SATA | PS 2 | 150 MHz | On-board oscillator U23 | optional: Si5345 CLK4 of prog. PLL on mounted SoM |

| DP.0 | PS 3 | 27 MHz | Si5345 CLK5 of prog. PLL on mounted SoM | DisplayPort GT SERDES Clock Si5345 CLK6 of prog. PLL on mounted SoM |

Table 68: PS GT Lane Assignment

Following block diagram shows the wiring of the MGT Lanes of the PS GT bank 505 to the particular high speed data interfaces:

Figure 45: TEBF0808 PS GT Bank 505 Interface

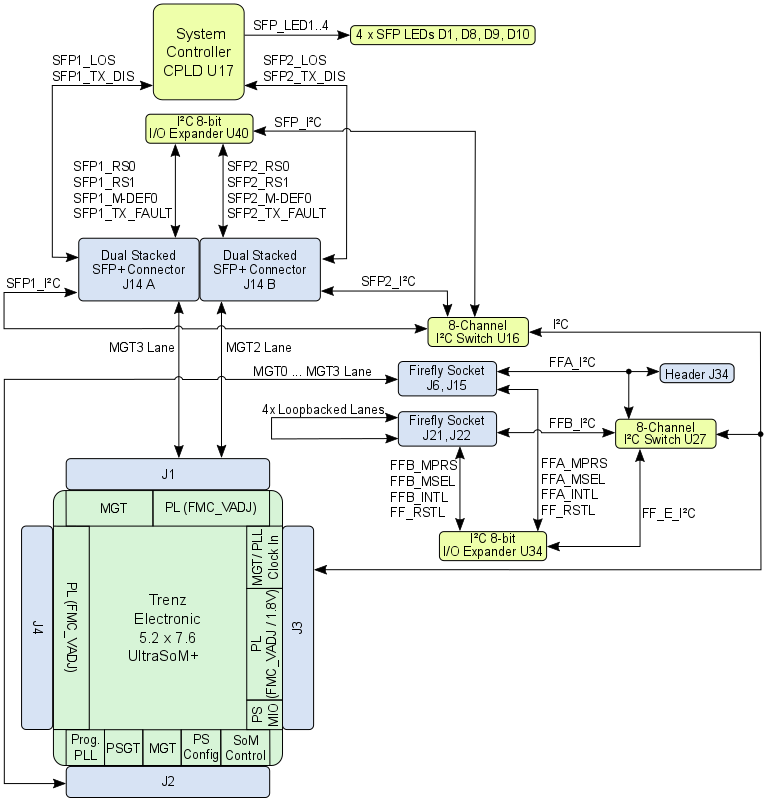

...

| Function | MGT Lane | Required Ref Clock | Clock Source | Comment |

|---|---|---|---|---|

| FireFly | B128 MGT Lanes 0..3 | - | Si5345 CLK6 of prog. PLL on mounted SoM | internally on-module wired |

| SFP | B230 MGT Lane 2 | 125 / 156.25 MHz | Si5345 CLK7 of prog. PLL on mounted SoM | wired on carrier board |

| SFP | B230 MGT Lane 3 | 125 / 156.25 MHz | Si5345 CLK7 of prog. PLL on mounted SoM | wired on carrier board |

Table 69: MGT Lane Assignment

Following block diagram show the wiring of the MGT lanes to the particular interface connectors:

Figure 56: TEBF0808 MGT Interfaces

...

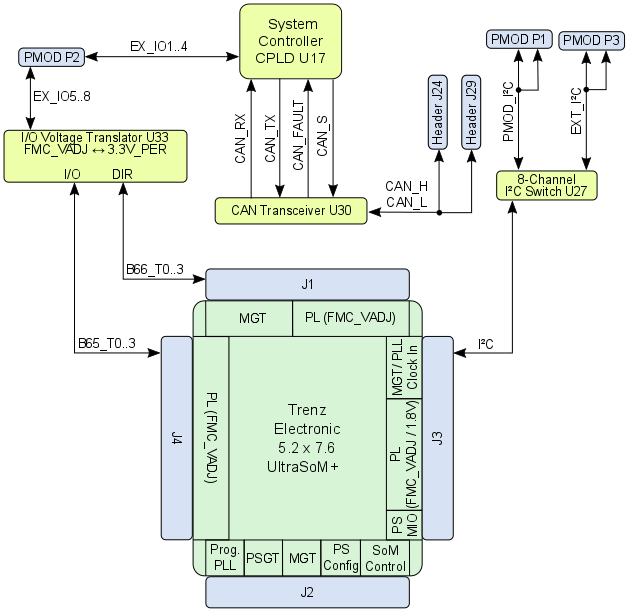

| PMOD | Interface | Connected with | Notes |

|---|---|---|---|

| P1 | GPIO | HP Bank 65 of MPSoC (4 I/O's, B65_T0 ... B65_T3), System Controller CPLD U17 (4 I/O's, EX_IO1 ... EX_IO4) | Voltage translation via IC U33 with direction control, only singled-ended signaling possible |

| P2 | I²C | 8-channel I²C Switch U27 | Accessible on MPSoC's I²C interface through I²C switch U27 |

| P3 | I²C | 8-channel I²C Switch U27 | Accessible on MPSoC's I²C interface through I²C switch U27 |

Table 710: PMOD Pin Assignment

Figure 67: TEBF0808 CAN Interfaces, PMOD

...

| Header | Pin Name | Function | Connected to | Notes |

|---|---|---|---|---|

| J10 | Pin 1, HD LED+ | HD LED Anode | SC CPLD U39 | Reset und Power Switch-pins are also connected to switch buttons S1 and S2 |

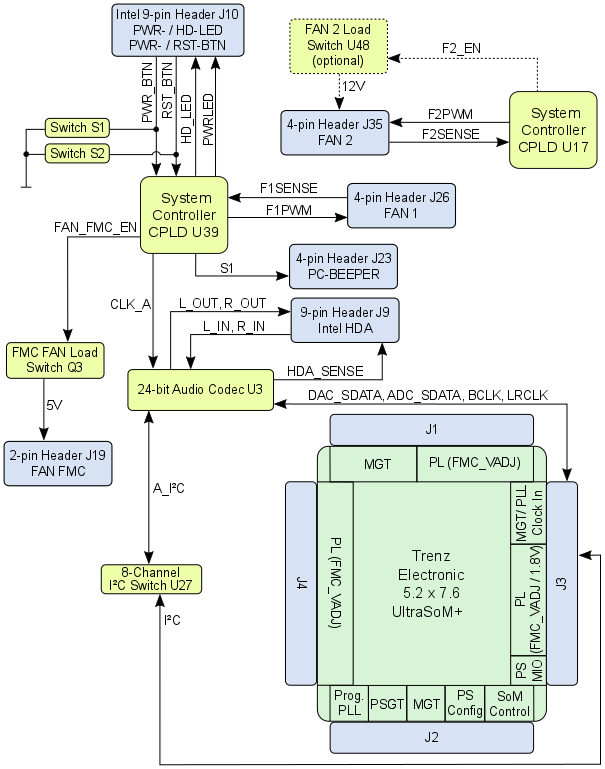

| J9 | Pin 1, PORT1L | Microphone Jack Left Microphone Jack Right Audio Out Jack Left Audio Out Jack Right Jack Detect / Mic in Ground | 24-bit Audio Codec IC U3 | - |

| J23 | Pin 1, 3V3SB Pin 4, S1 | 3.3V DC Supply PC compatible Beeper | SC CPLD U39 | - |

| J26 | Pin 1, GND | Ground 12V DC Supply RPM PWM | SC CPLD U39 | 4-wire PWM FAN connector |

| J35 | Pin 1, GND | Ground 12V DC Supply RPM PWM | SC CPLD U39 | 4-wire PWM FAN connector |

| J19 | Pin 1, GND | Ground 5V DC Supply | Load Switch Q3 (5V DC) | 2-wire FAN connector Fan off/on switchable by signal 'FAN_FMC_EN' on SC CPLD U39 |

Table 811: PC compatible Headers

Figure 78: TEBF0808 PC Compatible Headers

...

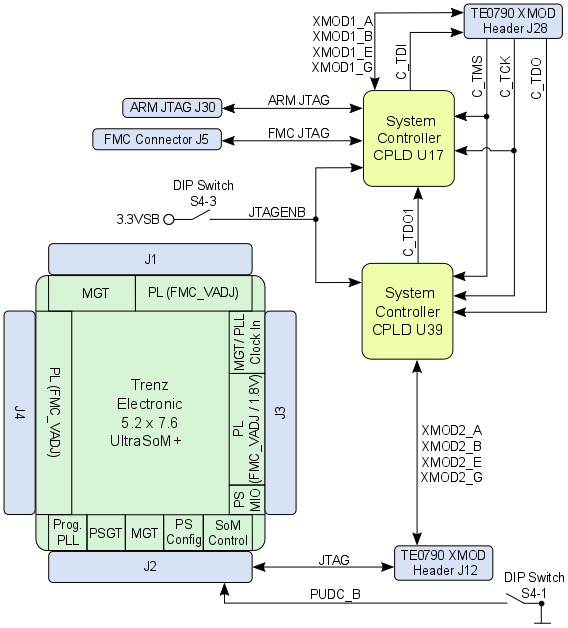

XMOD-Header J12 is designated to program the Zynq Ultrascale+ MPSoC via USB interface, the 4 GPIO/UART pins (XMOD2_A/B/E/G) of this header are routed to the System Controller CPLD U39.

Figure 89: TEBF0808 JTAG interfaces

...

| Boot Mode | MIO5 (BOOTMODE_1) | MIO4 (BOOTMODE) | MIO3 | Note |

|---|---|---|---|---|

JTAG | 0 | 0 | 0 | - |

| NOR | 0 | 0 | 1 | MIO3 pin is shared with QSPI Flash Memory (QSPI-DQ1) |

| NAND | 0 | 1 | 0 | - |

| QSPI Flash Memory | 1 | 0 | 0 | standard mode in current configuration |

| SD-Card | 1 | 1 | 0 | SD-Card on base board necessary |

Table 1112: Selectable boot modes

In delivery state of the SoM the boot mode depends on the configured SC-CPLD firmware. The current mode is set to boot from the QSPI Flash Memory.

...

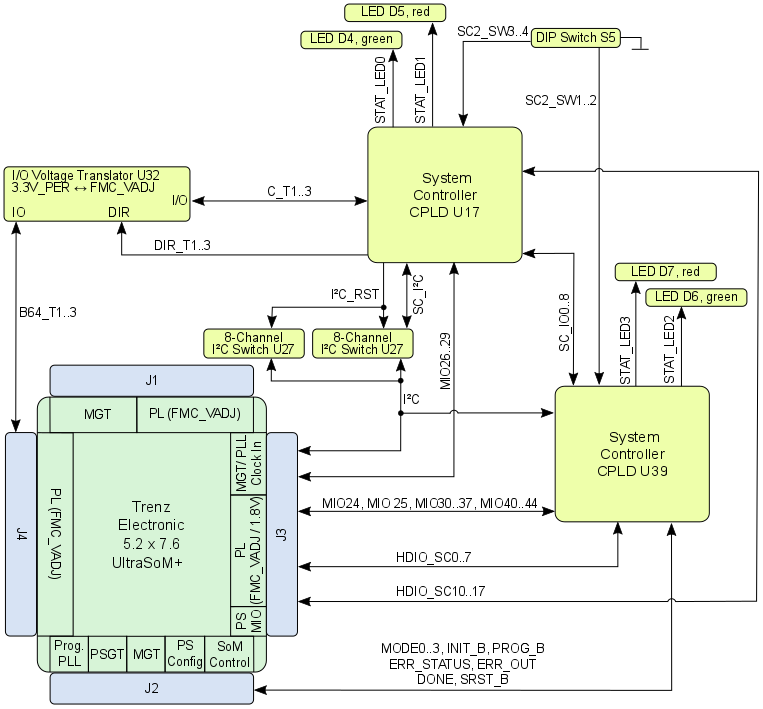

Both Sytem Controller CPLDs are connected to the Zynq Ultrascale+ MPSoC through MIO and also Programmable Logic pins, PL IO-bank pins and I²C interface. The CPLDs are connected with each other through the IO pins SC_IO0 ... SC_IO8.

The functionalities and configuration of the pins depend on the CPLDs' firmware. The documentations of the firmware of SC CPLD U17 and SC CPLD U39 contains detailed information on this matter.

Following block diagram visualizes the connection of the SC CPLDs with the Zynq Ultrascale+ MPSoC via PS (MIO) and , PL bank pins and I²C interface.

Figure 810: TEBF0808 System Controller CPLDs

...

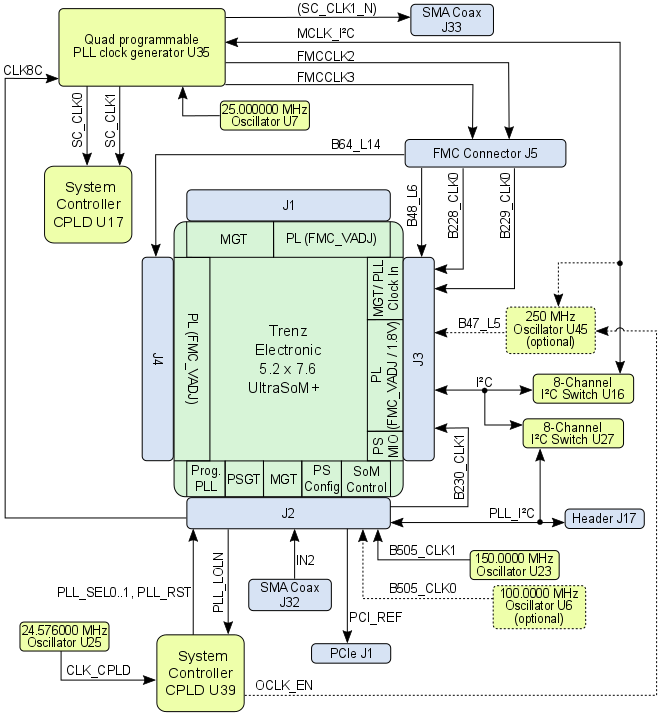

| Si5338A (U35) Input | Signal Schematic Name | Note |

|---|---|---|

IN1/IN2 | CLK8_P, CLK8_N | Reference clock signal from Si5345 (CLK8 of prog. PLL on mounted SoM) |

IN3 | reference clock signal from oscillator SiTime SiT8008BI (U7) | 25.000000 MHz fixed frequency. |

IN4/IN6 | pins put to GND | LSB (pin 'IN4') of the default I²C-adress 0x70 not activated. |

IN5 | not connected | - |

| Si5338A (U35) Output | Signal Schematic Name | Note |

CLK0 A/B | SC_CLK0 | Reference clock signal to SC CPLD U17 (single-ended signaling) |

CLK1 A/B | SC_CLK1 | Reference clock signal to SC CPLD U17 (single-ended signaling) |

CLK2 A/B | FMCCLK2_P, FMCCLK2_N | Clock signal routed to FMC connector J5, pins J5-K4 / J5-K5 |

| CLK3 A/B | FMCCLK3_P, FMCCLK3_N | Clock signal routed to FMC connector J5, pins J5-J2 / J5-J3 |

Table 913: Pin description of PLL clock generator Si5338A

Figure 911: Clocking Configuration of TE0808 SoM on TEBF0808 Carrier Board

...

| Clock Source | Schematic Name | Frequency | Clock Input Destination |

|---|---|---|---|

| SiTime SiT8008BI oscillator, U10 | USB0_RCLK | 52.000000 MHz | USB 2.0 transceiver PHY U9, pin 26 |

| SiTime SiT8008BI oscillator, U13 | ETH_CLK | 25.000000 MHz | Gigabit Ethernet PHY U12, pin 34 |

| SiTime SiT8008BI oscillator, U7 | - | 25.000000 MHz | Quad PLL clock generator U35, pin 3 |

| DSC1123 oscillator, U23 | B505_CLK1 | 150.0000 MHz | PS GT Bank 505, dedicated for SATA interface |

DSC1123 oscillator, U6 optional, not equipped | B505_CLK0 | 100.0000 MHz | PS GT Bank 505, dedicated for USB interface |

Silicon Labs 570FBB000290DG, U45 optional, not equipped | B47_L5 (LVDS) | 250.MHz | HD Bank 47 clock capable input pins |

| SiTime SiT8008BI oscillator, U25 | CLK_CPLD | 25.576000 MHz | System Controller CPLD U35, pin 128 |

Table 1014: Reference clock signal oscillators

...

| PHY Pin | Connected to | Notes |

|---|---|---|

| ULPI | PS bank MIO52 ... MIO63 | Zynq Ultrascale+ USB0 MIO pins are connected to the PHY |

| REFCLK | - | 52MHz from on board oscillator (U9) |

| REFSEL[0..2] | - | All pins set to GND selects the external reference clock frequency (52.000000 MHz) |

| RESETB | SC CPLD U17 | Low active USB PHY Reset (pulled-up to PS_1.8V). |

| DP, DM | 4-port USB3.0 Hub U4 | USB USB2.0 data lineslane |

| CPEN | - | External USB power switch active-high enable signal |

| VBUS | 5V | Connected to USB VBUS via a series of resistors, see schematic |

| ID | - | For an A-device connect to the ground. For a B-device, leave floating |

Table 1115: USB PHY interface connections

...

| PHY Pin | Connected to | Notes |

|---|---|---|

| MDC/MDIO | PS bank MIO76, MIO77 | - |

| PHY LED0..1 | SC CPLD U17, pin 67,86 | see schematic for details, forwarded to RJ45 GbE MagJack J7 |

| PHY_LED2 / INTn: | SC CPLD U17, pin 85 | Active low interrupt line |

| PHY_CLK125M | SC CPLD U17, pin 70 | 125 MHz Ethernet PHY clock out |

| CONFIG | SC CPLD U17, pin 65 | Permanent logic high |

| RESETn | SC CPLD U17, pin 62 | Active low reset line |

| RGMII | PS bank MIO64 ... MIO75 | Reduced Gigabit Media Independent Interface |

| SGMII | - | Serial Gigabit Media Independent Interface |

| MDI | RJ45 GbE MagJack J7 | Media Dependent Interface |

Table 1216: Ethernet PHY interface connections

...

For this purpose, the TEBF0808 carrier board is equipped with two 8-channel I²C switches provided by TCA9548A from Texas Instruments, together creating up to 16 switched I²C channels.

Refer to the data sheet of the TCA9548A chip how to address and and transmit data to the I²C slave devices through this switches.

The I2C bus works internally on-module with reference voltage 1.8V, it is connected to the PS I2C interface via PS MIO bank 501, pins MIO38 and MIO39, configured as master.

| MIO | Signal Schematic Name | Notes |

|---|---|---|

| 38 | I2C_SCL | 1.8V reference voltage |

| 39 | I2C_SDA | 1.8V reference voltage |

Table 1317: MIO-pin assignment of the module's I2C interface

I2C addresses for on-board slave devices are listed in the table below:

| I²C Slave Devices | I2C I²C Slave Address | Schematic Names of I²C Bus Lines | I²C Switch |

|---|---|---|---|

| 8-channel I²C switch U16 | 0x73 | I2C_SDA / I2C_SCL | - |

| 8-channel I²C switch U27 | 0x77 | I2C_SDA / I2C_SCL | - |

| On-module Quad programmable PLL clock generator Si5345 | 0x69 | PLL_SDA / PLL_SCL | U27 |

| Configuration EEPROM U24 | 0x54 | MEM_SDA / MEM_SCL | U16 |

| Configuration EEPROM U36 | 0x52 | MEM_SDA / MEM_SCL | U16 |

| Configuration EEPROM U41 | 0x51 | MEM_SDA / MEM_SCL | U16 |

| Configuration EEPROM U22 | 0x50 | MEM_SDA / MEM_SCL | U16 |

| 8-bit I²C IO Expander U44 | 0x26 | SFP_SDA / SFP_SCL | U16 |

| 24-bit Audio Codec U3 | 0x38 | A_I2C_SDA / A_I2C_SCL | U27 |

| 4-port USB3.0 Hub configuration EEPROM U5 | 0x51 | USBH_SDA / USBH_SCL | U16 |

| 4-port USB3.0 Hub | 0x60 | USBH_SDA / USBH_SCL | U16 |

| 8-bit I²C IO Expander U38 | 0x27 | MEM_SDA / MEM_SCL | U16 |

| On-board Quad programmable PLL clock generator U35 Si5338 | 0x70 | MCLK_SDA / MCLK_SCL | U16 |

| 8-bit I²C IO Expander U34 | 0x24 | FF_E_SDA / FF_E_SCL | U27 |

| SC CPLD U17, bank 3, pins 13 (SDA), 14 (SCL) | User programmable | SC_SDA / SC_SCL | U27 |

| SC CPLD U39, bank 2, pins 52 (SDA), 50 (SCL) | User programmable | I2C_SDA / I2C_SCL | - |

Table 1418: On-board peripherals' I2C-interfaces device slave addresses

There are further I²C interfaces connected to the 8-channel I²C switches U16 and U27, which are provided by connectors with I²C interface. The I²C slave addresses depend on the devicedevices, which are attached to this connectors:

| Connector | Schematic Names of I²C Bus Lines | I²C Switch |

|---|---|---|

| PCIe Connector J1 | PCIE_SDA / PCIE_SCL | U16 |

| SFP+ Connector J14A | SFP1_SDA / SFP1_SCL | U16 |

| SFP+ Connector J14B | SFP2_SDA / SFP2_SCL | U16 |

| FireFly Connector J15 | FFA_SDA / FFA_SCL | U27 |

| FireFly Connector J22 | FFB_SDA / FFB_SCL | U27 |

| FMC Connector J5 | FMC_SDA / FMC_SCL | U16 |

| PMOD Connector P1 | PMOD_SDA / PMOD_SCL | U27 |

| PMOD Connector P3 | EXT_SDA / EXT_SCL | U27 |

Table 1519: On-board connectors' I2C-interfaces overview

Configuration EEPROMs

A Microchip 24AA025E48 serial EEPROM (U23) contains a globally unique 48-bit node address, which is compatible with EUI-48(TM) specification. The device is organized as two blocks of 128 x 8-bit memory. One of the blocks stores the 48-bit node address and is write protected, the other block is available for application use. It is accessible over I2C bus with slave device address 0x53.

The TEBF0808 carrier board contains several EEPROMs for configuration and general user purposes. The EEPROMs are provided by Microchip and all have I²C interfaces:

| EEPROM Modell | Schematic Designator | Memory Density | Purpose |

|---|---|---|---|

| 24LC128-I/ST | U24 | 128 Kbit | user |

| 24AA025E48T-I/OT | U36 |

| 2 Kbit | user | ||

| 24AA025E48T-I/OT | U41 | 2 Kbit | user |

| 24AA025E48T-I/OT | U42 | 2 Kbit | user |

| 24LC128-I/ST | U5 | 128 Kbit | USB3.0 |

| Hub U4 |

| configuration memory |

Table 1620: On-board configuration EEPROMs overview

4-port USB3.0 Hub

The System Controller CPLD (U2) is provided by Lattice Semiconductor LCMXO2-256HC (MachXO2 Product Family). The SC-CPLD is the central system management unit where essential control signals are logically linked by the implemented logic in CPLD firmware, which generates output signals to control the system, the on-board peripherals and the interfaces. Interfaces like JTAG and I2C between the on-board peripherals and to the FPGA-module are by-passed, forwarded and controlled by the System Controller CPLD.

Other tasks of the System Controller CPLD are the monitoring of the power-on sequence and to display the programming state of the FPGA module.

CAN FD Transceiver

On-board QSPI flash memory (U14) on the TE0745-02 is provided by Micron Serial NOR Flash Memory N25Q256A with 256 Mbit (32 MByte) storage capacity. This non volatile memory is used to store initial FPGA configuration. Besides FPGA configuration, remaining free flash memory can be used for user application and data storage. All four SPI data lines are connected to the FPGA allowing x1, x2 or x4 data bus widths. Maximum data rate depends on the selected bus width and clock frequency used.

eMMC Memory

On-board Gigabit Ethernet PHY (U7) is provided with Marvell Alaska 88E1512 IC (U8). The Ethernet PHY RGMII interface is connected to the Zynq Ethernet0 PS GEM0. I/O voltage is fixed at 1.8V for HSTL signaling. The reference clock input of the PHY is supplied from an on-board 25.000000 MHz oscillator (U9), the 125MHz output clock signal CLK_125MHZ is connected to the pin J2-150 of B2B connector J2.

24-bit Audio Codec

Hi-speed USB ULPI PHY (U32) is provided with USB3320 from Microchip. The ULPI interface is connected to the Zynq PS USB0 via MIO28..39, bank 501 (see also section). The I/O voltage is fixed at 1.8V and PHY reference clock input is supplied from the on-board 52.000000 MHz oscillator (U33).

SDIO Port Expander

On the carrier board there are up to 4 USB3.0 Super Speed ports available, which are also downward compatible to USB2.0 High Speed ports. The USB3.0 ports are provided by Cypress Semiconductor CYUSB3324 4-port USB3.0 Hub controller U4. The pin-strap configuration option of the USB3.0 Hub is disabled, so this controller gets the configuration data and parameter from the configuration EEPROM U5. The I²C interface of the EEPROM and the controller is also accessible by the Zynq Ultrascale+ MPSoC through I²C switch U16.

On the Upstream-side, this controller is connected to the MGT1 lane of MPSoC's PS GT bank 505 to establish the USB3.0 data lane. For the USB2.0 interface, the controller is connected to the on-board USB2.0 PHY U9. The USB2.0 PHY is connected per ULPI interface (MIO pins 52..63) to MPSoC's MIO bank 501.

The USB3.0 Hub controller has also an ARM Cortex-M0 controller integrated, refer to the data sheet for further features and programmable options.

CAN FD Transceiver

On-board CAN FD (Flexible Data Rate) transceiver is provided by Texas Instruments TCAN337. This controller is the physical layer of the CAN interface and is specified for data rates up to 1 Mbps. The controller has many protection features included to ensure CAN network robustness and to eliminate the need for additional protection circuits. Refer to the data sheet of this transceiver for more details and specifications.

The transceiver is connected to System Controller CPLD U17, means it works on this interface with 3.3V VCCIO. The logical signal processing of the CAN interface depends on the current firmware ot the SC CPLD U17.

eMMC Memory

The TEBF0808 carrier board is equipped with embedded MMC memory connected to the PS MIO bank (MIO13 ... MIO23) of the Zynq Ultrascale+ MPSoC. The memory is provided by MTFC4GACAJCN-4M from Micron Technology. It has a memory density of 32 Gbit (4 GByte) and is sectored into 8 banks a 4 Gbit.

24-bit Audio Codec

For high resolution digital audio signal processing, the TEBF0808 carrier board is equipped with the Analog Devices 24-bit Audio Codec chip ADAU1761 with the schematic designator U3. The Audio Codec chip is connected to the Intel High Defintion Audio (Intel HDA) compatible 9-pin header J9 with single-ended signaling for analog stereo audio signal input and output. It supports also MIC / Jack detect. Its I²C control interface is accessible by the Zynq Ultrascale+ MPSoC through I²C switch U27.

The 24-bit Audio Codec provides numerous features and is also fully programmable with its dedicated graphical tool from the manufacturer. Refer to the data sheet of this chip for more detail information and specifications.

SDIO Port Expander

Due to the different signaling voltage levels of the MicroSD and MMC Card interfaces (3.3V) and the PS MIO bank of the Zynq Ultrascale+ MPSoC (1.8V), there is voltage-translation necessary, which is fullfilled by the SDIO port expander Texas Instruments TXS02612, U15. This IC also muxes the MikroSD and the MMC Card sockets to the SDIO port of the MPSoC, which is controlled by the signal 'SEL_SD' of the System Controller CPLD U39. The SC CPLD U39 also controls the load switches to enable the card sockets J16 and J27 and to report the card detect signal both of the sockets to the MPSoC (see schematic)A Microchip 24AA025E48 serial EEPROM (U23) contains a globally unique 48-bit node address, which is compatible with EUI-48(TM) specification. The device is organized as two blocks of 128 x 8-bit memory. One of the blocks stores the 48-bit node address and is write protected, the other block is available for application use. It is accessible over I2C bus with slave device address 0x53.

DIP-swithches

There are two 4 bit DIP Switches on the TEBF0808, they must be used to select some options. On TEBF0808-02 default CPLD-Firmware selects boot from SD-Card, Firmware update is needed for Boot-Mode selection.

| 1 | 2 | 3 | 4 | Description |

|---|---|---|---|---|

| OFF | OFF | OFF | ON | Default |

| ON | x | x | x | PUDC = 0 |

| OFF | x | x | x | PUDC = High |

DIP Switch S5 located close to PWR push-button. This DIP Switch is connected to the two baseboard control CPLD's.

| 1 | 2 | 3 | 4 | Description |

|---|---|---|---|---|

| ON | ON | ON | ON | Default, boot from SD/eMMC, 1.8V FMC VADJ |

| ON | ON | x | x | Boot from microSD, SD or SPI Flash |

| OFF | ON | x | x | Boot from eMMC |

| ON | OFF | x | x | Boot mode PJTAG0 |

| OFF | OFF | x | x | Boot mode main JTAG |

| x | x | x | ON | FMC VADJ = 1.8V |

| x | x | x | OFF | FMC VADJ = 1.2V |

On-board LEDs

LED | Color | Connected to | Description and Notes |

|---|---|---|---|

| D1 | red | DONE signal (PS Configuration Bank 503) | This LED goes ON when power has been applied to the module and stays ON until MPSoC's programmable logic is configured properly. |

Table 14: LED's description

| LED | Position | Description |

|---|---|---|

| D4 | Green LED near DisplayPort Connector | |

| D5 | Red LED near DisplayPort Connector | |

| D6 | Green LED near Reset Button | |

| D7 | Red LED near Reset Button |

Power and Power-On Sequence

...

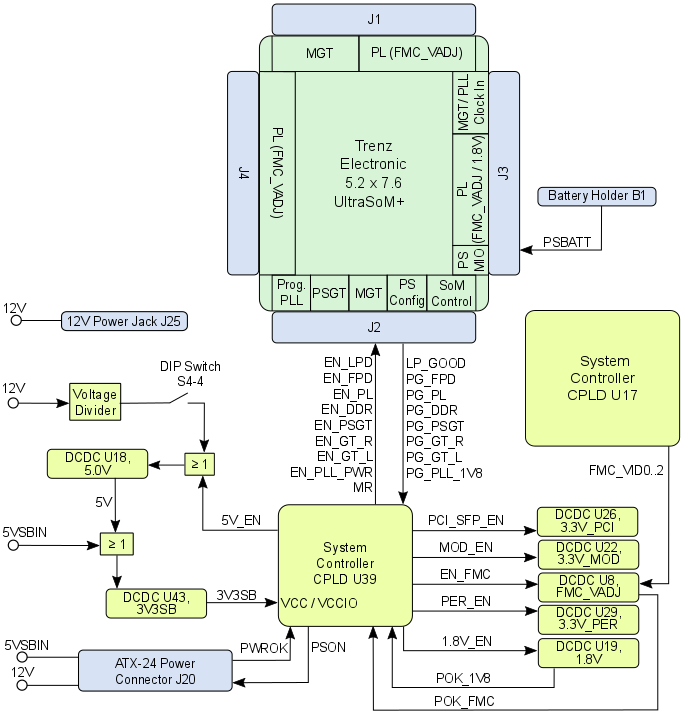

The power-on sequence of the TE0808 SoM is managed by utilizing the SoM's DC-DC converter control signals ('Enable', 'Power-Good'), so the DC-DC converters of the SoM dedicated to the particular Power Domains of the Zynq Ultrascale+ MPSoC will be powerer-up in a specific sequence to meet the recommended criteria to power up the Xilinx Zynq Ultrascale+ MPSoC properly.

Figure 1012: TEBF0808 Power-Management

...

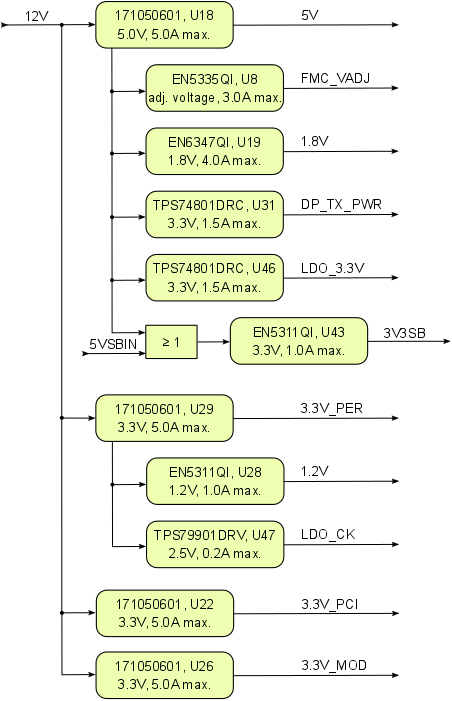

There are following dependencies how the initial 12V power supply is distributed to the on-board DC-DC converters, which power up further DCDC converters and the particular on-board voltages:

Figure 1113: Power Distribution Diagram

...

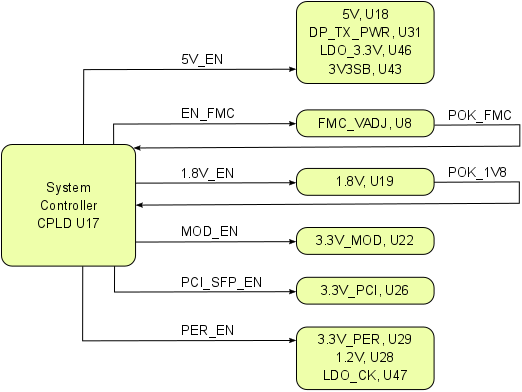

Following diagram visualizes the connection of the DC-DC converter control signals ('Enable', 'Power-Good') with System Controller CPLD U17, which enables the particular on-board voltages.

Figure 1214: Power-On Sequence Utilizing DCDC Converter Control Signals

...