Page History

...

| Info |

|---|

2 Firmware variants with swapped external reset input and output are available. See Watchdog section on of this document. |

| Warning |

|---|

Watchdog do not work correctly on all modules with Firmware released before 2017.08.22. Please update Firmware on CPLD. For questions, write to Trenz Electronic support. |

...

| Pin | FPGA IO |

|---|---|

| BOOT1 (BMODE1) | MIO4 |

| BOOT2 (BMODE2) | MIO5 |

| BOOT1 | BOOT2 | Boot Mode |

|---|---|---|

| 0 | 0 | JTAG |

| 0 | 1 | QSPI |

| 1 | 0 | not supported |

| 1 | 1 | SD |

Watchdog

Watchdog (TPS3310K33DMVR) is controlled by B2B IO, CPLD, Zynq IO or 1V power supply voltage.

TPS3310K33DMVR WDI Timing Requirenments:

| Time-out period | tT(OUT) | at WDI | min 0,55s, typ 1,1s, max 1,65s |

| Pulse width | tw | at WDI | 300ns |

Firmware Variants:

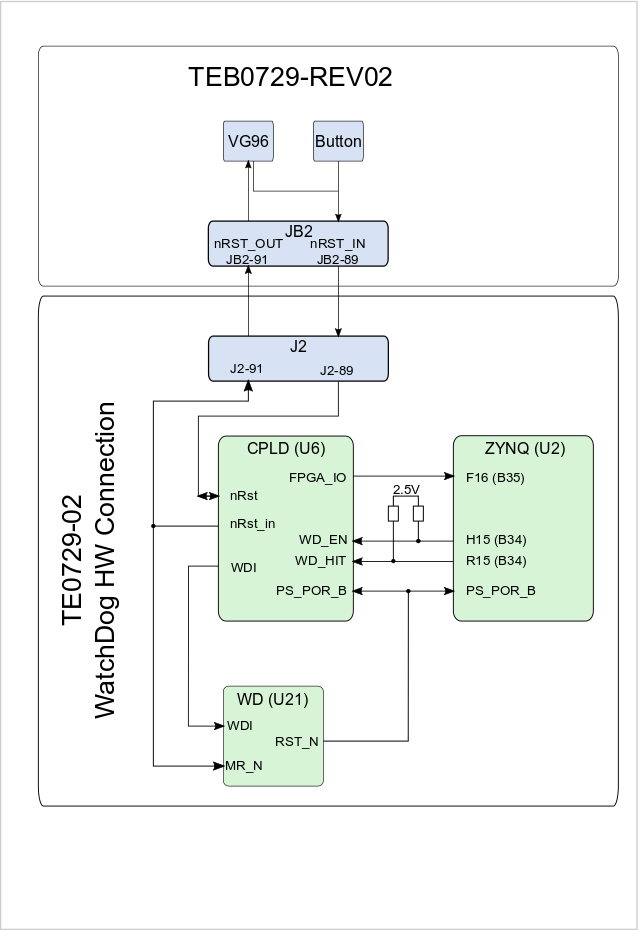

Figure1: Firmware for TEB0729 without modification,

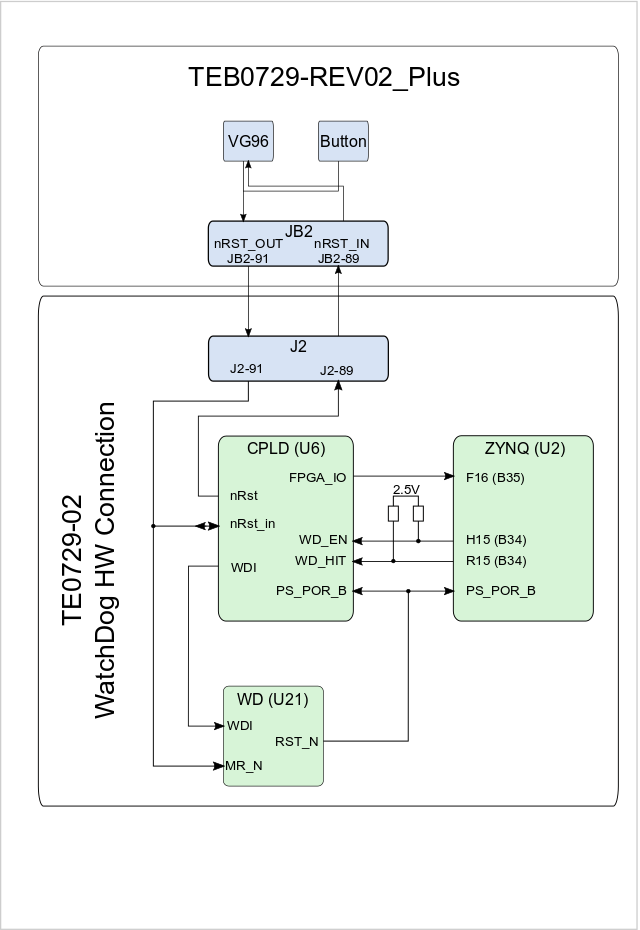

| Figure2: Firmware for TEB0729 with modification,

|

B2B Control:

2 Variant available,depends on carrier board connection, see Figure 1 and 2. The swapped signals and Variant 1 and nRST_IN pulse limitation on variant 1 are the only different difference between this tow two variants.

Variant 1(Figure 1):

| IOs | Direction | Description |

|---|---|---|

| nRST | in | Main Reset to module |

| nRST_IN | out | Main reset to carrier and PS_POR_B for approx. 1,9 us. |

Variant 2 (Figure 2):

| IOs | Direction | Description |

|---|---|---|

| nRST | out | Main reset to carrier and PS_POR_B |

| nRST_IN | in | Main Reset to module |

1V Power supply:

Reset PS, if 1V drop down. Connected on PCB, controlled by WD SENSE pin.

CPLD Control:

CPLD controlled WD on power up until FPGA takes control via WE_EN and WD_HIT input. CPLD WDI pulse frequency is set to approx. 1ms (Pulse width tw(CPLD)=507us )

FPGA Control:

WD_HIT pulse will be forwarded to WDI pin, if WE_EN is high and min 16 WD_HIT from FPGA was detected. To disable FPGA Control, set WD_EN to low.

WDI max. pulse width: tw(FPGA)<tT(out)- tw(CPLD)FPGA Control:

Status / GPIO

BOARD_STAT is used as WD restart indicator and as user IO.

| Modus | Condition |

|---|---|

| Slow Blink | If PS_POR_B is low and appr. 30s long after PS_POR_B goes up |

| User defined | appr. 30s long after PS_POR_B goes up and as long as PS_POR_B is high |

Info: On TEB0729, signal is connected to XMOD LED.

...