Page History

...

The TEC0330 features HPC (High Pin Count) ANSI/VITA 57.1 compatible FMC interface connector for standard I/O Mezzanine modules. Other interface connectors found on-board include JTAG for accessing FPGA and on-board System Controller CPLD, and also connector with 5 high-speed I/O differential signaling pairs available.

The TEC0330 FPGA board is intended to be used as add-on card in a PCIe 2.0 or higher capable host systemsystems, it can not be used as a stand-alone device.

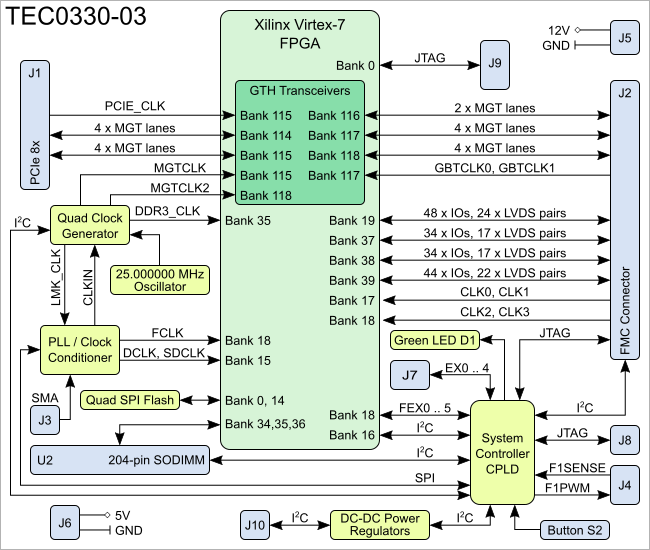

Block Diagram

...

...

Main Components

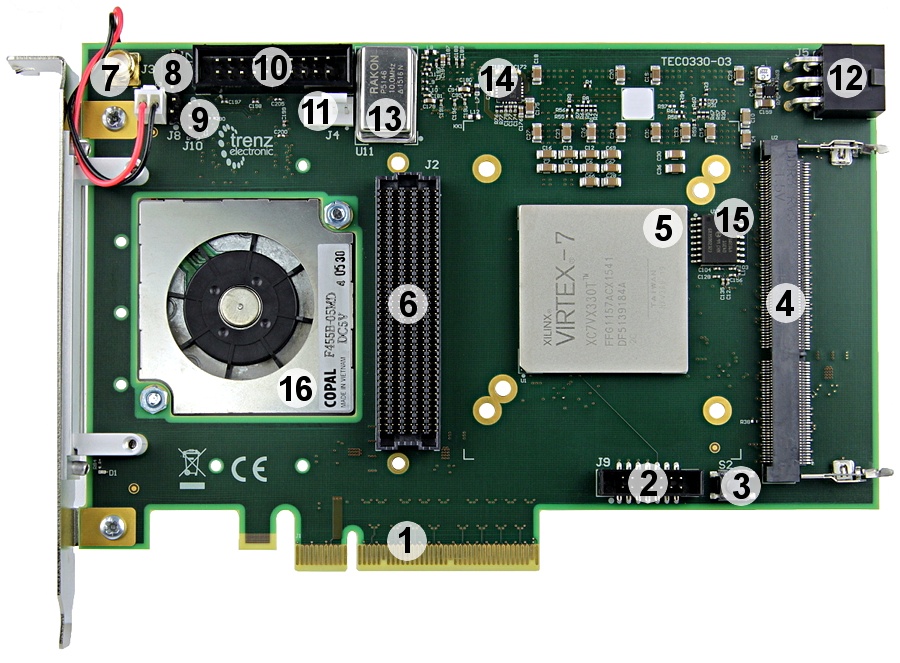

Figure 2: FPGA board TEC0330-03.

- PCIe x8 connector, J1

- FPGA JTAG connector, J9

- User button, S2

- SO-DIMM socket, U2

- Xilinx Virtex-7 XC7VX330T-2FFG1157C FPGA, U1

- ANSI/VITA 57.1 compliant FMC HPC connector, J2

- SMA coaxial connector for external clock input, J3

- System Controller CPLD JTAG connector, J8

- I2C connector for LT LTM4676 step-down DC-DC regulator, J10

- IDC header for access to 5 x high-speed data lanes (LVDS pairs), J7

- 4-wire PWM fan connector, J4

- 6-pin 12V power connector, J5

- Reference clock generator @10.0 MHz (P5146) , U11

- LDO DC-DC regulator @3.3V (LMK_3V3) (TI TPS74901RGWR), U21

- 256 Mbit Quad SPI Flash Memory (Micron N25Q256A), U12

- Cooling fan 5VDC M1 (45X5MM, 0.7W, 1.06CFM)

- System Controller CPLD (Lattice Semiconductor LCMXO2-1200HC), U5

- Ultra low jitter clock synthesizer (TI LMK04828B), U9

- Step-down DC-DC regulator @1.0V (LT LTM4676), U4

- Step-down DC-DC regulator @1.5V (VCC1V5) (LT LTM4676, U3

- I2C Programmable quad clock generator (Silicon Labs Si5338A), U13

- 4A PowerSoC DC-DC converter @1.8V (Altera EN6347QI, U20

- LDO DC-DC regulator @1.0V (MGTAVCC_FPGA) (TI TPS74401RGW), U18

- LDO DC-DC regulator @1.2V (MGTAVTT_FPGA) (TI TPS74401RGW), U17

- 4A PowerSoC DC-DC converter @3.3V (3V3FMC) (Altera EN6347QI), U15

- 4A PowerSoC DC-DC converter @1.8V (FMC_VADJ) (Altera EN6347QI), U7

Key Features

- Xilinx Virtex-7 FPGA module XC7VX330T-2FFG1157C (commercial temperature range)

- FPGA board designed as PCIe card is fitting in PCI Express x8 slots (PCIe 2.0 or higher)

- FMC High Pin Count (HPC) Connector

- 8 MGT lanes available on PCIe interface

- DDR3 SO-DIMM Socket

- 256-Mbit (32-MByte) Quad SPI Flash memory (for configuration and operation) accessible through:

- FPGA

- JTAG port (SPI indirect (Bus width x4))

- External Clock Input via SMA coaxial connector

- 28 GTH transceivers, each with up to 13.1 Gbit/s data transmission rate

- FPGA configuration through:

- JTAG connector

- SPI Flash memory

- Programmable quad PLL clock generator

- TI LMK04828B ultra low-noise high-performance clock synthesizer (jitter cleaner)

- On-board high-efficiency DC-DC converters

- Up to 202 FPGA I/O pins available on FMC connector (up to 101 LVDS pairs possible)

- System management and power sequencing

- AES bit-stream encryption

- eFUSE bit-stream encryption

...

Key Features

- Xilinx Virtex-7 FPGA module XC7VX330T-2FFG1157C (commercial temperature range)

- PCI Express 2.0 x8 card with maximum throughput of 4 GB/s

- FMC High Pin Count (HPC) connector

- 8 FPGA MGT lanes available on PCIe interface

- DDR3 SO-DIMM SDRAM socket

- 256-Mbit (32-MByte) Quad SPI Flash memory (for configuration and operation) accessible through:

- FPGA

- JTAG port (SPI indirect, bus width x4)

- External clock input via SMA coaxial connector

- 28 GTH transceivers, each with up to 13.1 Gbit/s data transmission rate

- FPGA configuration through:

- JTAG connector

- SPI Flash memory

- Programmable quad PLL clock generator

- TI LMK04828B ultra low-noise JESD204B compliant clock jitter cleaner

- On-board high-efficiency DC-DC converters

- Up to 202 FPGA I/O pins available on FMC connector (up to 101 LVDS pairs possible)

- System management and power sequencing

- AES bit-stream encryption

- eFUSE bit-stream encryption

Additional assembly options are available for cost or performance optimization upon request.

Block Diagram

Figure 1: TEC0330-03 Block Diagram.

Main Components

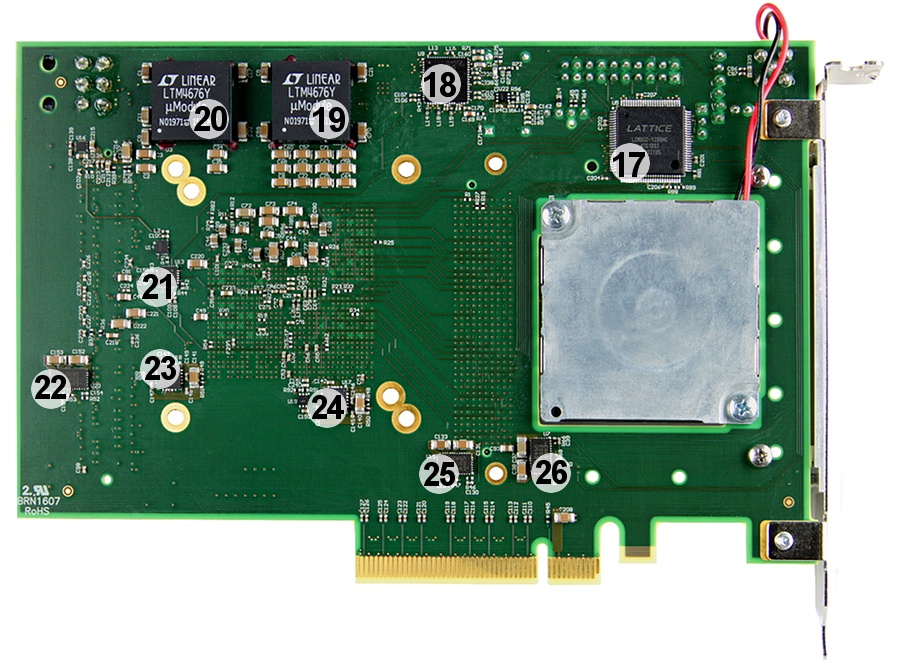

Figure 2: FPGA board TEC0330-03.

- PCI Express 2.0 x8 connector, J1

- FPGA JTAG connector, J9

- User button, S2

- SO-DIMM socket, U2

- Xilinx Virtex-7 XC7VX330T-2FFG1157C FPGA, U1

- ANSI/VITA 57.1 compliant FMC HPC connector, J2

- SMA coaxial connector for external clock input, J3

- System Controller CPLD JTAG connector, J8

- I2C connector for LT LTM4676 step-down DC-DC regulator, J10

- IDC header for access to 5 x high-speed data lanes (LVDS pairs), J7

- 4-wire PWM fan connector, J4

- 6-pin 12V power connector, J5

- Reference clock generator @10.0 MHz (P5146) , U11

- LDO DC-DC regulator @3.3V (LMK_3V3) (TI TPS74901RGWR), U21

- 256 Mbit Quad SPI Flash Memory (Micron N25Q256A), U12

- Cooling fan 5VDC M1 (45X5MM, 0.7W, 1.06CFM)

- System Controller CPLD (Lattice Semiconductor LCMXO2-1200HC), U5

- Ultra low jitter clock synthesizer (TI LMK04828B), U9

- Step-down DC-DC regulator @1.0V (LT LTM4676), U4

- Step-down DC-DC regulator @1.5V (VCC1V5) (LT LTM4676, U3

- I2C Programmable quad clock generator (Silicon Labs Si5338A), U13

- 4A PowerSoC DC-DC converter @1.8V (Altera EN6347QI, U20

- LDO DC-DC regulator @1.0V (MGTAVCC_FPGA) (TI TPS74401RGW), U18

- LDO DC-DC regulator @1.2V (MGTAVTT_FPGA) (TI TPS74401RGW), U17

- 4A PowerSoC DC-DC converter @3.3V (3V3FMC) (Altera EN6347QI), U15

- 4A PowerSoC DC-DC converter @1.8V (FMC_VADJ) (Altera EN6347QI), U7

Initial Delivery State

| Storage device name | Content | Notes |

|---|---|---|

SPI Flash OTP Area | Empty, not programmed | Except serial number programmed by flash vendor. |

SPI Flash Quad Enable bit | Programmed | - |

SPI Flash main array | Demo design | - |

eFUSE USER | Not programmed | - |

eFUSE Security | Not programmed | - |

...

The high-pin count (HPC) FMC (FPGA Mezzanine Card) connector (J2) is a standard ANSI/VITA 57.1 modular interface to the FPGA and provides access to numerous FPGA I/O pins for use by other mezzanine modules and expansion cards. The FMC connector supports single ended I/O (with several VCCIO voltages available) and LVDS I/O signaling.

The I/O signals are routed from the FPGA I/O banks to the FMC connector as LVDS pairs:

| Bank | I/O |

|---|

| Signals | LVDS pairs |

|---|

| VCCO |

|---|

| Bank Voltage | Notes | |||

|---|---|---|---|---|

| Bank 19 | 92 | 46 | 1.8V | - |

| Bank 39 | 42 | 21 | VIO_B_FMC | Bank voltage VIO_B_FMC must be supplied by FMC connector pins J2-J39, J2-K40 Bank's |

VREF_B_M2C |

signal is routed to the FMC connector pin J2-K1 (external reference voltage) | ||||

| Bank 37 | 34 | 17 | 1.8V | Bank's |

| VREF_A_M2C |

| signal is routed to the FMC connector pin J2-H1 (external reference voltage) | ||||

| Bank 38 | 34 | 17 | 1.8V | Bank's VREF |

| _A_M2C |

| signal is routed to the FMC connector pin J2-H1 (external reference voltage) |

Table 2: FMC connector pin-outs of available logic banks Overview of the FPGA I/O bank signals routed to the FMC.

The FMC connector provides also access to the MGT banks of the FPGA. There are also 10 high-speed data links MGT lanes (Xilinx GTH transceiver) available composed as differential signaling pairs for both directions (RX/TX), means from card to (mezzanine) module and vice versatransceivers) from different FPGA MGT banks routed to the FMC connector.

The MGT banks have also clock input - pins which are exposed to the FMC connector. Following MGT lanes are available on the FMC connector:

| FPGA Bank | I/O |

|---|

| signals | LVDS pairs |

|---|

| MGT lanes |

|---|

| Bank's reference clock (LVDS pair) | ||||

|---|---|---|---|---|

| 116 | 10 | 5 | 2 | 1 clock-signal from clock synthesizer U9 to bank's pins T6/T5 |

| 117 | 20 | 10 | 4 | 2 clock-signals from clock FMC connector GBTCLK0_M2C and GBTCLK1_M2C (pins J2-D4/J2-D5 and J2-B20/J2-B21) to bank's pins M6/M5 and P6/P5 |

| 118 | 20 | 10 | 4 | 1 reference clock from clock synthesizer U9 to bank's pins F6/F5 1 reference clock from programmable quad PLL clock generator U13 to bank's pins H6/H5 |

Table 3: FMC connector pin-outs of available MGT lanes of the FPGAOverview of MGT banks lanes routed to the FMC connector.

The FMC connector provides JTAG and I2C interfaces to the System Controller CPLD:

| Interface | I/O |

|---|

| signals |

|---|

| Schematic name / FMC pin | Connected to | Notes | ||

|---|---|---|---|---|

| JTAG | 5 | FMC_TRST, pin D34 FMC_TCK, pin D29 FMC_TMS, pin D33 FMC_TDI, pin D30 FMC_TDO, pin D31 | SC CPLD, bank 2 | VCCIO: 3V3PCI |

| I2C | 2 | FMC_SCL, pin C30 FMC_SDA, pin C31 | SC CPLD, bank 2 | VCCIO: 3V3PCI I2C-lines 3V3PCI pulled-up |

| Control lines | 3 | FMC_PRSNT_M2C_L, pin H2 FMC_PG_C2M, pin D1 (3V3FMC pull-up) FMC_PG_M2C, pin F1 (3V3FMC pull-up) | SC CPLD, bank 1 | PG |

- Power Good signal C2M |

- carrier to mezzanine module M2C |

- mezzanine module to carrier Internal System Controller CPLD signal assignment: FEX_0_N <= FMC_PG_M2C FMC_PG_C2M <= FMC_PRSNT_M2C_L |

Table 4: FMC connector pin-outs of available interfaces to the System Controller CPLD.

...

FPGA bank 17 and 18 clock inputs from FMC connector:

| Schematic name | FMC connector pins | FPGA bank | FPGA pins |

|---|---|---|---|

| CLK0_P, CLK0_N | H4, H5 | 17 | R28, R29 |

| CLK1_P, CLK1_N | G2, G3 | 17 | P29, P30 |

| CLK2_P, CLK2_N | K4, K5 | 18 | G31, G31 |

| CLK3_P, CLK3_N | J2, J3 | 18 | H29, H30 |

...

| FPGA bank | I/O signal count | LVDS pairs count | MGT - lanes count | Bankbank's reference clock (LVDS - pair) | Notes |

|---|---|---|---|---|---|

| 114 | 16 | 8 | 4 | - | - |

| 115 | 18 | 9 | 4 | 1 reference clock from programmable quad PLL clock generator 1 reference clock from PCIe interface J1 to bank's pins AD6/AD5 | - |

Table 7: MGT lanes available on PCIe interface.

JTAG Interfaces

TEC0330 board JTAG interfaces are accessible on the TEC0330 board to program the accessing the FPGA or the System Controller CPLD:

| JTAG interface | JTAG signals schematic name | JTAG connector pins | Connected to |

|---|---|---|---|

CPLD JTAG VCCIO: 3V3PCI Connector: J8 | CPLD_JTAG_TMS | J8-1 | SC CPLD, bank 0, pin 90 |

| CPLD_JTAG_TDI | J8-2 | SC CPLD, bank 0, pin 94 | |

| CPLD_JTAG_TDO | J8-3 | SC CPLD, bank 0, pin 95 | |

| CPLD_JTAG_TCK | J8-4 | SC CPLD, bank 0, pin 91 | |

FPGA JTAG VCCIO: 1V8 Connector: J9 | FPTA_JTAG_TMS | J9-4 | FPGA, bank 0, pin N9 |

| FPTA_JTAG_TCK | J9-6 | FPGA, bank 0, pin M8 | |

| FPTA_JTAG_TDO | J9-8 | FPGA, bank 0, pin N8 | |

| FPTA_JTAG_TDI | J9-10 | FPGA, bank 0, pin L8 | |

FMC JTAG VCCIO: 3.3VPCI Connector: J2 | FMC_TRST | J2-D34 | SC CPLD, bank 2, pin 36 |

| FMC_TCK | J2-D29 | SC CPLD, bank 2, pin 27 | |

| FMC_TMS | J2-D33 | SC CPLD, bank 2, pin 28 | |

| FMC_TDI | J2-D30 | SC CPLD, bank 2, pin 31 | |

| FMC_TDO | J2-D31 | SC CPLD, bank 2, pin 32 |

Table 8: JTAG Interface on TEC0330 board.

SO-DIMM Socket for DDR3

...

SDRAM

The TEC0330 board can be upgraded with a supports additional DDR3 SO-DIMM (204-pin). For this purpose the board is equipped with a -pin) via 204-pin SO-DIMM socket socked U2. The DDR3 memory interface is routed to the FPGA banks 34, 35 and 36.

The reference clock signal for the DDR3 interface is generated by the quad programmable reference clock U13 and is applied to bank 35.

There is also a I2C - interface between the System Controller CPLD and the DDR3 SDRAM memory interface:

| Interface signals schematic name | System Controller CPLD pin | DDR3 memory interface pin |

|---|---|---|

| DDR3_SDA | Bank 2, pin 48 | Pin 200 (3V3PCI pull-up) |

| DDR3_SCL | Bank 2, pin 49 | Pin 202 (3V3PCI pull-up) |

Table 9: I2C-interface between SC CPLD and DDR3 SDRAM memory.

System Controller CPLD

...

Following table describes the interfaces and functionalities established by of the System Controller CPLD, which weren't discussed are not described elsewhere in this TRM:

| CPLD functionality | Interface | Designated CPLD pins | Connected to | Notes |

|---|

| I2C |

| interface between on-board peripherals and FPGA |

| I2C | FPGA_IIC_SDA, pin 24 FPGA_IIC_SCL, pin 25 FPGA_IIC_OE, pin 19 | FPGA bank 16, pin V29 FPGA bank 16, pin W29 FPGA bank 16, pin W26 | VCCIO: 1V8 |

, all |

with pull-up to 1V8. Following |

devices and connectors are linked to the FPGA_IIC I2C |

interface:

|

Note: FPGA_IIC_OE must kept high for I2C |

operation. For I2C |

slave device addresses refer to the |

component datasheets. | |||

User I/Os External LVDS pairs | 10 I/Os 5 x differential signaling pairs | EX0_P ... EX4_P EX0_N ... EX4_N | IDC header J7 |

Can also be used for single-ended signaling. | |

User I/Os Internal LVDS pairs | 13 I/ |

Os 6 x differential signaling pairs | FEX0_P ... FEX5_P FEX0_N ... FEX5_N FEX_DIR (single-ended I/O) | FPGA bank 18 | VCCIO: 1V8 |

Can also be used for single-ended signaling. FPGA bank 18 has also reference clock input from FMC connector (CLK2, CLK3) and |

clock synthesizer U9 (FCLK). |

Internal signal assignment: FEX_DIR <= FMC_PRSNT_M2C_L |

| FPGA |

| programming control and state | 2 I/ |

| Os | DONE, pin 7 PROGRAM_B, pin 8 | FPGA bank 0, pin V8 FPGA bank 0, pin U8 | VCCIO: 1V8 |

| I2C |

| interface to quad programmable PLL clock generator | I²C | PLL_SCL, pin 14 PLL_SDA, pin 15 | U13, pin 12 U13, pin 19 | VCCIO: 1V8 Only PLL_SDA has 1V8 |

pull-up. | |

| Fan PWM control J4 | 2 I/ |

| Os | F1SENSE, pin 99 F1PWM, pin 98 | J4-3 (active low |

) J4-4 |

Internal signal assignment: FEX_5_P <= F1SENSE FEX_5_N => F1PWM | ||

| Button S2 | 1 I/O | BUTTON, pin 77 |

| Switch S2 |

| Functionality depends on CPLD firmware, activating pin |

| PROGRAM_B |

| (active low |

| ) and |

| LED1 |

| in standard configuration. | |||

| LED1 | 1 I/O | LED1, pin 76 | LED D1 (green) |

Fast blinking, |

when FPGA is not programmed. |

Internal signal assignment: LED1 <= Button S2 or FEX0_P | |

PCIe control line RESET_B | 1 I/O |

| PCIE_RSTB |

| , pin 37 | PCIe connector J1-A11 (33R serial resistor) | Internal signal assignment: FEX_4_N <= PCIE_RSTB |

Control Interface to clock synthesizer U9 (TI LMK04828B) | SPI (3 I/ |

Os), 4 I/ |

Os | CLK_SYNTH_SDIO, pin 75 CLK_SYNTH_SCK, pin 74 CLK_SYNTH_RESET, pin 54 CLK_SYNTH_CS, pin 53 CLK_SYNTH_SYNC, pin 52 LMK_STAT0, pin 62 LMK_STAT1, pin 63 | U9, pin 20 U9, pin 19 U9, pin 5 U9, pin 18 U9, pin 6 U9, pin 31 U9, pin 48 |

Pull up to 3V3PCI. Internal signal assignment: LMK_SCK <= FEX_1_P LMK_SDIO <= FEX_1_N LMK_CS <= FEX_3_P LMK_SYNC <= |

EX_3_N LMK_RESET <= FEX_4_P FEX_2_P => LMK_SDIO (FEX_2_N must be 0) |

LMK_STAT0 |

and |

LMK_STAT1 |

signals |

are not |

used. |

| Control Interface to DC-DC converters U3 and U4 (both LT LTM4676) |

I2C (2 I/Os), 2 I/Os | LTM_SCL, pin 67 LTM_SDA, pin 66 LTM1_ALERT, pin 65 LTM2_ALERT, pin 64 | U4, pin E6 and U3, pin E6 U4, pin D6 and U3, pin D6 U4, pin E5 U3, pin E5 |

3V3 |

pull- |

ups. LTM I2C |

interface is also accessible trough header J10. LTM1 |

_Alert and LTM2 |

_ALERT signals |

are not |

used. | |||

| Power-on sequence and monitoring | 6 I/Os | EN_1V8, pin 58 PG_1V8, pin 59 EN_FMC_VADJ, pin 60 PG_FMC_VADJ, pin 61 EN_3V3, pin 51 PG_3V3, pin 57 | U20, pin 27 U20, pin 28 U7, pin 27 U7, pin 28 U15, pin 27 U15, pin 28 |

Sequence of the supply voltages |

depend on the |

System Controller CPLD firmware. EN_1V8, EN_3V3 and EN_FMC_VADJ will be set simultaneously at start-up. PG |

signals will not be evaluated. |

Table 11: Overview of the System Controller CPLD functionalitiesfunctions.

Clocking

The TEC0330 FPGA board has a sophisticated clock generation and conditioning system to meet the requirements of the Xilinx Virtex-7 GTH units with data transmission rates up to 13.1 Gb/s.

...

Once running, the frequency and other parameters can be changed by programming the device using the I²C-I2C bus connected between the FPGA (master) and clock generator (slave). Logic needs to be generated inside the FPGA - module to utilize I²C-bus correctly.

| Si5338A (U13) input | Signal schematic name | Notes |

|---|---|---|

IN1/IN2 | CLKIN_5338_C_P, CLKIN_5338_C_N | reference Reference clock signal from clock synthesizer U9 (100 nF decoupling capacitors and 100Ω termination resistor) |

IN3 | Reference clock signal from reference clock oscillator input, SiTime SiT8208AI (U14). | 25.0 MHz fixed frequency |

IN4/IN6 | pins put Connected to the GND. | LSB (pin 'IN4') of the default I²C-adress 0x70 is zero |

IN5 | not Not connected | - |

| Si5338A (U13) output | Signal schematic name | Notes |

CLK0 A/B | DDR3_CLK_P, DDR3_CLK_N | DDR3-RAM reference clock signal to FPGA bank 35 |

CLK1 A/B | MGTCLK_5338_C_P, MGTCLK_5338_C_N | reference Reference clock signal to FPGA bank 115 MGT (100 nF decoupling capacitors and 100Ω termination resistor) |

CLK2 A/B | LMK_CLK_P, LMK_CLK_N | input Input clock signal to clock synthesizer U9 (100 nF decoupling capacitors) |

| CLK3 A/B | MGTCLK2_5338_C_P, MGTCLK2_5338_C_N | reference Reference clock signal to FPGA bank 118 MGT (100 nF decoupling capacitors and 100Ω termination resistor) |

...

Logic needs to be generated inside the FPGA module to utilize SPI bus correctly.

| LMK04828B (U9) input | signal schematic name | Note |

|---|---|---|

| Status_LD1, Status_LD2 | LMK_STAT0, LMK_STAT1 | Connected to System Controller CPLD, not implemented in current CPLD firmware |

SPI interface and control lines | see section 'System controller CPLD' | The clock synthesizer can be controlled and programmed by the FPGA module via the SPI interface and control lines, which are by-passed through the System Controller CPLD |

| CLKin0, CLKin0* | CLK_SYNTH_CLKIN0_P, CLK_SYNTH_CLKIN0_N | Input reference clock signal via SMA coaxial connector J3, connected to CLKin0* via serial decoupling capacitor 100nF. CLKin0 to connected to GND via serial decoupling capacitor 100nF. |

| CLKin1, CLKin1* | CLK_SYNTH_CLKIN1_P, CLK_SYNTH_CLKIN1_N | Input reference clock signal from quad PLL clock generator Si5338A (U13) via serial decoupling capacitor 100nF. |

| OSCin, OSCin* | - | Signal from reference clock oscillator RAKON P51446LF, fixed to 10.0 MHz |

| LMK04828B (U9) output | signal schematic name | Note |

| DCLKout0, DCLKout0* | CLK_SYNTH_DCLKOUT0_P, CLK_SYNTH_DCLKOUT0_N | Reference clock signal to FPGA bank 15 pins AD29/AE29 |

| SDCLKout1, SDCLKout1* | CLK_SYNTH_SDCLKOUT1_P, CLK_SYNTH_SDCLKOUT1_N | Reference clock signal to FPGA bank 15 pins AE31/AF31 |

| DCLKout2, DCLKout2* | CLKIN_5338_P, CLKIN_5338_N | Reference clock signal to quad PLL clock generator Si5338A (U13) (100 nF decoupling capacitors and 100Ω termination resistor) |

| DCLKout4, DCLKout4* | CLK_SYNTH_DCLKOUT4_P, CLK_SYNTH_DCLKOUT4_N | Reference clock signal to FPGA bank 115 MGT, pins T6/T5 |

| SDCLKout7, SDCLKout7* | CLK_SYNTH_SDCLKOUT7_P, CLK_SYNTH_SDCLKOUT7_N | Reference clock signal to FPGA bank 118 MGT, pins F6/F5 |

| OSCout0, OSCout0* | CLK_SYNTH_CLKIN2_P, CLK_SYNTH_CLKIN2_N | Reference clock signal to FPGA bank 18, pins J30/J31 (100 nF decoupling capacitors) |

Table 14: Pin description of clock synthesizer TI LMK04828B.

...

| Bank | Schematic Name | Voltage | Range | Note |

|---|---|---|---|---|

| 0 | 1V8 | 1.8V | HP: 1.2V to 1.8V | Config bank (fixed to 1.8V) / JTAG interface |

| 14 | 1V8 | 1.8V | HP: 1.2V to 1.8V | QSPI flash memory interface |

| 15 | 1V8 | 1.8V | HP: 1.2V to 1.8V | Reference clock input |

| 16 | 1V8 | 1.8V | HP: 1.2V to 1.8V | I2C interface of FPGA |

| 17 | 1V8 | 1.8V | HP: 1.2V to 1.8V | Reference clock input |

| 18 | 1V8 | 1.8V | HP: 1.2V to 1.8V | Reference clock input / I/O's to CPLD |

| 34 | VCC1V5 | 1.5V | HP: 1.2V to 1.8V | DDR3 memory interface |

| 35 | VCC1V5 | 1.5V | HP: 1.2V to 1.8V | DDR3 memory interface |

| 36 | VCC1V5 | 1.5V | HP: 1.2V to 1.8V | DDR3 memory interface |

114 115 116 117 118 | MGTAVCC_FPGA MGTVCCAUX_FPGA MGTAVTT_FPGA | 1.0V 1.8V 1.2V | MGT bank supply voltage MGT bank auxiliary supply voltage MGT bank termination circuits voltage | MGT banks with Xilinx GTH transceiver units |

| 19 | 1V8 | 1.8V | HP: 1.2V to 1.8V | Bank's I/O's Os routed to FMC, usable as LVDS pairs |

| 37 | 1V8 | 1.8V | HP: 1.2V to 1.8V | Bank's I/O's Os routed to FMC, usable as LVDS pairs |

| 38 | 1V8 | 1.8V | HP: 1.2V to 1.8V | Bank's I/O's Os routed to FMC, usable as LVDS pairs |

| 39 | VIO_B_FMC | user | HP: 1.2V to 1.8V | Bank's I/O's Os routed to FMC, usable as LVDS pairs |

...

| Connector / Pin | Voltage | Direction | Notes |

|---|---|---|---|

| J4, pin 2 | 12V (filtered) | Output | 4-wire PWM fan connector suppy supply voltage |

| J6, pin 2 | 5V (filtered) | Output | Cooling fan M1 supply voltage |

| J8, pin 6 | 3V3PCI | Output | VCCIO CPLD JTAG |

| J9, pin 2 | 1V8 | Output | VCCIO FPGA JTAG |

| J2, pin C35 / C37 | 12V | Output | VCCIO FMC |

| J2, pin D32 | 3V3PCI | Output | VCCIO FMC |

| J2, pin D36 / D38 / D39 / D40 | 3V3FMC | Output | VCCIO FMC |

| J2, pin H1 | VREF_A_M2C | Input | VREF voltage for bank 37 / 38 |

| J2, pin K1 | VREF_B_M2C | Input | VREF voltage for bank 39 |

| J2, pin J39 / J40 | VIO_B_FMC | Input | PL I/O voltage bank 39 (VCCO) |

| J2, pin H40 / G39 / F40 / E39 | FMC_VADJ | Output | VCCIO FMC (fixed to 1.8V) |

| J1, pin A10 / A11 / B8 | 3V3PCI | Input | PCIe interface supply voltage |

| J5, pin 1 / 2 / 3 | 12V | Input | main Main power supply interfaceconnector |

Table 17: Power rails and corresponding connectors of the FPGA board on accessible connectors.

Technical Specifications

Absolute Maximum Ratings

| Parameter | Min | Max | Units | Notes | Notes |

|---|---|---|---|---|---|

12V power supply voltage | 11.4 | 12.6 | V | 12V ± 5 % | ANSI/VITA 57.1 FPGA Mezzanine Card (FMC) |

| standard | |||||

| PL I/O voltage for HP banks | -0.55 | VCCO_X + 0.55 | V | - | Xilinx datasheet DS183 |

| GTH |

| transceivers | -0.5 | 1.26 | V | - | Xilinx datasheet DS183 |

| Voltage on System Controller CPLD pins | -0.3 | 3.6 | V | - | MachXO2 family datasheet |

| Storage temperature | -55 | +125 | °C | - | MachXO2 family datasheet |

Table 18: Absolute maximum ratings.

Recommended Operating Conditions

| Parameter | Min | Max | Units | Notes | Reference Document |

|---|---|---|---|---|---|

| 12V power supply voltage | 11.4 | 12.6 | V | 12V ± 5 % | ANSI/VITA 57.1 FPGA Mezzanine Card (FMC) |

| standard | |||||

| PL I/O voltage for HP banks | -0.2 | VCCO_X + 0.2 | V | - | Xilinx datasheet DS183 |

| GTH transceivers | (*) | (*) | - | - | Xilinx datasheet DS183 |

| Voltage on System Controller CPLD pins | 3.135 | 3.6 | V | - | MachXO2 family datasheet |

Table 19: Recommended operation conditions.

...

Hardware Revision History

| Date | Revision | Notes | PCN | Documentation |

|---|---|---|---|---|

| - | 03 | First production release | - | - |

| 2015-11-05 | 02 | Prototype | - | - |

| - | 01 | Prototype | - | - |

Table 20: Hardware revision history.

Hardware revision number is printed on the PCB board together with the model number separated by the dash.

Figure 5: TE0330 board revision number.

Document Change History

...