Page History

...

- MPSoC: ZYNQ UltraScale+ ZU7EV 900-pin package

- Memory

- 64bit DDR4, 8 GByte maximum

- Dual SPI boot Flash in parallel, 512 MByte maximum - User I/Os

- 65 x PS MIOs, 48 x PL HD GPIOs, 156 x PL HP GPIOs (3 banks)

- Serial transceivers: 4 x GTR + 16 x GTH

- Transceiver clocks inputs and outputs

- PLL clock generator inputs and outputs - Si5345 - 10 output PLL

- All power supplies on board, single 3.3V power source required

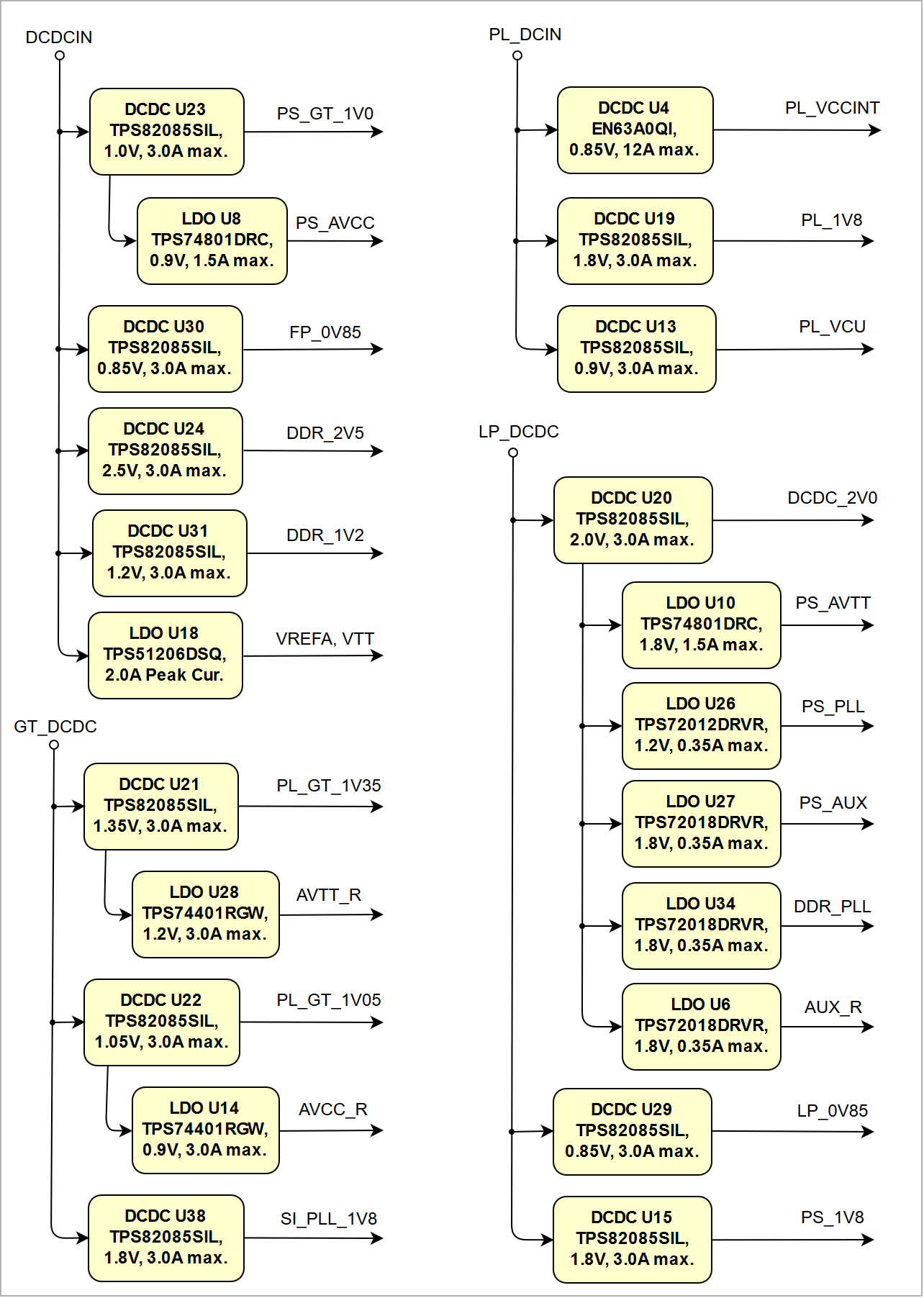

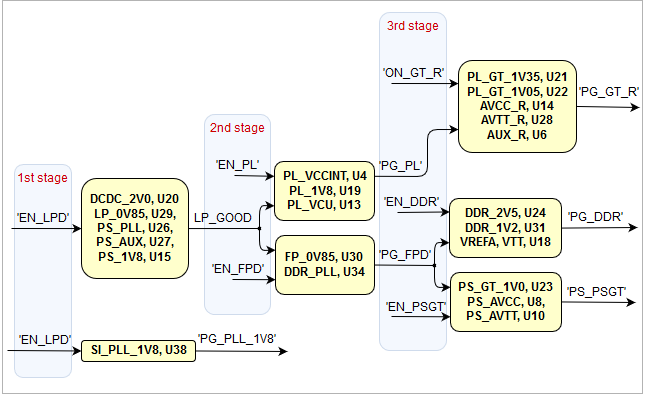

- 14 on-board DC-DC regulators and 13 LDOs

- LP, FPLPD, FPD, PL separately controlled power domains - Support for all boot modes (except NAND) and scenarios

- Support for any combination of PS connected peripherals

- Size: 52 x 76 mm, 3 mm mounting holes for skyline heat spreader

- B2B connectors: 4 x 160 pin

...

| Scroll Title | ||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||

|

Main Components

| Scroll Title | ||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||

|

...

Table 4: B2B connector pin-outs of available PL and PS banks of the TE0807-02 03 SoM.

All MIO banks are powered from on-module DC-DC power rail. All PL I/O Banks have separate VCCO pins in the B2B connectors, valid VCCO should be supplied from the baseboard.

...

| Bank | Type | Lane | Signal Name | B2B Pin | FPGA Pin |

|---|---|---|---|---|---|

| 224 | GTH | 0 |

|

|

|

| 1 |

|

|

| ||

| 2 |

|

|

| ||

| 3 |

|

|

| ||

| 225 | GTH | 0 |

|

|

|

| 1 |

|

|

| ||

| 2 |

|

|

| ||

| 3 |

|

|

| ||

| 226 | GTH | 0 |

|

|

|

| 1 |

|

|

| ||

| 2 |

|

|

| ||

| 3 |

|

|

| ||

| 227 | GTH | 0 |

|

|

|

| 1 |

|

|

| ||

| 2 |

|

|

| ||

| 3 |

|

|

| ||

| 505 | GTR | 0 |

|

|

|

| 1 |

|

|

| ||

| 2 |

|

|

| ||

| 3 |

|

|

|

Table 5: MGT lanes

...

| Clock signal | Bank | Source | FPGA Pin | Notes |

|---|---|---|---|---|

| B224_CLK0_P | 224 | B2B, J3-62 | MGTREFCLK0P_224, R8 | Supplied by the carrier board |

| B224_CLK0_N | 224 | B2B, J3-60 | MGTREFCLK0N_224, R7 | Supplied by the carrier board |

| B224_CLK1_P | 224 | U5, CLK4_P | MGTREFCLK1P_224, N8 | On-board Si5345A |

| B224_CLK1_N | 224 | U5, CLK4_N | MGTREFCLK1N_224, N7 | On-board Si5345A |

| B225_CLK0_P | 225 | B2B, J3-67 | MGTREFCLK0P_225, L8 | Supplied by the carrier board |

| B225_CLK0_N | 225 | B2B, J2J3-65 | MGTREFCLK0N_225, L7 | Supplied by the carrier board |

| B225_CLK1_P | 225 | U5, CLK3_P | MGTREFCLK1P_225, J8 | On-board Si5345A |

| B225_CLK1_N | 225 | U5, CLK3_N | MGTREFCLK1N_225, J7 | On-board Si5345A |

| B226_CLK0_P | 226 | U5, CLK2_P | MGTREFCLK0P_226, H10 | On-board Si5345A |

| B226_CLK0_N | 226 | U5, CLK2_N | MGTREFCLK0N_226, H9 | On-board Si5345A |

| B226_CLK1_P | 226 | B2B, J3-61 | MGTREFCLK1P_226, F10 | Supplied by the carrier board |

| B226_CLK1_N | 226 | B2B, J3-59 | MGTREFCLK1N_226, F9 | Supplied by the carrier board |

| B227_CLK0_P | 227 | U5, CLK1_P | MGTREFCLK0P_227, D10 | On-board Si5345A |

| B227_CLK0_N | 227 | U5, CLK1_N | MGTREFCLK0N_227, D9 | On-board Si5345A |

| B227_CLK1_P | 227 | B2B, J2-22 | MGTREFCLK1P_227, B10 | Supplied by the carrier board |

| B227_CLK1_N | 227 | B2B, J2-24 | MGTREFCLK1N_227, B9 | Supplied by the carrier board |

| B505_CLK0_P | 505 | B2B, J2-10 | PS_MGTREFCLK0P_505, M23 | Supplied by the carrier board |

| B505_CLK0_N | 505 | B2B, J2-12 | PS_MGTREFCLK0N_505, M24 | Supplied by the carrier board |

| B505_CLK1_P | 505 | B2B, J2-16 | PS_MGTREFCLK1P_505, L25 | Supplied by the carrier board |

| B505_CLK1_N | 505 | B2B, J2-18 | PS_MGTREFCLK1N_505, L26 | Supplied by the carrier board |

| B505_CLK2_P | 505 | U5, CLK5_P | PS_MGTREFCLK2P_505, K23 | On-board Si5345A |

| B505_CLK2_N | 505 | U5, CLK5_N | PS_MGTREFCLK2N_505, K24 | On-board Si5345A |

| B505_CLK3_P | 505 | U5, CLK6_P | PS_MGTREFCLK3P_505, H23 | On-board Si5345A |

| B505_CLK3_N | 505 | U5, CLK6_N | PS_MGTREFCLK3N_505, H24 | On-board Si5345A |

...

| PS MIO | Function | Connected to |

|---|---|---|

| 0 | SPI0 | U7-B2, CLK |

| 1 | SPI0 | U7-D2, DO/IO1 |

| 2 | SPI0 | U7-C4, WP/IO2 |

| 3 | SPI0 | U7-D4, HOLD/IO3 |

| 4 | SPI0 | U7-D3, DI/IO0 |

| 5 | SPI0 | U7-C2, CS |

| 6 | N/A | Not connected |

| 7 | SPI1 | U17-C2, CS |

| 8 | SPI1 | U17-D3, DI/IO0 |

| 9 | SPI1 | U17-D2, DO/IO1 |

| 10 | SPI1 | U17-C4, WP/IO2 |

| 11 | SPI1 | U17-D4, HOLD/IO3 |

| 12 | SPI1 | U17-B2, CLK |

| 13 ... 77 | user dependent | B2B connector J2 |

Table 11: TE0807-02 03 PS MIO mapping

On-board Peripherals

...

Table 12: Peripherals connected to the PS MIO pins.

DDR4 SDRAM

The TE0807-02 03 SoM is equipped with with four DDR4 -2400 SDRAM modules chips with a total of up to 8 GByte memory density. The SDRAM modules chips are connected to the Zynq MPSoC's PS DDR controller (bank 504) with a 64bit wide data bus.

...

| Signal | B2B Connector Pin | Function |

|---|---|---|

| PLL_FINC | J2-81 | Frequency increment |

| PLL_LOLN | J2-85 | Loss of lock (active-low) |

| PLL_SEL0 / PLL_SEL1 | J2-93 / J2-87 | Manual input switching |

| PLL_FDEC | J2-94 | Frequency decrement |

| PLL_RST | J2-89 | Device reset (active-low) |

| PLL_SCL / PLL_SDA | J2-90 / J2-92 | I2C interface, external pull-ups needed for SCL / SDA lines I2C address in current configuration: 1101000b1101001b. |

Table 1214: B2B connector pin-out of Si5345A programmable clock generator.

...

| Clock | Signal Schematic Name | Frequency | Connected to Bank 503 Pin |

|---|---|---|---|

| MEMS Oscillator, U32 | PS_CLK | 33.333333 MHz | Bank 503 Pin P20 |

| Quartz crystal, Y2 | XTALI / XTALO | 32.768 kHz | Bank 503 Pin R22/R23 |

| Quartz crystal, Y1 | XAXB_P / XAXB_N | 50.000 MHz | PLL U5, Pin XA/XB |

Table 1315: On-board osciallators

MAC Address EEPROMs

...

LED | Color | Connected to | Description and Notes |

|---|---|---|---|

| D1 | Red | DONE signal (PS Configuration Bank 503) | This LED goes ON when power has been applied to the module and stays ON until MPSoC's programmable logic is configured properly. |

Table 1416: LED's description.

Power and Power-On Sequence

...

| Power Input Pin | Typical Current |

|---|---|

| DCDCIN | TBD* |

| LP_DCDC | TBD* |

| PL_DCIN | TBD* |

| PS_BATT | TBD* |

Table 1517: Maximum current of power supplies. *to be determined soon with reference design setup.

...

| Scroll Title | ||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||

|

...

| Scroll Title | ||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||

|

Operation Conditions of the DC-DC Converter Control Signals

...

| Enable-Signal | B2B Connector Pin | Max. Voltage | Note | Power-Good-Signal | B2B Connector Pin | Pull-up Resistor | Note | |

|---|---|---|---|---|---|---|---|---|

| EN_LPD | J2-108 | 6V | TPS82085SIL data sheet | LP_GOOD | J2-106 | 4K7, pulled up to LP_DCDC | - | |

| EN_FPD | J2-102 | DCDCIN | NC7S08P5X data sheet | PG_FPD | J2-110 | 4K7, pulled up to DCDCIN | - | |

| EN_PL | J2-101 | PL_DCIN | left floating for logic high (drive to GND for logic low) | PG_PL | J2-104 | 4K7, pulled up to PL_DCIN | - | |

| EN_DDR | J2-112 | DCDCIN | NC7S08P5X data sheet | PG_DDR | J2-114 | 4K7, pulled up to DCDCIN | - | |

| EN_PSGT | J2-84 | DCDCIN | NC7S08P5X data sheet | PG_PSGT | J2-82 | External pull-up needed (max. 5.5V), max. sink current 1 mA | TPS74801 data sheet | |

| EN_GT_R | J2-95 | GT_DCDC | NC7S08P5X data sheet | PG_GT_R | J2-91 | External pull-up needed (max. 5.5V), max. sink current 1 mA | TPS74401 data sheet | |

| EN_PLL_PWR | J2-77 | 6V | TPS82085SIL data sheet | PG_PLL_1V8 | J2-80 | External pull-up needed (max. 5.5V), max. sink current 1 mA | TPS82085SIL data sheet |

Table 1618: Recommended operation conditions of DC-DC converter control signals.

...

| Scroll Title | ||||

|---|---|---|---|---|

| ||||

|

Power Rails

|

Power Rails

Power Rail Name | B2B J1 Pins | B2B J2 Pins | B2B J3 Pins | B2B J4 Pins | Directions | Note |

|---|---|---|---|---|---|---|

| PL_DCIN | 151, 153, 155 | |||||

Power Rail Name | B2B J1 Pins | B2B J2 Pins | B2B J3 Pins | B2B J4 Pins | Directions | Note |

| PL_DCIN | 151, 153, 157, 159 | - | - | - | Input | - |

| DCDCIN | - | 154, 156, 158, 160, | - | - | Input | - |

| LP_DCDC | - | 138, 140, 142, 144 | - | - | Input | - |

| PS_BATT | - | 125 | - | - | Input | - |

| GT_DCDC | - | - | 157, 158, 159, 160 | - | Input | - |

| PLL_3V3 | - | - | 152 | - | Input | U5 (programmable PLL) 3.3V nominal input |

| SI_PLL_1V8 | - | - | 151 | - | Output | Internal voltage level 1.8V nominal output |

| PS_1V8 | - | 99 | 147, 148 | - | Output | Internal voltage level |

| PL_1V8 | 91, 121 | - | - | - | Output | Internal voltage level |

| DDR_1V2 | - | 135 | - | - | Output | Internal voltage level |

| VCCO47 | - | - | 43, 44 | - | Input | - |

| VCCO48 | - | - | 15, 16 | - | Input | - |

| VCCO64 | - | - | - | 58, 106 | Input | - |

| VCCO65 | - | - | - | 69, 105 | Input | - |

| VCCO66 | 90, 120 | - | - | - | Input | - |

Table 1619: TE0807-02 03 power rails

Bank Voltages

| Bank | Type | Schematic Name | Voltage | Reference Input Voltage | Voltage Range |

|---|---|---|---|---|---|

| 47 | HD | VCCO47 | user | - | 1.2V to 3.3V |

| 48 | HD | VCCO48 | user | - | 1.2V to 3.3V |

| 64 | HP | VCCO64 | user | VREF_64, pin J4-88 | 1.2V to 1.8V |

| 65 | HP | VCCO65 | user | VREF_65, pin J4-15 | 1.2V to 1.8V |

| 66 | HP | VCCO66 | user | VREF_66, pin J1-108 | 1.2V to 1.8V |

| 500 | MIO | PS_1V8 | 1.8V | - | - |

| 501 | MIO | PS_1V8 | 1.8V | - | - |

| 502 | MIO | PS_1V8 | 1.8V | - | - |

| 503 | CONFIG | PS_1V8 | 1.8V | - | - |

Table 1720: TE0807-02 03 I/O bank voltages

See Xilinx Zynq UltraScale+ datasheet DS925 for the voltage ranges allowed.

...

Parameter | Min | Max | Unit | Notes / Reference Document | |||||

|---|---|---|---|---|---|---|---|---|---|

| PL_DCIN | -0.3 | 74 | V | TPS82085SIL / EN63A0QI data sheet/ Limit is LP_DCDC over EN/PG | |||||

| DCDCIN | -0.3 | 74 | V | TPS82085SIL / TPS51206 data sheet/ Limit is LP_DCDC over EN/PG | |||||

| LP_DCDC | -0.3 | 4 | V | TPS3106K33DBVR data sheet | |||||

| GT_DCDC | -0.3 | 74 | V | TPS82085SIL data sheet/ Limit is LP_DCDC over EN/PG | |||||

| PS_BATT | -0.5 | 2 | V | Xilinx DS925 data sheet | |||||

| PLL_3V3 | -0.5 | 3.8 | V | Si5345/44/42 data sheet | |||||

| VCCO for HD I/O banks | -0.5 | 3.4 | V | Xilinx DS925 data sheet | |||||

| VCCO for HP I/O banks | -0.5 | 2V | Xilinx DS925 data sheet | VREF | -0.5 | 2 | V | Xilinx DS925 data sheet | |

| I/O input voltage for HD I/O banks | -0.55 | VCCO + 0.55 | V | Xilinx DS925 data sheet | |||||

| I/O input voltage for HP I/O banks | -0.55 | VCCO + 0.55 | V | Xilinx DS925 data sheet | |||||

| PS I/O input voltage (MIO pins) | -0.5 | VCCO_PSIO + 0.55 | V | Xilinx DS925 data sheet, VCCO_PSIO 1.8V nominally | |||||

| PS GTR reference clocks absolute input voltage | -0.5 | 1.1 | V | Xilinx document DS925 | |||||

| PS GTR absolute input voltage | -0.5 | 1.1 | V | Xilinx document DS925 | |||||

| MGT clock absolute input voltage | -0.5 | 1.3 | V | Xilinx document DS925 | |||||

MGT Receiver (RXP/RXN) and transmitter | -0.5 | 1.2 | V | Xilinx DS925 data sheet | |||||

Voltage on input pins of | -0.5 | VCC + 0.5 | V | NC7S08P5X data sheet, see schematic for VCC | |||||

Voltage on input pins (nMR) of | -0.3 | VDD + 0.3 | V | TPS3106 data sheet, | |||||

| "Enable"-signals on TPS82085SIL (EN_PLL_PWR, EN_LPD) | -0.3 | 7 | V | TPS82085SIL data sheet | |||||

Storage temperature (ambient) | -40 | 100 | °C | ROHM Semiconductor SML-P11 Series data sheet |

Table 1821: Module absolute maximum ratings

...

| Parameter | Min | Max | Unit | Notes / Reference Document |

|---|---|---|---|---|

| PL_DCIN | 23.53 | 3.6 | V | EN63A0QI / TPS82085SIL data sheet/ Limit is LP_DCDC over EN/PG |

| DCDCIN | 3.13 | 3.6 | V | TPS82085SIL / TPS51206PSQ data sheet/ Limit is LP_DCDC over EN/PG |

| LP_DCDC | 23.53 | 3.6 | V | TPS82085SIL / TPS3106 data sheet |

| GT_DCDC | 23.53 | 3.6 | V | TPS82085SIL data sheet/ Limit is LP_DCDC over EN/PG |

| PS_BATT | 1.2 | 1.5 | V | Xilinx DS925 data sheet |

| PLL_3V3 | 3.143 | 3.47 | V | Si5345/44/42 data sheet 3.3V typical |

| VCCO for HD I/O banks | 1.14 | 3.4 | V | Xilinx DS925 data sheet |

| VCCO for HP I/O banks | 0.95 | 1.9 | V | Xilinx DS925 data sheet |

| I/O input voltage for HD I/O banks. | -0.2 | VCCO + 0.2 | V | Xilinx DS925 data sheet |

| I/O input voltage for HP I/O banks | -0.2 | VCCO + 0.2 | V | Xilinx DS925 data sheet |

| PS I/O input voltage (MIO pins) | -0.2 | VCCO_PSIO + 0.2 | V | Xilinx DS925 data sheet, VCCO_PSIO 1.8V nominally |

| PL bank reference voltage VREF pin | -0.5 | 2 | V | Xilinx DS925 data sheet |

| Voltage on input pins of NC7S08P5X 2-Input AND Gate | 0 | VCC | V | NC7S08P5X data sheet, |

Voltage on input pin 'MR' of | 0 | VDD | V | TPS3106 data sheet, |

Table 1922: Recommended operating conditions

...

Module size: 52 mm × 76 mm. Please download the assembly diagram for exact numbers

Mating height with standard connectors: 4mm5mm

PCB thickness: 1.6mm

Highest part on PCB: approx. 3mm. Please download the step model for exact numbers

...

| Date | Revision | Notes | PCN Link | Documentation Link |

|---|---|---|---|---|

| 2020-06-05 | 03 | current available module revision | PCN-20200511 | TE0807-03 |

| - | 02 | current available module revision | - | TE0807-02 |

| - | 01 | first production release | - | TE0807-01 |

Table 2023: Hardware revision history table

...

| Scroll Title | ||||

|---|---|---|---|---|

| ||||

|

...

|

Document Change History

| HTML |

|---|

< |

| HTML |

<!--

Generate new entry:

1.add new row below first

2.Copy "Page Information Macro(date)" Macro-Preview, Metadata Version number, Author Name and description to the empty row. Important Revision number must be the same as the Wiki document revision number

3.Update Metadata = "Page Information Macro (current-version)" Preview+1 and add Author and change description.

--> |

...

Date | Revision | Contributors | Description | ||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

|

|

| ||||||||||||||||||||||||||

2021-09-07 |

| ||||||||||||||||||||||||||||

| 2021-06-10 | v.27 | John Hartfiel |

| ||||||||||||||||||||||||||

| 2021-05-17 | v.26 | John Hartfiel |

| ||||||||||||||||||||||||||

| 2021-05-03 | v.25 | Martin Rohrmüller |

| ||||||||||||||||||||||||||

2021-03-11 | v.24 | Antti Lukats |

| ||||||||||||||||||||||||||

2019-06-14 | v.22 | John Hartfiel |

| ||||||||||||||||||||||||||

2018-08-07 | v.20 | Ali Naseri |

|

Table 2124: Document change history

Disclaimer

...