Page History

...

...

Table of contents

| Table of Contents | ||

|---|---|---|

|

...

...

There are several options to create the Vivado project from the project delivery. These options are described in Vivado Projects.

...

...

...

...

...

...

...

...

...

Zip Name Description

...

...

...

...

...

...

...

...

...

Currently limitations of functionality

- no current limitations of functionality

Directory structure

...

Command Files

Windows Command Files

...

Settings for the other *.cmd files. Following Settings are avaliable:

- General Settings:

- (optional) DO_NOT_CLOSE_SHELL: Shell do not closed after processing

- (optional) ZIP_PATH: Set Path to installed Zip-Program. Currently 7-Zip is supported. Used for predefined TCL-function to backup project.

- Intel setting:

- QUADIR: Set Intel installation path (Default: c:\intelFPGA_lite).

- QUARTUS_VERSION: Current Quartus Version (Example:18.1). Don't change Quartus Version.

- Intel Software will be searched in:

QUARTUS (optional for project creation and programming): %QUADIR%\%QUARTUS_VERSION%\ quartus\

SDK (optional for software projects and programming): %QUADIR%\%QUARTUS_VERSION%\ nios2eds\

...

Hardware Design

...

Create Project with settings from "design_basic_settings.cmd" and source folders. Build all Quartus hardware and software files if the sources are available.

If old quartus project exists, type "y" into the command line input to delete "<design_name>/quartus/", and "<design_name>/software/" directory with related files before project will created again.

TE-TCL-Extensions

...

Create new Block-Design with initial Setting for PS, for predefined bd_names:

fsys→Fabric Only, msys→Microblaze, zsys→7Series Zynq, zusys→UltraScale+ Zynq

Typ TE::hw_blockdesign_create_bd -help for more information

...

Copies current Hardware files and reports from the vivado project to the prebuilt folder, if -prebuild_hdf <arg> isn't set.

Copy the Hardware Defintition file to the working directory:<design_name>/workspace/hsi

Run HSI in <design_name>/workspace/hsi for all Programes listed in <design_name>/sw_lib/apps_list.csv

If HSI is finished, BIF-GEN and BIN-Gen are running for these Apps in the prepuilt folders <design_name>/prebuilt/...

You can deactivate different steps with following args :

- -no_hsi : *.elf filesgeneration is disabled

- -no_bif : *.bif files generation is disabled

- -no_bin : *.bin files generation is disabled

- -no_bitmcs: *.bit and *.mcs file (with software design) is disabled

...

Copies current Hardware files and reports from the vivado project to the prebuilt folder, if -prebuild_hdf <arg> isn't set.

Copy the Hardware Defintition file to the working directory:<design_name>/workspace/sdk

Start SDK GUI in this workspace

...

Copies current Hardware files and reports from the vivado project to the prebuilt folder, if -used_board <arg> isn't set (Vivado only).

Programming Bitfile from <design_name>/prebuilt/hardware/<board_file_shortname> to the fpga device.

If "-used_basefolder_bitfile" is set, the Bitfile (*.bit) from the base folder (<design_name>) is used instead of the prebuilts. Attention: Take only one Bitfile in the basefolder!

(MicroBlaze only) If "-swapp" is set, the Bitfile with *.elf configuration is used from <design_name>/prebuilt/boot_images/<board_file_shortname>/<app_name>

...

Attention: For Zynq Systems only!

Program the Bootbin from <design_name>/prebuilt/boot_images/<board_file_shortname>/<app_name> to the fpga device.

Appname is selected with: -swapp <app_name>

After programming device reboot from memory will be done.

Default SDK Programmer is used, if not available LabTools Programmer is used.

If "-used_basefolder_binfile" is set, the Binfile (*.bin) from the base folder (<design_name>) is used instead of the prebuilts. Attention: Take only one Binfile in the basefolder!

...

Copies current Hardware files and reports from the vivado project to the prebuilt folder, if -used_board <arg> isn't set (Vivado only).

Initialise flash memory with configuration from *_board_files.csv

Programming MCSfile from <design_name>/prebuilt/hardware/<board_file_shortname> to the Flash Device.

After programming device reboot from memory will be done.

If "-used_basefolder_binfile" is set, the MCSfile (*.mcs) from the base folder (<design_name>) is used instead of the prebuilts. Attention: Take only one MCSfile in the basefolder!

(MicroBlaze only) If "-swapp" is set, the MCSfile with *.elf configuration is used from <design_name>/prebuilt/boot_images/<board_file_shortname>/<app_name>

...

Make a Backup from your Project in <design_name>/backup/

Zip-Program Variable must be set in start_settings.cmd. Currently only 7-Zip is supported.

Design Environment: Usage

Reference-Design: Getting Started

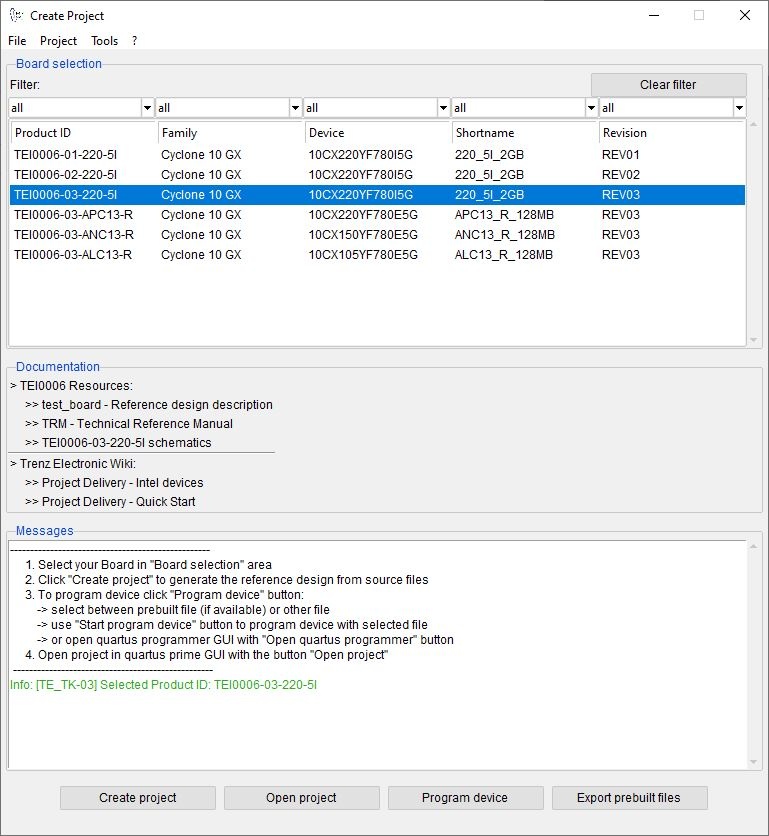

- Install Quartus Prime 18.1 Lite Edition

- Automatically configuration of the reference-designs:

- Run "create_project_win.cmd" and follow instructions.

- "design_basic_settings.cmd" will be configured over this menu

- Run "create_project_win.cmd" and follow instructions.

- Manual Configure the reference-design:

- Open “design_basic_settings.cmd” with a text-editor:

a. Set correct Quartus Environment:

@set QUADIR=C:/intelFPGA_lite

@set QUARTUS_VERSION=18.1

Program settings will be search in :

%QUADIR%/%QUARTUS_VERSION%/quartus/

%QUADIR%/%QUARTUS_VERSION%/nios2eds/

Example directory: c:/intelFPGA_lite/18.1/

Attention: Scripts are supported only with predefined Quartus Version!

- Open “design_basic_settings.cmd” with a text-editor:

- Create and compile project:

- select "c" to create project

- if project already exists, choose between "y" for delete and create project again or "n" to keep project

- after project ist created or project already exists, select "m" to compile project

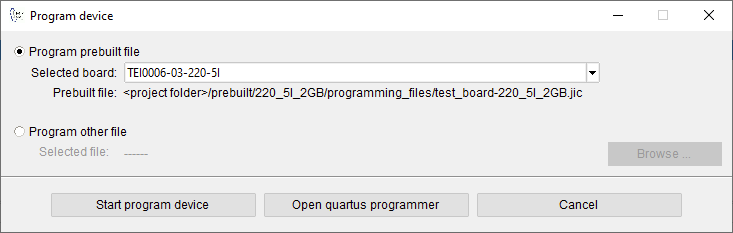

Programming FPGA or flash memory with prebuilt files:

Connect your Hardware-Modul with PC via JTAG.

- Select "p" and press enter

- Quartus Programmer will be open

- Select "Add File..." and open correct file from /prebuilt/<device_list_shortname>/programming_files/

- Start programming FPGA or flash memory

Basic Design Settings

Initialise TE-scripts on Vivado/LabTools

- Variant 1 (recommended):

- Start the project with the predefined command file (vivado_open_existing_project_guimode.cmd) respectively LabTools with (labtools_open_project_guimode.cmd)

- Variant 2:

- Create your own Initialisation Button on the Vivado GUI:

- Tools → Customize Commands → Customize Commands...

- Push

- Type Name ex.: Init Scripts

- Press Enter

- Select Run command and insert:

- for Vivado: cd [get_property DIRECTORY [current_project]]; source -notrace "../scripts/reinitialise_all.tcl"

- for LabTool: cd [pwd]; source -notrace "../scripts/reinitialise_all.tcl"

- Press Enter

- A new Button is shown on the Vivado Gui: All Scripts are reinitialised, if you press this Button.

- Create your own Initialisation Button on the Vivado GUI:

- Variant 3:

- Reinitialise Script on Vivado TCL-Console:

- Type: source ../scripts/reinitialise_all.tcl

- Type: source ../scripts/reinitialise_all.tcl

- Reinitialise Script on Vivado TCL-Console:

Use predefined TE-Script functions

...

- Typ function on Vivado TCL Console, ex.: TE::help

- TE::help

- Show all predefined TE-Script functions.

- TE:<functionname> -help

- Show short description of this function.

- Attention: If -help argument is set, all other args will be ignored.

...

- Variante 1 (no Vivado request window for args):

- insert function and used args, ex.: TE::sw_program_zynq -swapp hello_world

- Variant 2 (Vivado request window for args):

- insert function, ex.:TE::sw_program_zynq

- Press Define Args...

- For every arg:

- Push

- Typ Name, Comment, Default Value and set optional

- Press Enter

- Example for args:

- Push

- Index, Key Name, -swapp,

- Push

- Appname, Arg, hello_world,

- Push

- Push

...

...

...

...

...

SDC Conventions

...

...

User defined device list csv file

To modifiy current deivce list csv list, make a copy of the original csv and rename with suffix "_mod.csv", ex.TEI0001_devices.csv as TEI0001_devices_mod.csv. Scripts used modified csv instead of the original file.

See Chapter Board Part Files for more information.

User defined Settings

Vivado settings:

Vivado Project settings (corresponding TCL-Commands) can be saved as a user defined file "<design_name>/settings/project_settings.tcl". This file will be loaded automatically on project creation.

Script settings:

Additional script settings (only some predefined variables) can be saved as a user defined file "<design_name>/settings/development_settings.tcl". This file will be loaded automatically on script initialisation.

Design settings:

...

ZIP ignore list:

Files which should not be added in the backup file can be can be defined in this file: "<design_name>/settings/zip_ignore_list.tcl". This file will be loaded automaticaly on script initialisation.

SDSOC settings:

SDSOC settings will are deposited on the following folder: "<design_name>/settings/sdsoc"

User defined TCL Script

TCL Files from "<design_name>/settings/usr" will be load automaticaly on script initialisation.

SDSOC-Template

SDSOC description and files to generate SDSoC project are deposited on the following folder: "<design_name>/settings/sdsoc"

HDL-Design

HDL files can be saved in the subfolder "<design_name>/hdl/" as single files or <design_name>/hdl/folder/ and all subfolders or "<design_name>/hdl/<shortname>" and all subfolders of "<design_name>/hdl/<shortname>". They will be loaded automatically on project creation. Available formats are *.vhd, *.v and *.sv. A own top-file must be specified with the name "<design_name>_top.v" or "<design_name>_top.vhd".

To set file attributes, the file name must include "_simonly_" for simulation only and "_synonly_" for synthese only.

RTL-IP-cores (*.xci). can be saved in the subfolder "<design_name>/hdl/xci" or "<design_name>/hdl/xci/<shortname>". They will be loaded automatically on project creation.

Checklist / Troubleshoot

- Are you using exactly the same Vivado version? If not then the scripts will not work, no need to try.

- Ary you using Vivado in Windows PC? Vivado works in Linux also, but the scripts are tested on Windows only.

- Is you PC OS Installation English? Vivado may work on national versions also, but there have been known problems.

- Win OS only: Use short path name, OS allows only 256 characters in normal path.

- Linux OS only: Use bash as shell and add access rights to bash files. Check with "ls ls /bin/sh". It should be desplay: /bin/sh -> bash. Access rights can be changed with "chmod"

- Are space character on the project path? Somtimes TCL-Scripts can't handle this correctly. Remove spaces from project path.

- Did you have the newest reference design build version? Maybe it's only a bug from a older version.

- Check <design_name>/v_log/vivado.log? If no logfile exist, wrong xilinx paths are set in design_basic_settings.cmd

- On project creation process old files will be deleted. Sometimes the access will be denied by os (synchronisiation problem) and the scripts canceled. Please try again.

- If nothing helps, send a mail to Trenz Electronic Support (support[at]trenz-electronic.de) with subject line "[TE-Reference Designs] ", the complete zip-name from your reference design and the last log file (<design_name>/v_log/vivado.log)

References

- Vivado Design Suite User Guide - Getting Started (UG910)

- Vivado Design Suite User Guide - Using the Vivado IDE (UG893)

- Vivado Design Suite User Guide - I/O and Clock Planning (UG899)

- Vivado Design Suite User Guide - Programming and Debugging (UG908)

- Zynq-7000 All Programmable SoC Software Developers Guide (UG821)

- SDSoC Environment User Guide - Getting Started (UG1028)

- SDSoC Environment - User Guide (UG1027)

- SDSoC Environment User Guide - Platforms and Libraries (UG1146)

...

...

...

...

...

Last Vivado 2018.2 supported project delivery version

- no document update was done

...

...

v.134

...

John Hartfiel

...

v.83

...

...

v.1

...

...