...

The Trenz Electronic TE0835 is an industrialextended-grade module based on Xilinx UltraScale+ RFSoC.

...

| Page properties |

|---|

|

Note:

'description: Important components and connector or other Features of the module

→ please sort and indicate assembly options Key Features' must be split into 6 main groups for modules and mainboards: - SoC/FPGA

- Package: SFVC784

- Device: ZU2...ZU5*

- Engine: CG, EG, EV*

- Speed: -1LI, -2LE,*, **

- Temperature: I, E,*, **

- RAM/Storage

- Low Power DDR4 on PS

- Data width: 32bit

- Size: def. 2GB*

- Speed:***

- eMMC

- Data width: 8Bit

- size: def. 8GB *

- QSPI boot Flash in dual parallel mode (size depends on assembly version)

- Data width: 8bit

- size: def. 128MB *

- HyperRAM/Flash (optional, default not assembled)

- MAC address serial EEPROM with EUI-48™ node identity (Microchip 24AA025E48)

- On Board

- Lattice LCMXO2

- PLL SI5338

- Gigabit Ethernet transceiver PHY (Marvell Alaska 88E1512)

- Hi-speed USB2 ULPI transceiver with full OTG support (Microchip USB3320C)

- Interface

- 132 x HP PL I/Os (3 banks)

- ETH

- USB

- 4 GTR (for USB3, Sata, PCIe, DP)

- MIO for UART

- MIO for SD

- MIO for PJTAG

- JTAG

- Ctrl

- Power

- 3.3V-5V Main Input

- 3.3V Controller Input

- Variable Bank IO Power Input

- Dimension

- Notes

- * depends on assembly version

- ** also non low power assembly options possible

- *** depends on used U+ Zynq and DDR4 combination

Key Features' must be split into 6 main groups for carrier: - Modules

- TE0808, TE807, TE0803,...

- RAM/Storage

- On Board

- Interface

- E.g. ETH, USB, B2B, Display port

- Power

- E.g. Input supply voltage

- Dimension

|

- SoC/FPGA

- Xilinx UltraScale+ RFSoC (XCZU25DR-1FFVE1156E)

- Package: E1156

- Speed: -1 (slowest)

- Temperature: Extended (0 to +100 °C)

<Replace for module use "SoC/FPGA" for Carrier "Modules"> - RAM/Storage

- 4x 8Gb DDR4

- 2x 512Mb SPI Flash

- On Board

- Interface

- Power

- Dimension

- Notes

- Lattice iCE40 CPLD

- Programmable Clock Generator

- 3x Oscillators

- Interface

- 2x Samtec ST5 (2x80 pol) Board to Board Connectors

- Power

- Dimension

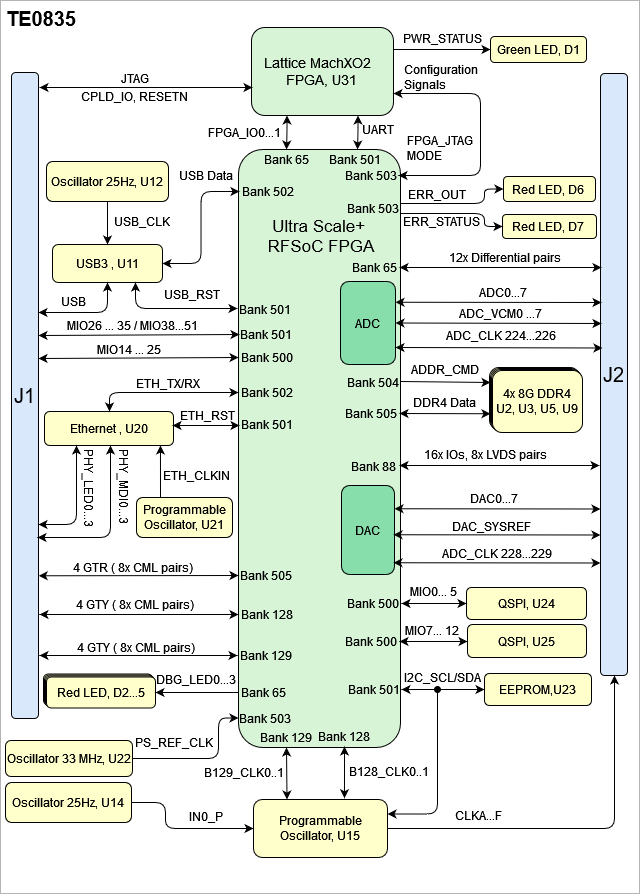

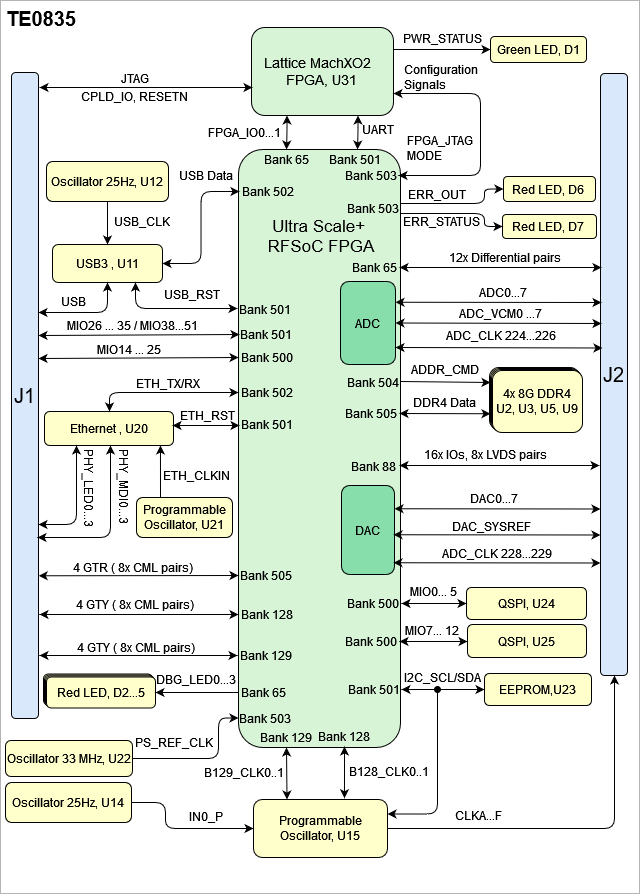

Block Diagram

| Page properties |

|---|

|

add drawIO object here.

|

...

| Scroll Title |

|---|

| anchor | Figure_OV_BD |

|---|

| title | TExxxx block diagram |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | truefalse |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 1 |

|---|

| diagramName | TE0835_OV_BD |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 641 | revision | 1 |

|---|

|

|

| Scroll Only |

|---|

|

|

Main Components

...

| Scroll Title |

|---|

| anchor | Table_OV_IDS |

|---|

| title | Initial delivery state of programmable devices on the module |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

Storage device name | Content | Notes |

|---|

Quad 2x SPI Flash |

|

| | EEPROM | System Controller CPLD |

|

| | 2x DDR4 |

|

| | Programmable Clock Generator |

|

|

|

Configuration Signals

| Page properties |

|---|

|

- Overview of Boot Mode, Reset, Enables.

|

...

| Scroll Title |

|---|

| anchor | Table_OV_BP |

|---|

| title | Boot process. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

MODE Signal State | Boot Mode |

|---|

|

|

|

|

|

| Scroll Title |

|---|

| anchor | Table_OV_RST |

|---|

| title | Reset process. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

|

...

| Scroll Title |

|---|

| anchor | Table_OBP_LED |

|---|

| title | On-board LEDs |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Designator | Color | Connected to | Active Level | Note |

|---|

|

...

DDR4 SDRAM

| Page properties |

|---|

|

Notes : Minimum and Maximum density of DDR3 SDRAM must be mentioned for other assembly options. (pay attention to supported address length for DDR3) |

...

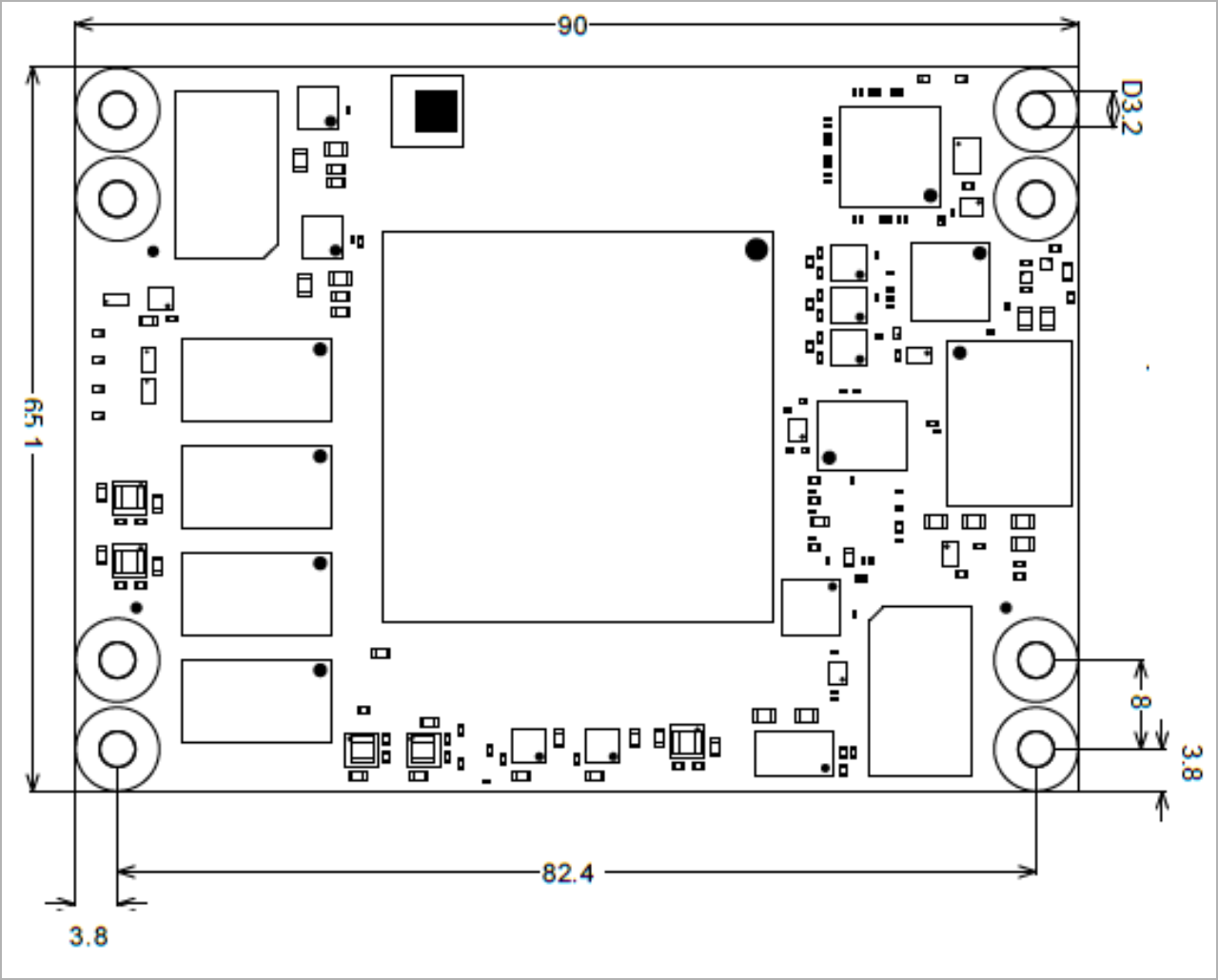

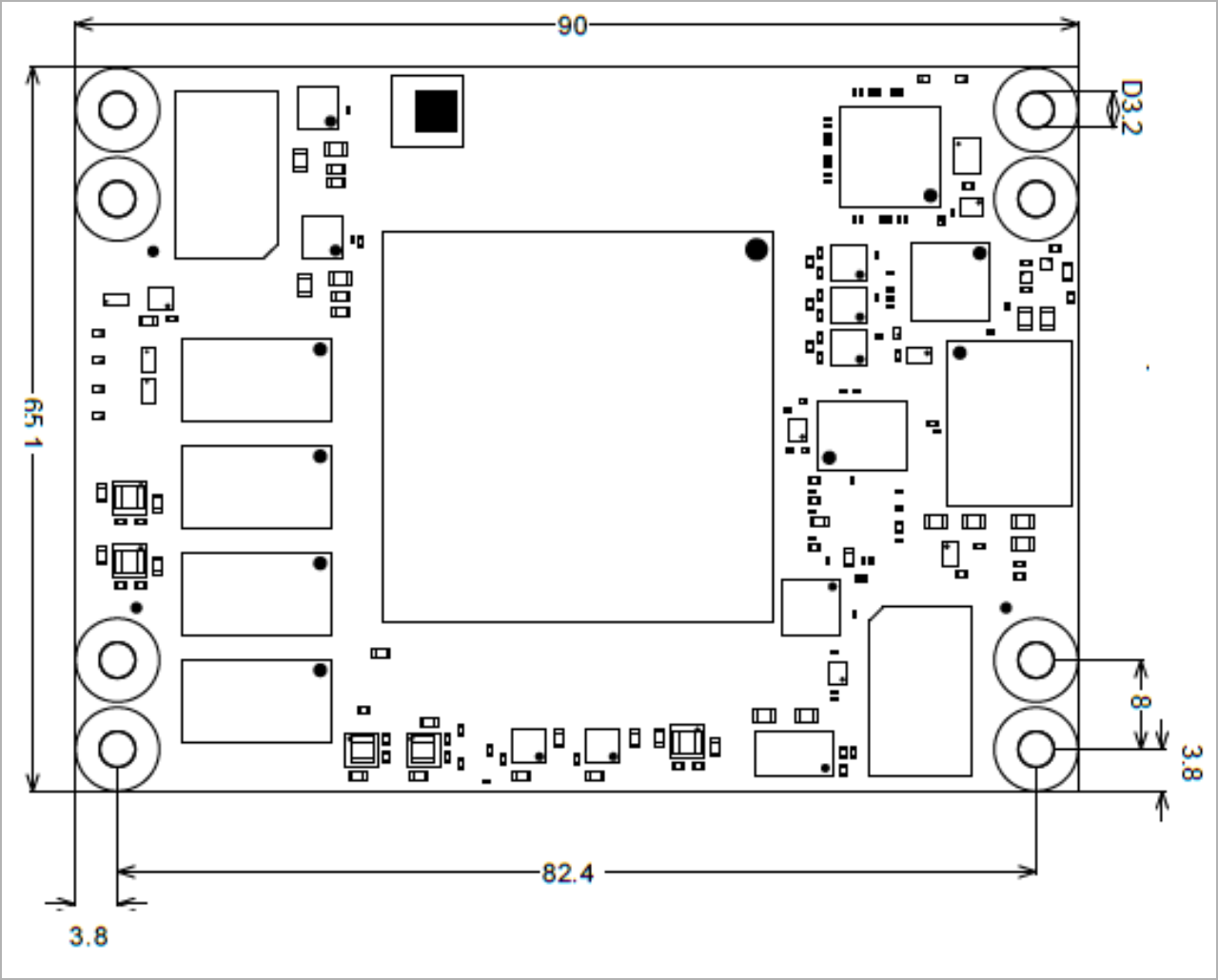

Physical Dimensions

Module size: ?? 90 mm × ?? 65 mm. Please download the assembly diagram for exact numbers.

Mating height with standard connectors: ? 7 mm.

PCB thickness: ?? 1.65 mm.

| Page properties |

|---|

|

In 'Physical Dimension' section, top and bottom view of module must be inserted, information regarding physical dimensions can be obtained through webpage for product in Shop.Trenz, (Download> Documents> Assembly part) for every SoM. For Example: for Module TE0728, Physical Dimension information can be captured by snipping tools from the link below: https://www.trenz-electronic.de/fileadmin/docs/Trenz_Electronic/Modules_and_Module_Carriers/5.2x7.6/TE0745/REV02/Documents/AD-TE0745-02-30-1I.PDF

|

...

| Scroll Title |

|---|

| anchor | Figure_TS_PD |

|---|

| title | Physical Dimension |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | true |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramName | TE0835_TS_PD |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| diagramWidth | 641549 |

|---|

| revision | 12 |

|---|

|

|

| Scroll Only |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

|

|

|

...