...

| Scroll Title |

|---|

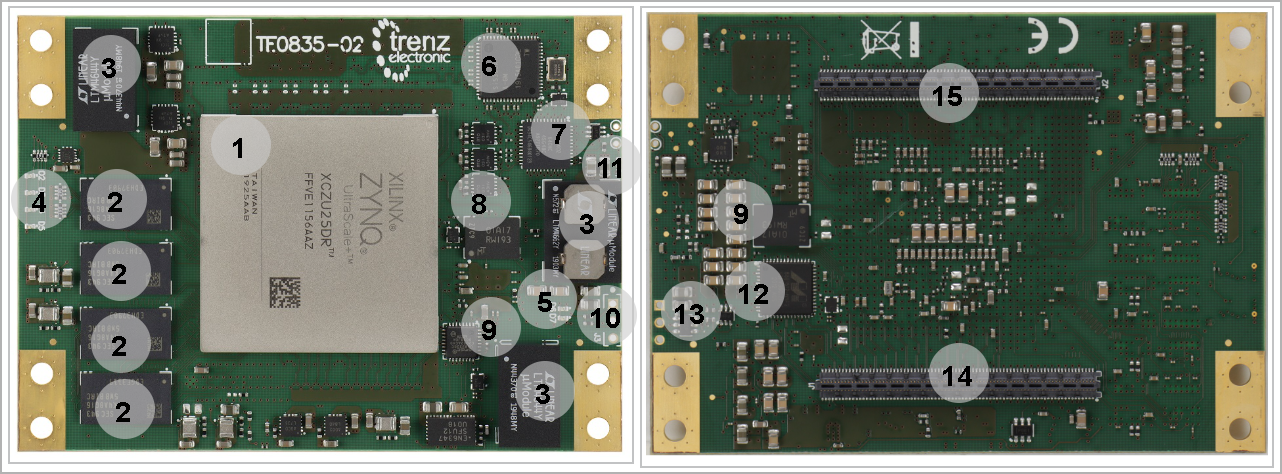

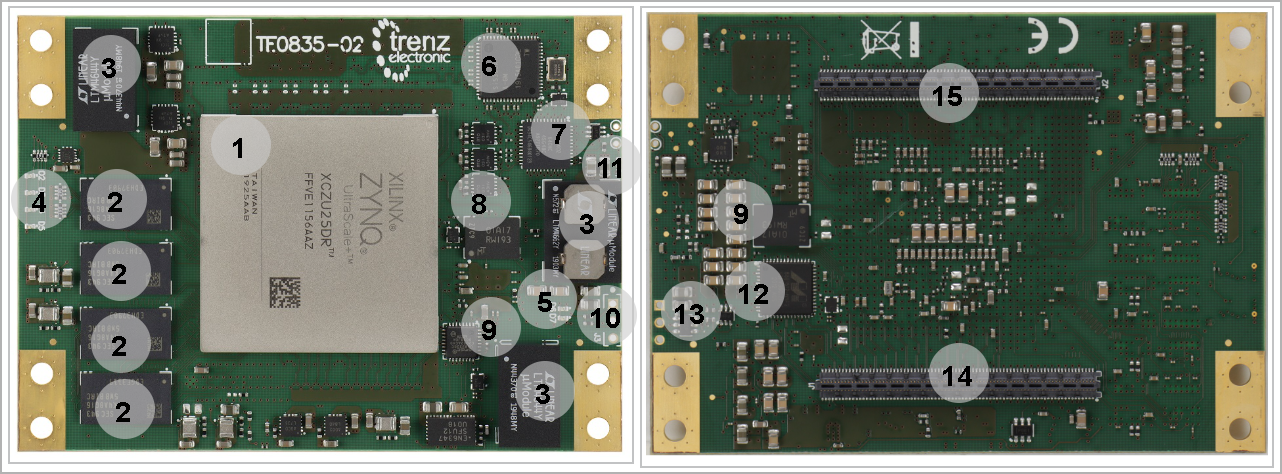

| anchor | Figure_OV_MC |

|---|

| title | TE0835 main components |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 9 |

|---|

| diagramName | TE0835_OV_MC |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 641 |

|---|

|

|

| Scroll Only |

|---|

|

|

- Xilinx UltraScale+ MPSoC XCZU25DRRFSoC XCZU25DR, U1

- 8Gb DDR4 SDRAM, U2,U3,U5,U9

- Voltage Regulators, U4,U6,U7

- Programmable Glock Generator, U15

- Lattice MachXO2 CPLD, U31

- Dual SPI Flash, U24-U25

- USB2.0 Transceiver, U11

- Pin Header 3x1, J3 (not Soldered)

- Gigabit Ethernet Transceiver, U20

- EEPROM, U23

- B2B Connector, J2

- B2B Connector, J1

...

Configuration must be set through CPLD,U31 by setting MODE0...3 signals.

...

| Scroll Title |

|---|

| anchor | Table_SIP_B2B |

|---|

| title | General PL I/O to B2B connectors information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

B2B ConnectorO Signal CountVoltage Level

|

JTAG Interface

JTAG access to the TExxxx SoM through B2B connector JMX.

...