Page History

...

| Page properties | ||||

|---|---|---|---|---|

| ||||

Template Revision 2.6 8 - on construction Design Name always "TE Series Name" + Design name, for example "TE0720 Test Board" |

...

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

| Excerpt |

|---|

|

...

| Scroll Title | |||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||||||||||||

|

...

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

Hardware

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

...

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

...

| Page properties | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Notes :

|

...

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||

|

...

Reference Design is available on:

Design Flow

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

...

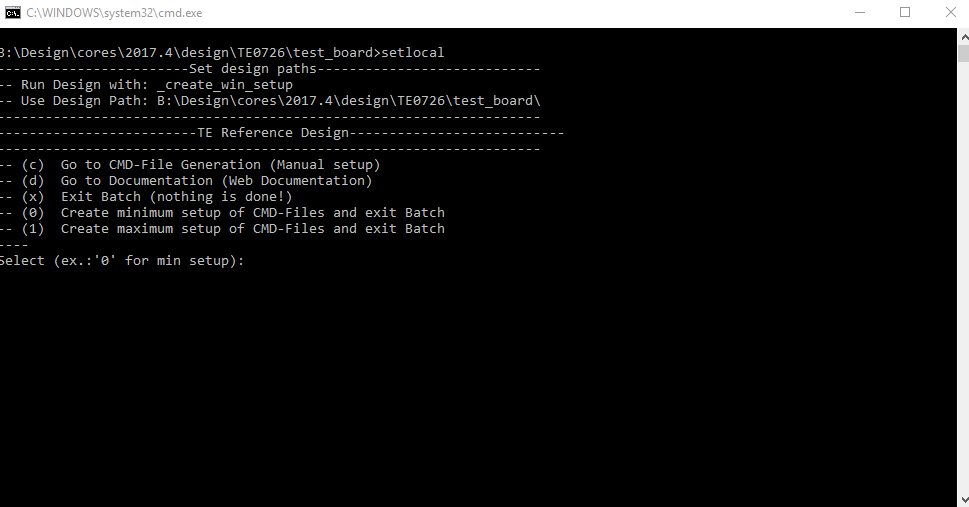

- _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

- Press 0 and enter to start "Module Selection Guide"

- (optional Win OS) Generate Virtual Drive or use short directory for the reference design (for example x:\<design name>)

- Create Project (follow instruction of the product selection guide), settings file will be configured automatically during this process

- (optional for manual changes) Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

Note: Select correct one, see TE Board Part Files

- (optional for manual changes) Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

- Create HDF and export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

- Create Linux (uboot.elf and image.ub) with exported HDFXSA

- HDF XSA is exported to "prebuilt\hardware\<short name>"

Note: HW Export from Vivado GUI create another path as default workspace. - Create Linux images on VM, see PetaLinux KICKstart

- Use TE Template from /os/petalinux

- For 128MB and 64MB only:Netboot Offset must be reduced manually, see 68616202

- HDF XSA is exported to "prebuilt\hardware\<short name>"

- Add Linux files (uboot.elf and image.ub) to prebuilt folder

- "prebuilt\os\petalinux\<DDR size>" or "prebuilt\os\petalinux\<short name>"

Notes: Scripts select "prebuilt\os\petalinux\<short name>", if exist, otherwise "prebuilt\os\petalinux\\<DDR size>"

- "prebuilt\os\petalinux\<DDR size>" or "prebuilt\os\petalinux\<short name>"

- Generate Programming Files with HSI/SDKVitis

- Run on Vivado TCL: TE::sw_run_hsivitis -all

Note: Scripts generate applications and bootable files, which are defined in "sw_lib\apps_list.csv" - (alternative) Start SDK Vitis with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_sdkvitis

Note: See SDK Projects TCL scripts generate also platform project, this must be done manuelly in case GUI is used. See Vitis

- Run on Vivado TCL: TE::sw_run_hsivitis -all

Launch

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

Programming

| Note |

|---|

Check Module and Carrier TRMs for proper HW configuration before you try any design. |

Xilinx documentation for programming and debugging: Vivado/SDK/SDSoC-Xilinx Software Programming

...

Programming

| Note |

|---|

Check Module and Carrier TRMs for proper HW configuration before you try any design. |

...

Get prebuilt boot binaries

- _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell

- Press 0 and enter to start "Module Selection Guide"

- Select assembly version

- Validate selection

- Select Create and open delivery binary folder

Note: Folder (<project foler>/_binaries_<Artikel Name>) with subfolder (boot_<app name>) for different applications will be generated

QSPI

- Connect JTAG and power module (TE0726 can be powered via JTAG USB or external)

- Open Vivado Project with "vivado_open_existing_project_guimode.cmd" or if not created, create with "vivado_create_project_guimode.cmd"

- Type on Vivado TCL Console: TE::pr_program_flash_binfile -swapp u-boot

Note: To program with SDK/Vivado GUI, use special FSBL (zynqmp_fsbl_flash) on setup

optional "TE::pr_program_flash_binfile -swapp hello_te0726" possible - Build Image.ub in Petalinux

- Copy the Petalinux image.ub on SD-Card

- For correct prebuilt file location, see <design_name>/prebuilt/readme_file_location.txt

- Copy init.sh on SD-Card

- Location : <design-name>/misc/sd/

- Insert SD-Card

...

For SDK project creation, follow instructions from:SDK Projects

Application

| Page properties | ||||

|---|---|---|---|---|

| ||||

---------------------------------------------------------- FPGA Example scuMCS Firmware to configure SI5338 and Reset System. srec_spi_bootloaderTE modified 2018.3 SREC Bootloader to load app or second bootloader from flash into DDR Descriptions:

xilisf_v5_11TE modified 2018.3 xilisf_v5_11

---------------------------------------------------------- Zynq Example: zynq_fsblTE modified 2018.3 FSBL General:

Module Specific:

zynq_fsbl_flashTE modified 2018.3 FSBL General:

ZynqMP Example: ---------------------------------------------------------- zynqmp_fsblTE modified 2018.3 FSBL General:

Module Specific:

zynqmp_fsbl_flashTE modified 2018.3 FSBL General:

zynqmp_pmufwXilinx default PMU firmware. ---------------------------------------------------------- General Example: hello_te0820Hello TE0820 is a Xilinx Hello World example as endless loop instead of one console output. u-bootU-Boot.elf is generated with PetaLinux. SDK/HSI is used to generate Boot.bin. |

SDK template in ./sw_lib/sw_apps/ available.

zynq_fsbl

TE modified 20182019.3 2 FSBL

General:

- Modified Files:main.c, fsbl_hooks.h/.c (search for 'TE Mod' on source code)

Add Files: te_fsbl_hooks.h/.c(for hooks and board)\n\

- General Changes:

- Display FSBL Banner and Device ID

...

zynq_fsbl_flash

TE modified 20182019.3 2 FSBL

General:

- Modified Files: main.c

- General Changes:

- Display FSBL Banner

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

...

U-Boot.elf is generated with PetaLinux. SDK/HSI Vitis is used to generate Boot.bin.

...

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

...