...

| Scroll Title |

|---|

| anchor | Figure_Overview |

|---|

| title | Board Overview |

|---|

|

| Scroll Ignore |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

| | draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 4 |

|---|

| diagramName | Overview |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 509 |

|---|

|

|

| Scroll Only |

|---|

|

|

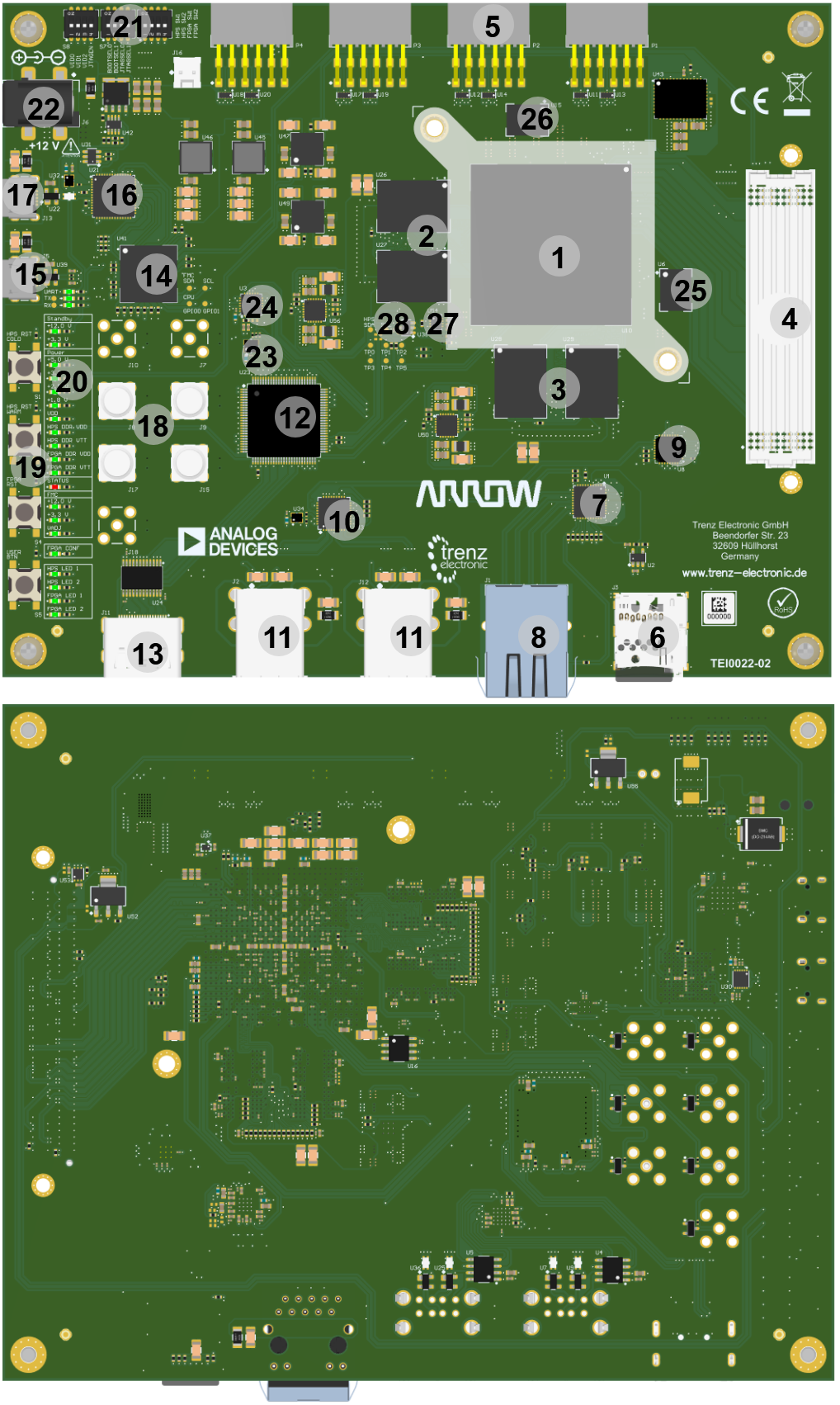

Board Overview

| Number | Note | Number | Note |

|---|

| 1 | U10 - Intel Cyclone V | 15 | J5 - Micro USB for UART |

| 2 | U26...27 - DDR3 for Fabric | 16 | U21 - USB to JTAG FTDI |

3 | U28...29 - DDR3 for HPS | 17 | J13 - Micro USB for JTAG |

| 4 | J4 - FMC | 18 | J7...10 / J15 / J17...18 - SMA Connector |

| 5 | P1...4 - PMOD | 19 | S1, S3...5 - Button |

| 6 | J3 - SD Card | 20 | LEDs |

| 7 | U1 - Ethernet PHY | 21 | S2 / S7...8 - DIP Switch |

| 8 | J1 - Ethernet RJ45 | 22 | J6 - Power Jack |

| 9 | U8 - USB PHY | 23 | U48 - Oscillator |

| 10 | U33 - USB HUB | 24 | U3 - Programmable Clock Generator |

| 11 | J2/ J12 - USB Connector | 25 | U6 - QSPI |

| 12 | U23 - HDMI Transmitter | 26 | U15 - QSPI |

| 13 | J11 - HDMI Connector | 27 | U54 - Power Monitoring |

| 14 | U41 - Intel MAX 10 | 28 | U38 - EEPROM |

Power supply

| Page properties |

|---|

|

The input power supply must be mentioned. |

Single +12.0 V power supply is needed to power on the board at power jack J6. Current depends manly mainly on design and cooling solution. Use Intel Power Estimator and/or your Intel Quartus Prime Project to estimate min current. Minimum of 3A are recommended for basic functionality.

...

| Scroll Title |

|---|

| anchor | Table_DIP_1 |

|---|

| title | DIP Switche S2 |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Overview 21 | Default | Description | Active Level |

|---|

| S2-1 | OFF | HPS User Switch 1 | L | | S2-2 | OFF | HPS User Switch 2 | L | | S2-3 | OFF | FPGA User Switch 1 | L | | S2-4 | OFF | FPGA User Switch 2 | L |

|

| Scroll Title |

|---|

| anchor | Table_DIP_2 |

|---|

| title | DIP Switche S7 (Firmware dependent) |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Overview 21 | Default | Description | Active Level |

|---|

| S7-1 | OFF |

| S7-1 | S7-2 | Boot Selection |

|---|

| 0 | 0 | FPGA | | 1 | 0 | SD/MMC | | 1 | 1 | SPI |

| L | | S7-2 | ON | L | | S7-3 | ON |

| S7-3 | S7-4 | S8-4 | JTAG Selection |

|---|

| X | X | ON | MAX 10 | | ON | ON | OFF | HPS | | ON | OFF | OFF | FPGA | | OFF | ON | OFF | FMC |

| L | | S7-4 | OFF | L |

|

| Scroll Title |

|---|

| anchor | Table_DIP_3 |

|---|

| title | DIP Switche S8 (Firmware dependent) |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Overview 21 | Default | Description | Active Level |

|---|

| S8-1 | OFF |

| S8-3 | S8-2 | S8-1 | Output Voltage |

|---|

| ON | ON | ON | 3.3 V | | ON | ON | OFF | 2.5 V | | ON | OFF | ON | 1.8 V | | ON | OFF | OFF | 1.5 V | | OFF | ON | ON | 1.25 V | | OFF | ON | OFF | 1.2 V | | OFF | OFF | ON | 0.8 V (not supported by Intel Cyclone V) | | OFF | OFF | OFF | Selected by HPS (Firmware dependent) |

| L | | S8-2 | OFF | L | | S8-3 | OFF | L | | S8-4 | OFF |

| S7-3 | S7-4 | S8-4 | JTAG Selection |

|---|

| X | X | ON | MAX 10 | | ON | ON | OFF | HPS | | ON | OFF | OFF | FPGA | | OFF | ON | OFF | FMC |

| H |

|

| Scroll Title |

|---|

| anchor | Table_PB |

|---|

| title | Push Button (Firmware dependent) |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Overview 21 | Default | Description | Active Level |

|---|

| S1 | OFF | Intel Cyclone V HPS Reset | L | | S3 | OFF | Intel Cyclone V HPS Warm Reset | L | | S4 | OFF | Intel Cyclone V FPGA Reset | L | | S5 | OFF | Intel Cyclone V User Button | L |

|

LEDs

| Page properties |

|---|

|

Explain all user LEDs functionality and connections. |

...

| Scroll Title |

|---|

| anchor | Table_LED |

|---|

| title | LEDs (Firmware dependent) |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Designator | Color | Connected to | Active Level | Note |

|---|

| J1C | Yellow | Ethernet PHY | L | Ethernet Status | | D25 | Red | Intel MAX 10 | H | Board Status | | D11 | Green | Intel Cyclone V HPS | H | HPS User LED 2 | | D12 | Green | Intel Cyclone V HPS | H | HOS User LED 1 | | D13 | Green | Intel Cyclone V FPGA | H | FPGA User LED 2 | | D14 | Green | Intel Cyclone V FPGA | H | FPGA User LED 1 | | D8 | Green | Intel MAX 10 and Intel Cyclone V | L | Programming Status | | D15 | Green | UART FTDI | L | UART Status | | D18 | Green | UART TX | L | UART TX Status | | D19 | Green | UART RX | L | UART RX Status | | D21 | Green | +12.0V | H | +12.0 V Status | | D1 | Green | +12.0V_FMC | H | +12.0 V FMC Status | | D2 | Green | +5.0V | H | +5.0 V Status | | D3 | Green | +3.3V | H | +3.3 V Status | | D20 | Green | +3.3V_MAX10 | H | +3.3 V Standby Status | | D22 | Green | +3.3V_FMC | H | +3.3 V FMC Status | | D4 | Green | +2.5V | H | +2.5 V Status | | D5 | Green | Intel MAX 10 | H | +1.8 V Status | | D7 | Green | Intel MAX 10 | H | VCC Status | | D9 | Green | Intel MAX 10 | H | VADJ Status | | D6 | Green | Intel MAX 10 | H | FPGA DDR VDD Status | | D23 | Green | Intel MAX 10 | H | HPS DDR VDD Status | | D17 | Green | Intel MAX 10 | H | HPS DDR VTT Status | | D10 | Green | Intel MAX 10 | H | FPGA DDR VTT Status |

|

JTAG/UART

| Page properties |

|---|

|

Explain JTAG or UART connection breifly. |

...

| Scroll Title |

|---|

| anchor | Table_UART |

|---|

| title | JTAG and UART |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Designator | Connected to | Direction | Note |

|---|

| J13 | Intel MAX 10 via FTDI | IN | JTAG | | J5 | Intel Cyclone V via FTDI | - | UART |

|

Reference Designs

| Page properties |

|---|

|

In this Section you must refer to the Reference Design (Test board) for the particular module. For Example: TE0728 Reference Designs |

...