...

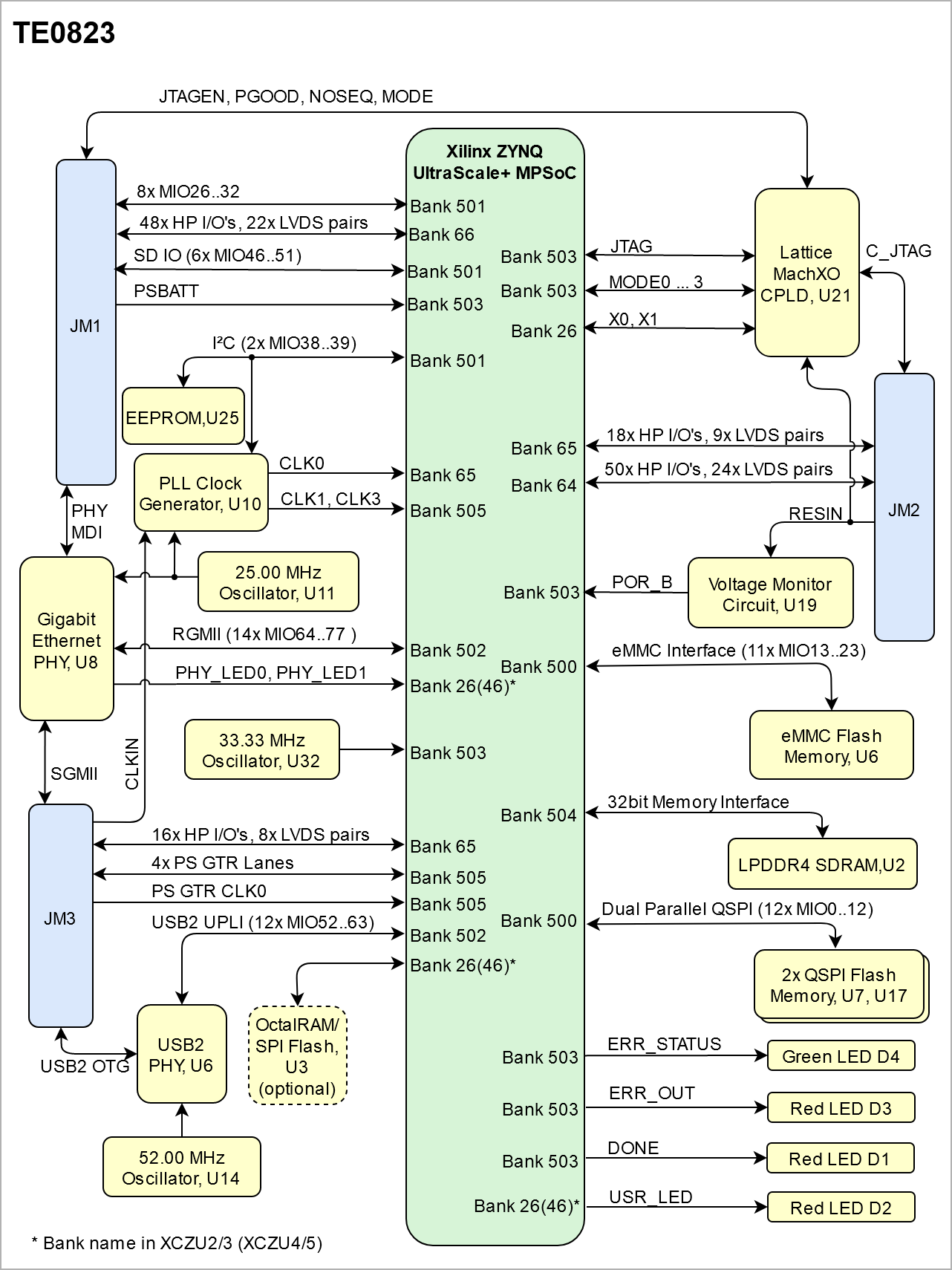

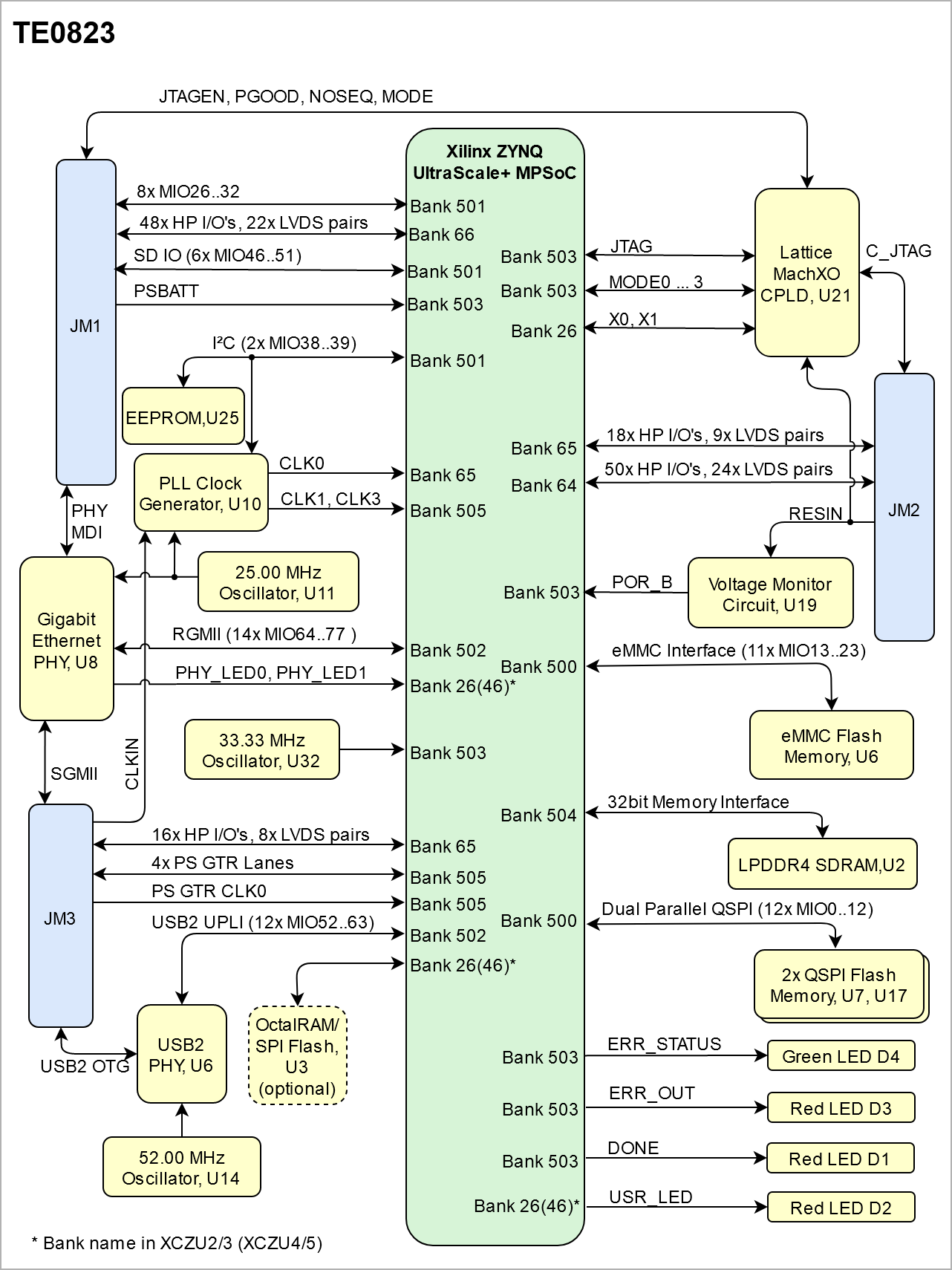

The Trenz Electronic TE0823 (3PIU1FA /3PIU1FL) is an industrial-grade MPSoC module integrating a low power Xilinx Zynq UltraScale+ MPSoC, 1 GByte LPDDR4 SDRAM, 128 MByte 8 GB eMMC chip, 2x 64 MB Flash memory for configuration and operation, and powerful switch-mode power supplies for all on-board voltages. A large number of configurable I/O's is provided via rugged high-speed stacking connections.. The module is equipped with a Lattice Mach XO2 CPLD for system controlling. 3x Robust high-speed connectors provide a large number of inputs and outputs.

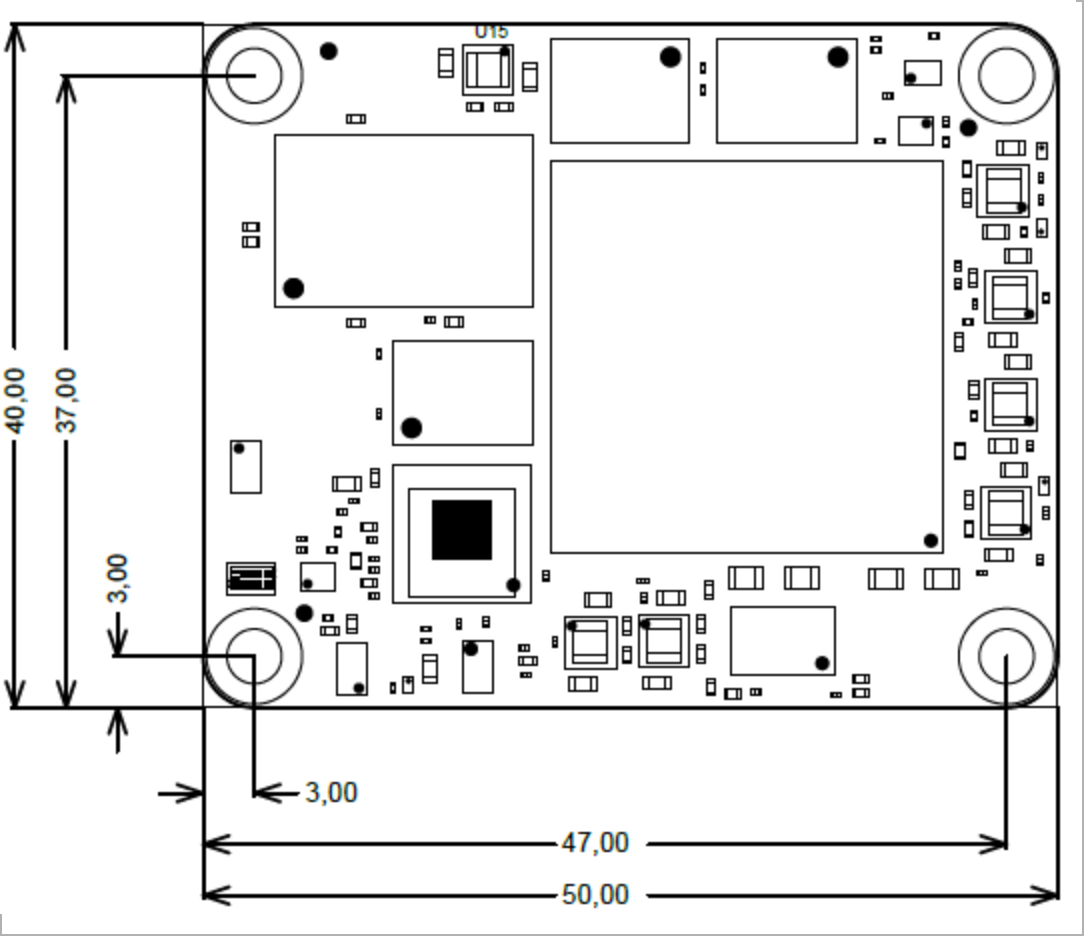

The highly integrated modules are All this on a tiny footprint, smaller than a credit card , at the most competitive price. Modules in and are offered in several variants at an affordable price-performance ratio. Modules with a 4 x 5 cm form factor are fully completely mechanically and largely electrically compatible among with each other.

All parts are at least industrial temperature range. The module operating temperature range depends on customer design and cooling solution. Please contact us for options.

Refer to http://trenz.org/te0823-info for the current online version of this manual and other available documentation.

...

- SoC/FPGA

- Package: SFVC784, SFRC784

- Device: ZU2 ...ZU5, *

- Engine: EG, CG, EV, *

- Speed: -1, -1L, -2, -2L, 3, *, **

- Temperature: I, E, *, **

- RAM/Storage

- 2x DDR4 SDRAM,

- Data Width: 32 Bit

- Size: 16 Gb, *

- Speed: 3733 Mbps, ***

- 2x QSPI boot Flash in dual parallel mode

- Data Width: 8 Bit

- Size: 512 Mb Gb, *

- 1x e.MMC Memory

- Data Width: 8 Bit

- Size: 32 Gb, *

- MAC address serial EEPROM

- On Board

- Lattice MachXO2 CPLD

- Programmable Clock Generator

- Hi-speed USB2 ULPI Transceiver

- 4x LEDS

- Interface

- 1x GB/s serial GMII interface

- 1x Hi-speed USB2 ULPI transceiver with full OTG support

- 154 x High Performance (HP) und 96 x High Density (HD) I/Os

- 78 x PS MIOs

- 4 x serial PS GTR transceivers

- Power

- All power regulators on board

- Dimension

- Note

- * depends on assembly version

- ** also non low power assembly options possible

- *** depends on used U+ Zynq and DDR4 combination

- Rugged for shock and high vibration

BlockDiagram

| Page properties |

|---|

|

add drawIO object here.

|

...

| Scroll Title |

|---|

| anchor | Figure_OV_BD |

|---|

| title | TE0823 block diagram |

|---|

|

| Scroll Ignore |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

| | draw.io Diagram |

|---|

| border | false |

|---|

| |

|---|

| diagramName | TE0823_OV_BD |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| diagramWidth | 641 |

|---|

| revision | 1316 |

|---|

|

|

| Scroll Only |

|---|

|

|

Main Components

...

| Scroll Title |

|---|

| anchor | Table_OV_BP |

|---|

| title | Boot process. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

MODE Signal State | Boot Mode |

|---|

| LowHigh | QSPI* | | HighLow | SD Card* |

*changable also with other CPLD Firmware:TE0823 CPLD |

| Scroll Title |

|---|

| anchor | Table_OV_RST |

|---|

| title | Reset process. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

Signal | B2B | I/O | Note |

|---|

RESIN | JM2-18 | Input |

|

|

...

| Page properties |

|---|

|

Notes : Minimum and Maximum density of DDR3 SDRAM must be mentioned for other assembly options. (pay attention to supported address length for DDR3) |

The TE0821 TE0823 SoM has dual 8 Gb volatile DDR4 a 1 GB volatile LPDDR4 SDRAM IC for storing user application code and data.

- Part number: K4A8G165WB-BIRC IS43LQ32256A

- Supply voltage: voltage: 1.7V ~ 1.2V95V

- Speed: 2400 3200 Mbps

- Temperature: -40 ~ 95 °C

...

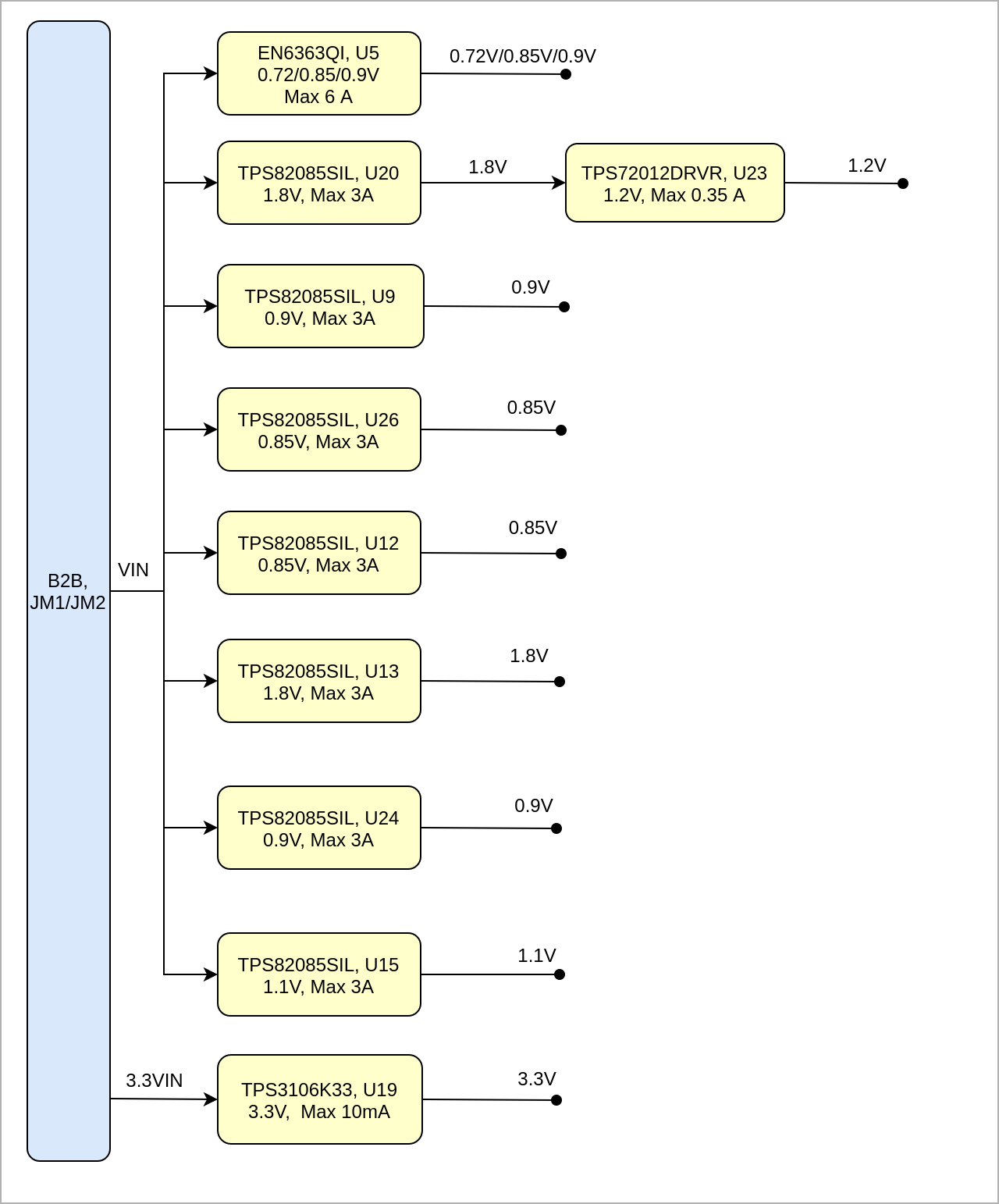

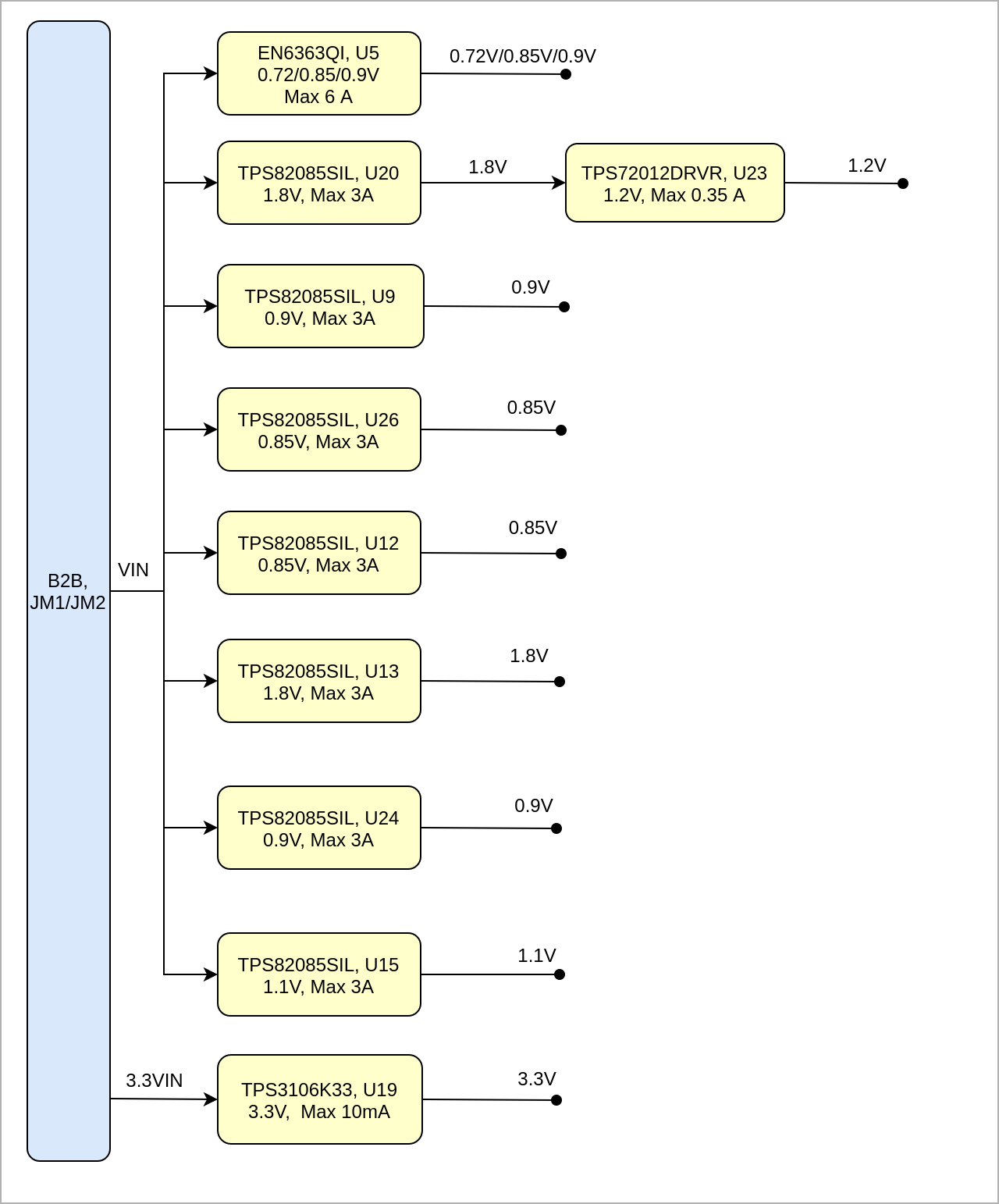

| Scroll Title |

|---|

| anchor | Figure_PWR_PD |

|---|

| title | Power Distribution |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| |

|---|

| diagramName | TE0823_PWR_PD |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| diagramWidth | 640 |

|---|

| revision | 910 |

|---|

|

|

| Scroll Only |

|---|

|

|

Power-On Sequence

...

| Page properties |

|---|

|

- This section is optional and only for modules.

use "include page" macro and link to the general B2B connector page of the module series, For example: 6 x 6 SoM LSHM B2B Connectors

| Include Page |

|---|

| PD:6 x 6 SoM LSHM B2B ConnectorsPD: |

|---|

| 6 x 6 SoM LSHM B2B Connectors |

|---|

|

|

| Include Page |

|---|

| PD:4 x 5 SoM LSHM B2B ConnectorsPD: |

|---|

| 4 x 5 SoM LSHM B2B Connectors |

|---|

|

...

| Scroll Title |

|---|

| anchor | Table_TS_ROC |

|---|

| title | Recommended operating conditions. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Parameter | Min | Max | Units | Reference Document |

|---|

| VIN supply voltage | 3.3 | 6 | V | See TPS82085S datasheet | | 3.3VIN supply voltage | 3.3 | 3.465 | V | See LCMXO2-256HC, Xilinx DS925 datasheet | | PS I/O supply voltage, VCCO_PSIO | 1.710 | 3.465 | V | Xilinx document DS925 | | PS I/O input voltage | –0.20 | VCCO_PSIO + 0.20 | V | Xilinx document DS925 | | HP I/O banks supply voltage, VCCO | 0.950 | 1.9 | V | Xilinx document DS925 | | HP I/O banks input voltage | -0.20 | VCCO + 0.20 | V | Xilinx document DS925 | | Voltage on SC CPLD pins | -0.3 | 3.6 | V | Lattice Semiconductor MachXO2 datasheet | | Operating Temperature Range | 0 | 85 | °C | Xilinx document DS925, extended grade Zynq temperarure range |

|

...

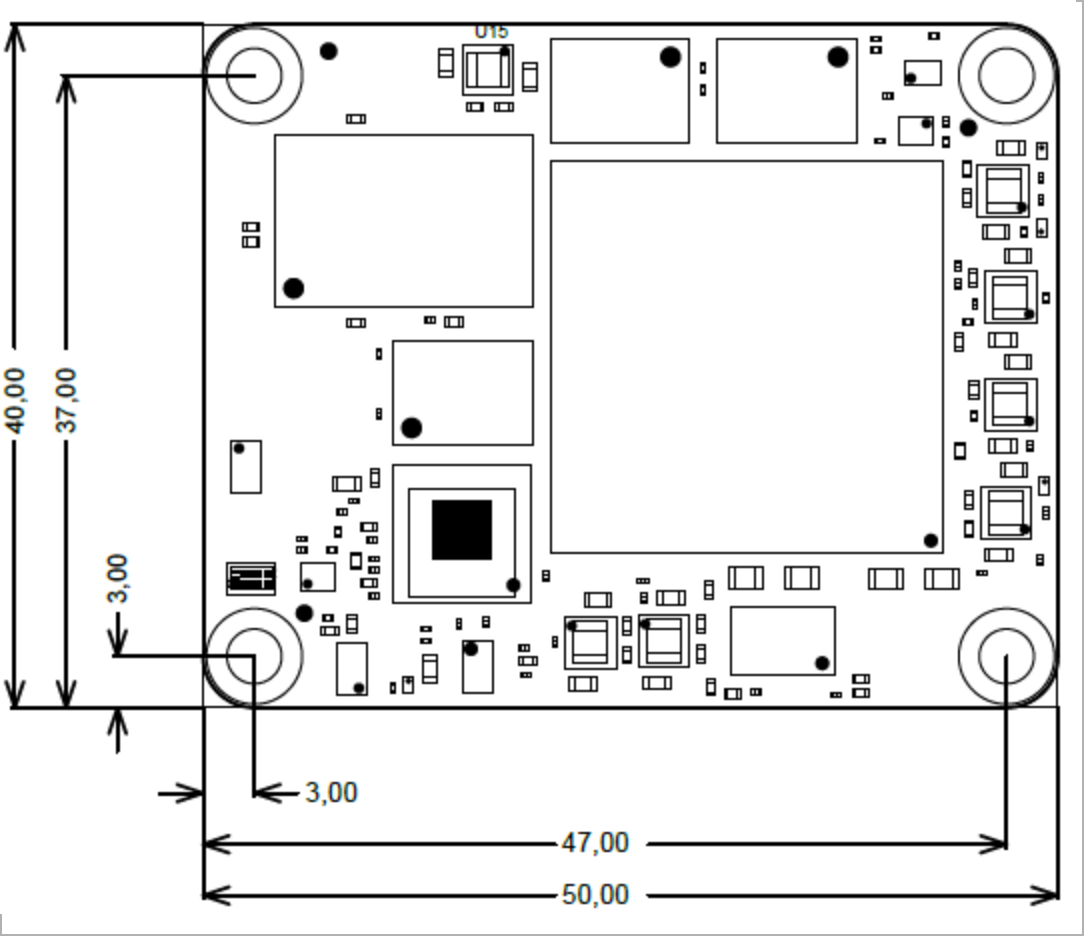

| Scroll Title |

|---|

| anchor | Figure_TS_PD |

|---|

| title | Physical Dimension |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| |

|---|

| diagramName | TE0823_TS_PD |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| diagramWidth | 542 |

|---|

| revision | 34 |

|---|

|

|

| Scroll Only |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

|

|

|

...

| Scroll Title |

|---|

| anchor | Figure_RV_HRN |

|---|

| title | Board hardware revision number. |

|---|

|

| Scroll Ignore |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

| | draw.io Diagram |

|---|

| border | false |

|---|

| |

|---|

| diagramName | TE0823_RV_HRN |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| diagramWidth | 170 |

|---|

| revision | 2 |

|---|

|

|

| Scroll Only |

|---|

|

|

...

| Scroll Title |

|---|

| anchor | Table_RH_DCH |

|---|

| title | Document change history. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Revision | Contributor | Description |

|---|

| Page info |

|---|

| infoType | Modified date |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| type | Flat |

|---|

|

| | Page info |

|---|

| infoType | Current version |

|---|

| prefix | v. |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| | Page info |

|---|

| infoType | Modified by |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| | | 2021-08-23 | v.42 | Pedram Babakhani | | | 2020-11-02 | v.40 | Pedram Babakhani | | -- | all | | Page info |

|---|

| infoType | Modified users |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| |

|

...