Vivado or not Vivado, that might be the question. Xilinx Answer is Vivado of course, as Xilinx has dropped support and development of anything else. So Vivado it is.

So how to make and publish a project that just blinks a LED with Vivado?

Correct answer to this is that it is not possible. You can not publish Vivado projects in such way that they will load and work unless you do some TCL magic.

So here the TCL magic goes:

#

# We need create IPI Block Design and name it, say "top"

#

create_bd_design "top"

#

# Lets make a binary counter with width say 32, clocked from Input port named CLK

#

startgroup

create_bd_cell -type ip -vlnv xilinx.com:ip:c_counter_binary:12.0 my_counter

set_property -dict [list CONFIG.Output_Width {32}] [get_bd_cells my_counter]

create_bd_port -dir I -type clk CLK

connect_bd_net [get_bd_pins /my_counter/CLK] [get_bd_ports CLK]

startgroup

#

# We want to access single bit of the counter and connect it to LED to make it blink

# So we create a "slicer" it has default wifth of 32 that matches our counter width

#

startgroup

create_bd_cell -type ip -vlnv xilinx.com:ip:xlslice:1.0 my_bitselector

endgroup

#

# Now we connect the "bit slicer" to our counter

#

connect_bd_net [get_bd_pins my_bitselector/Din] [get_bd_pins my_counter/Q]

#

# The following is optional, but it makes the 1 bit vector from bit slicer

# to be available as single signal (not as vector), so it is nicer name

# in XDF file to connect to single LED as LED not as LED[0]

# We create a logic function and immediatly set its vector input to 0:0

#

startgroup

create_bd_cell -type ip -vlnv xilinx.com:ip:util_reduced_logic:1.0 my_vector_to_signal

set_property -dict [list CONFIG.C_SIZE {1}] [get_bd_cells my_vector_to_signal]

endgroup

#

# Now we connect it to the output of the slicer that delivers our blinking signal

# As vector of width 1

#

connect_bd_net [get_bd_pins my_vector_to_signal/Op1] [get_bd_pins my_bitselector/Dout]

#

# Now we create a output port named LED and connect it

#

startgroup

create_bd_port -dir O LED

connect_bd_net [get_bd_pins /my_vector_to_signal/Res] [get_bd_ports LED]

endgroup

#

# We are done, lets regenerate the layout

#

regenerate_bd_layout

#

# We are done, LED Blinky design is created, and this TCL magic would

# Recreate the same design on any other PC

# (if the builtin IP core versions used here are available)

#

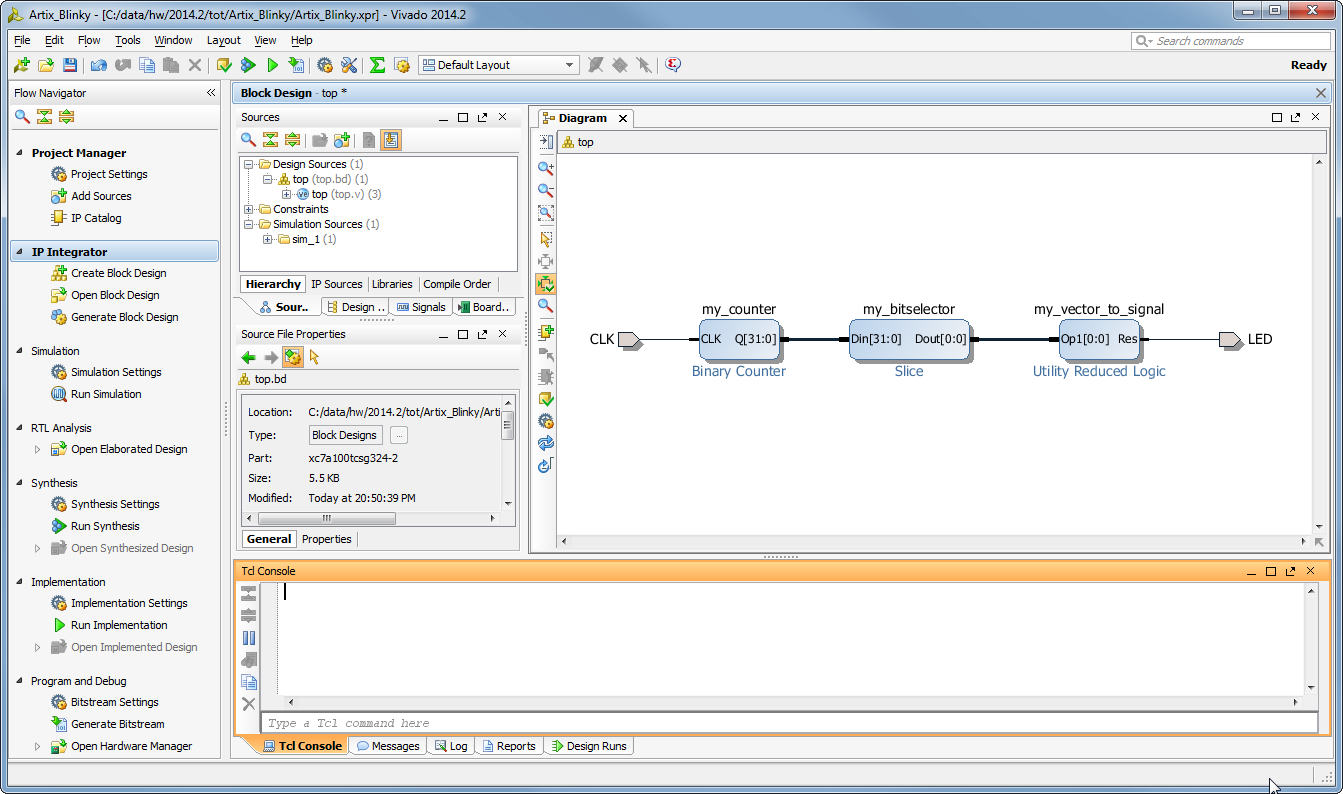

This is what we see after this TCL magic.

Overview

Content Tools