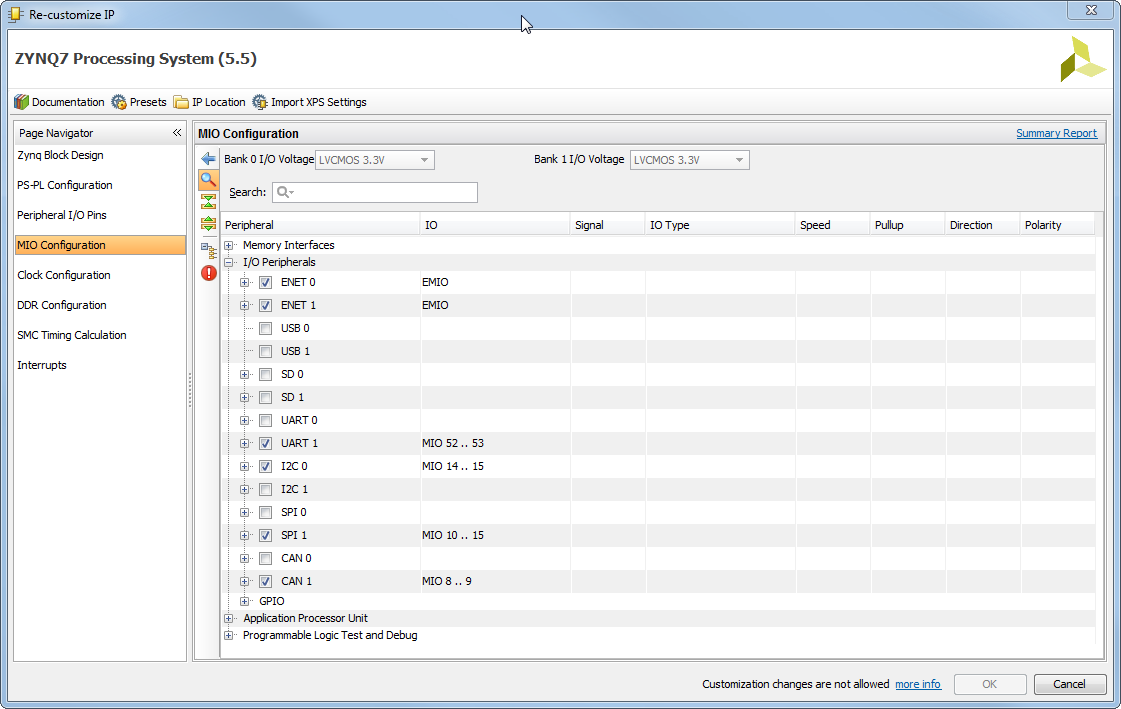

PS Peripherals

| MIO Pin | Mapped to | Pull up/down | Notes |

|---|---|---|---|

| 0 | GPIO | Up | RTC Interrupt |

| 1 | QSPI0 | ||

| 2 | QSPI0 | Down | |

| 3 | QSPI0 | Down | |

| 4 | QSPI0 | Down | Override to up on base for bootmode change |

| 5 | QSPI0 | Up | |

| 6 | QSPI0 | Down | |

| 7 | GPIO | Down | On-board LED |

| 8 | CAN1 TXD | Down | CAN transceiver in SBC |

| 9 | CAN1 RXD | CAN transceiver in SBC | |

| 10 | SPI1 MOSI | SBC SPI Bus | |

| 11 | SPI1 MISO | SBC SPI Bus | |

| 12 | SPI1 SCLK | SBC SPI Bus | |

| 13 | SPI1 SS0 | SBC SPI Bus | |

| 14 | I2C0 SCL | Up | On-board RTC, and EEPROM |

| 15 | I2C0 SDA | Up | On-board RTC, and EEPROM |

Recommended Peripheral mapping for MIO Voltage bank 0.

Mapping of on-board peripherals.

Note: UART must not be on MIO52,53 different mapping is possible.

PL Peripherals

Both Ethernet PHY IC's are connected to PL pins in Bank 34, all PHY IC pins are connected to FPGA pins, there is no sharing of signals for the two PHY's. PHY's must be operated in MII Mode, other modes are not supported. It is possible to use PS ENET0 or ENET1 via EMIO routing or Ethernet IP Cores implemented in PL Fabric.

PS and PL Banks

| Bank | VCCIO | B2B I/O Pins | Notes |

|---|---|---|---|

| 500 | 3.3V | 0 | |

| 501 | USER | 36 | Vref is connected to resistor divider to support HSTL18 |

| 13 | USER | 48 | Differential routing |

| 33 | 3.3V | 33 | Single ended routing |

| 34 | 3.3V | 0 | Ethernet PHY's |

| 35 | 3.3V | 42 | Single ended routing |

Clock sources

| Designator | Description | Frequency | Used as |

|---|---|---|---|

| U14 | MEMS Oscillator | 33.3333MHz | PS_CLK |

| U5 | MEMS Oscillator | 25MHz | Ethernet PHY Clock |

| U7 | RTC | 32.768KHz | Used by RTC, CLKOUT of RTC not connected |

LED's

| Designator | Color | Connected to | Active Level | IO Standard |

|---|---|---|---|---|

| D9 | Green | DONE | Low | not applicable |

| D8 | RED | MIO7 | High | not applicable |

| D4 | Green | PL pin V18 | High | LVCMOS33 |

XADC Usage

| Connected to | Notes | |

|---|---|---|

| VP_0/VP_0 | SBC MUX_OUT | |

| AD0 | B2B | |

| AD1 | B2B | |

| AD3 | B2B | |

| AD4 | B2B | |

| AD5 | B2B | |

| AD7 | B2B | Only singled ended use, N input is GND |

| AD8 | B2B | |

| AD9 | B2B | |

| AD10 | B2B | |

| AD12 | B2B | |

| AD13 | B2B | |

| AD14 | B2B | |

| AD15 | B2B |

XADC is used with internal reference option.

Note the XADC capable pins are not routed differentially to the B2B connector. The performance and usability of the XADC must be evaluated.

SBC

SBC - System Basis Chip MC33908

| SBC Name | Connected | Notes |

|---|---|---|

| VDDIO | 3.3V | I/O Voltage fix 3.3V |

| VCCA | B2B | Not used on board, external PNP Transistor not used, max 100mA |

| VAUX | - | Not connected, not used |

| SELECT | 5K1 to VPRE | Select 3.3V for VCCA Supply |

| MUX_OUT | XADC | |

| CAN RXD | MIO9 | |

| CAN TXD | MIO8 | |

| LIN RXD | PL Y14 | |

| LIN TXD | PL AA14 | |

| MOSI | MIO10 | |

| MISO | MIO11 | |

| SCK | MIO12 | |

| NCS | MIO13 | |

| DEBUG | B2B | 11K Pull-down on module, defaults to debug mode DISABLED |

| IO_0 | B2B | |

| IO_1 | B2B | |

| IO_2 | B2B | |

| IO_3 | B2B | |

| IO_4 | B2B | |

| IO_5 | B2B | |

| INTB | B2B | |

| FS0B | B2B | |

| RSTB | B2B | Also forces system Reset |

| CANH | B2B | 120R terminator on board |

| CANL | B2B | |

| LIN | B2B |

Note: the availability LIN depends on the Module version and assembly option.